目录

页表导论

Linux 页表

PGD(Page Global Directory)

P4D(Page 4th Directory)

PUD(Page Upper Directory)

PMD(Page Middle Directory)

PTE(Page Table Entry)

PGPROT(Page Table Attribute)

ARCHITECTURE

Intel® X86 架构页表

Intel® 32-Bit Paging Mode

Intel® 4-Level Paging Mode

Intel® 5-Level Paging Mode

Intel® PAT Mechanism

Intel® MTRRS Mechanism

Intel® Protection-Key Technology

ARM 架构页表(规划中)

RISCV 架构页表(规划中)

Page Table Attribute

PAGE_PRESENT

PAGE_USR

PAGE_RW

PAGE_ACCESSED

PAGE_DIRTY

PAGE_SOFT_DIRTY

PAGE_GLOBAL

PAGE_PAT/PAGE_PCD/PAGE_PWT

PAGE_PK

PAGE_NX

PAGE_UFFD_WP

PAGE_UFFD_TEST

PAGE_PSE

PAGE_SPECIAL

Linux Page Table 应用

用户进程与页表属性

内核线程与页表属性

页表查询

ATPR(Apply To Page Range) Mechanism

FOLLOW USERSPACE PGTable(FUPT) Mechanism

PageWalk Mechanism

LOOKUP-ADDRESS(LKAD) Mechanism

Copy-Page-Range(CPR) Technology

CPA(Change Page Attribute) Mechanism

User Maps Specific Physical Area(UMSPA)

PageFault 建立页表

PROC Interface

Clear Reference Mechanism

SMAPS Mechanism

Pagemap Mechanism

PTDUMP(PageTable Dump) Mechanism

FOLLOW-Page Technology

Page Table Tools

使用内存流动工具调试缺页

PTDUMP DEBUGFS TOOLS

pmap

ptexplore

Page Table 进阶研究

ZERO PAGE 机制

ZERO COPY 机制

COPY USER with SMEP/SMAP 机制

ENC 内存加密机制

CONFIG_HIGHPTE 机制

PTI(Page Table Isolation) Mechanism

PAGETABLE ENTRY BAD

CONFIG_PAGE_TABLE_ISOLATION

ALLOC PAGETABLE TRACK

PTRACE

change_protection_range

PROTNONE 与 NUMA Balancing

页表导论

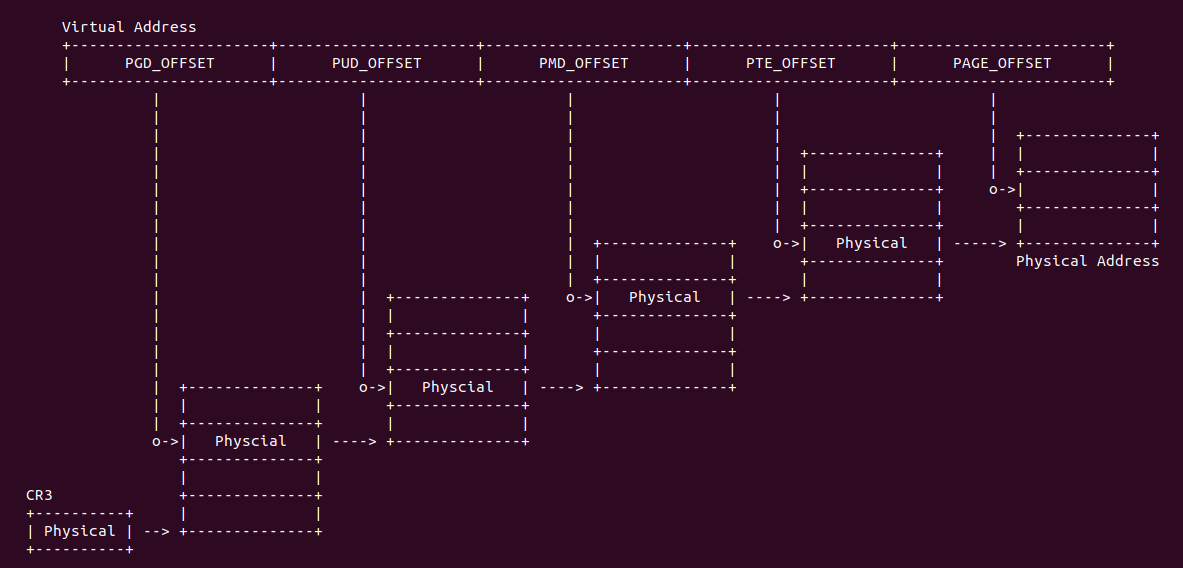

当开启保护模式之后,系统使用的地址从物理地址变成了虚拟地址,但虚拟内存是抽象出来的概念,并不是实际的存储介质,那么当系统访问虚拟内存时,MMU 通过分页机制透明的将虚拟地址自动转换成物理地址,进而访问物理内存。页表是一块长度为 PAGE_SIZE 的物理内存, 其被分割为指定长度的 Entry,Entry 内记录了下一级页表的物理地址或者物理页的物理地址。MMU 将虚拟地址划分为多个区域,在不同的架构中每个区域的含义不同。MMU 在转换虚拟地址之前需要建立页表,页表可以通过缺页被动创建,也可以主动创建。在不同的架构中页表的组成有所不同,但其目的都是将虚拟地址通过分层查表的方式找到下一级页表,最终找到最终的物理地址。

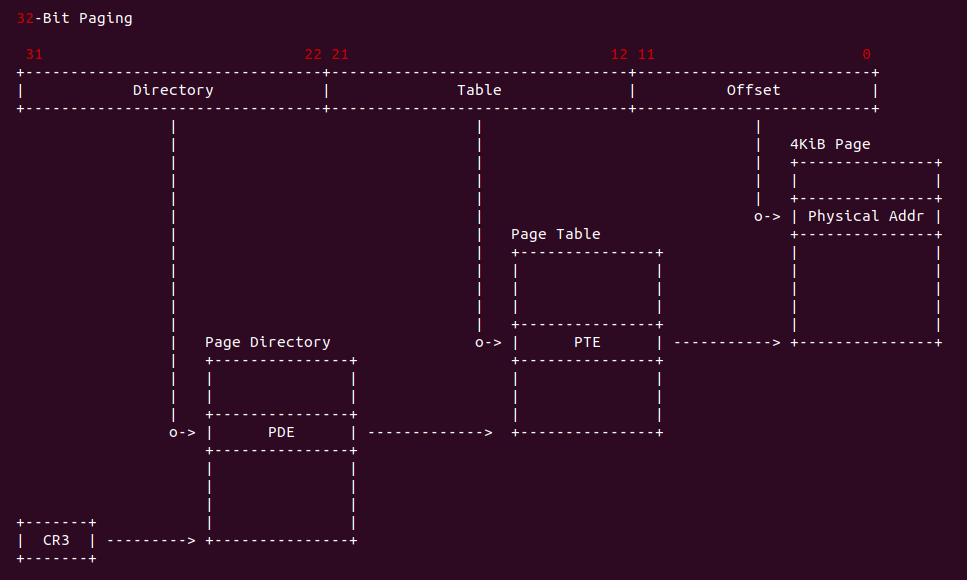

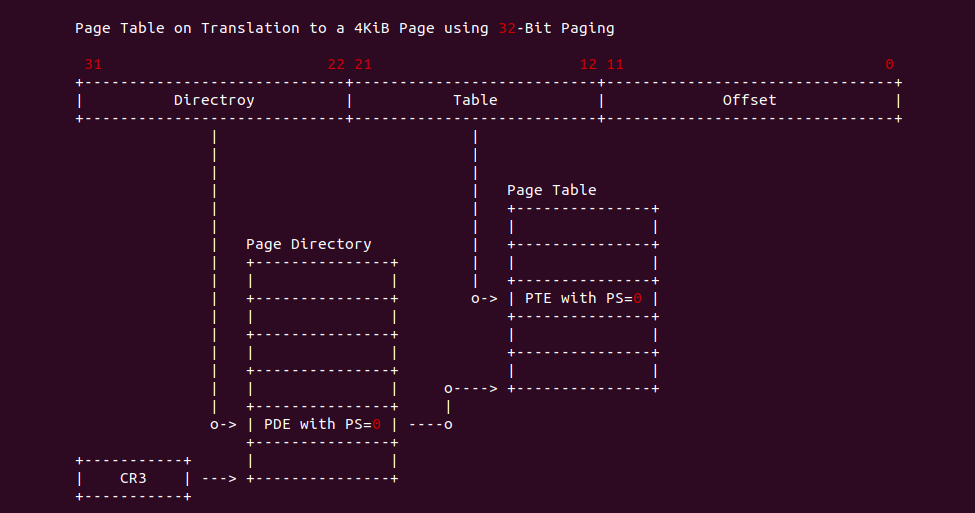

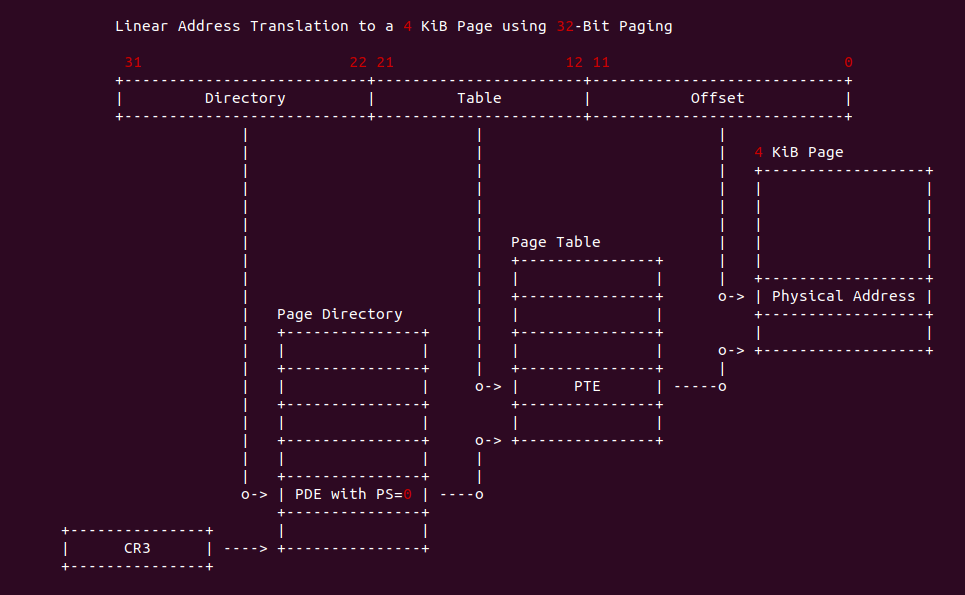

不同的架构地址总线数量不同,因此可寻址范围的不同导致页表的级数不同。在 IA32 架构中使用 32 位的地址总线寻址,因此使用两级页表的 32-Bit 分页机制。该机制中存在两种页表: 页目录页表(Page Directory Table) 和页表(Page Table), 并且使用 CR3 寄存器指向 Page Directory 页表的物理地址. 虚拟地址 [31, 22] 域称为页目录索引,用于在 Page Directory 页表中索引 PDE(Page Directory Entry), PDE 记录了下一级页表 Page Table 的物理地址。虚拟地址 [21, 12] 域称为页表索引, 用于在 Page Table 页表中索引 PTE(Page Table Entry), PTE 记录了物理页的物理地址。虚拟地址 [11, 0] 域称为页内偏移 PAGE_OFFSET,用于在物理页内找到对应的物理地址.

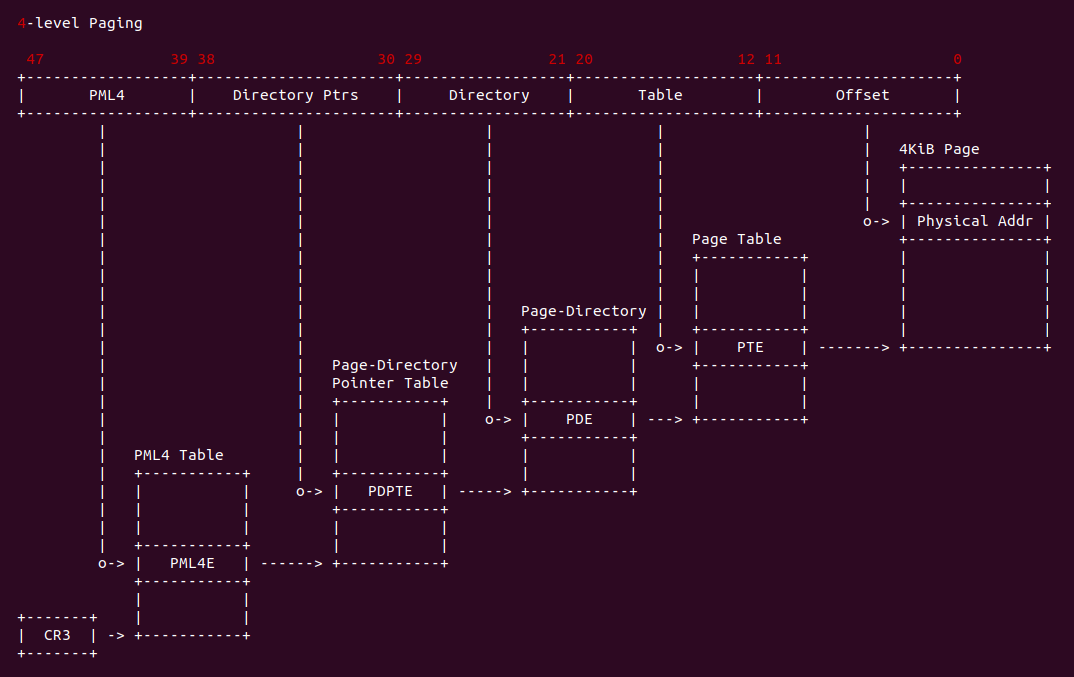

在实现 48 位寻址的 AMD64/X64 架构中,使用 4-level 分页机制,该机制中存在四种页表: PML4 页表、页目录指针页表(Page-Directory Pointer Table)、页目录页表(Page-Directory Table) 和页表(Page Table), 并使用 CR3 寄存器指向 PML4 页表的物理地址。虚拟地址 [47, 39] 域称为 PML4 索引,用于在 PML4 页表中获得 PML4E(PML4 Entry), PML4E 用于记录下一级 Page-Directory Pointer 页表的物理地址。虚拟地址 [38, 30] 域称为页目录指针索引, 用于在 Page-Directory Pointer 页表中索引 PDPTE(Page-Directory Pointer Table Entry), PDPTE 记录了下一级 Page-Directory 页表 的物理地址。虚拟地址 [29, 21] 域称为页目录索>引,用于在 Page-Directory 页表中索引 PDE(Page Directory Entry), PDE 记录了下一 Page Table 页表物理地址。虚拟地址 [20, 12] 域称为页表索引,用于在 Page Table 页表中索引 PTE(Page Table Entry), PTE 记录了物理页的物理地址。虚拟地址 [11, 0] 域称为页内偏移,用于在物理页内索引物理地址.

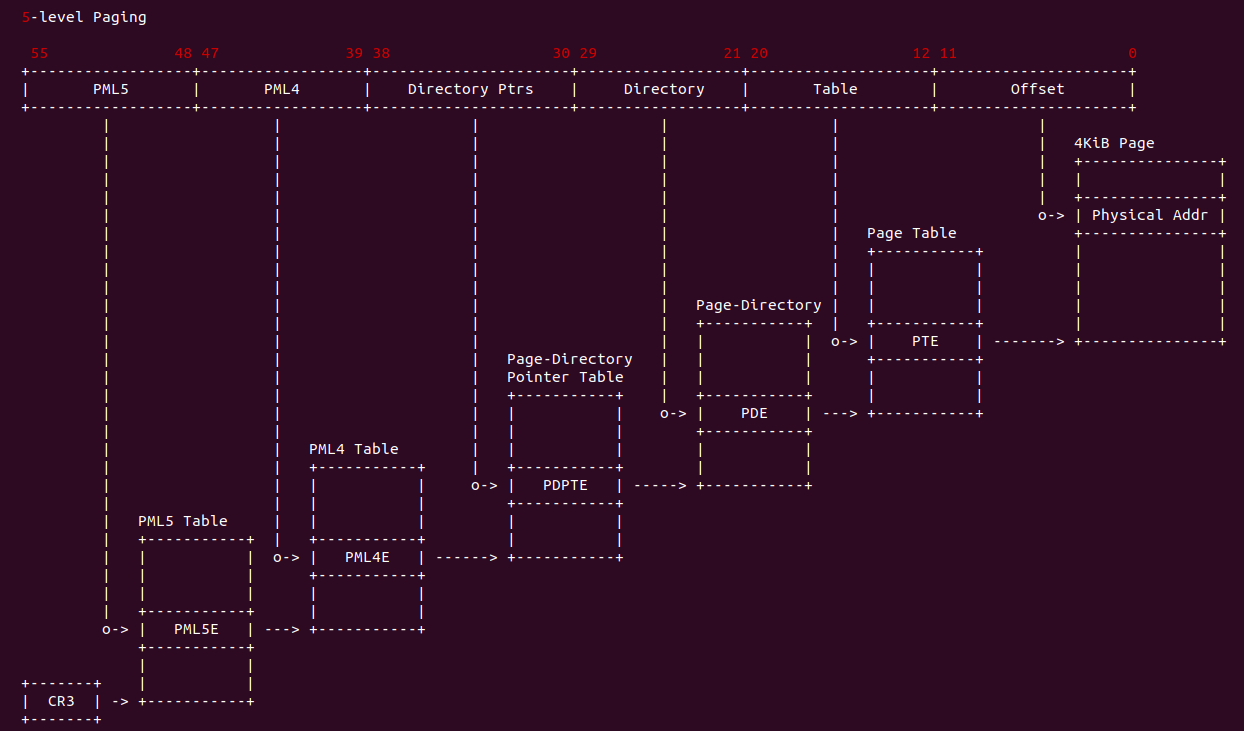

在实现 56 位寻址的 AMD64/X64 架构中,使用 5-level 分页机制,该机制中存在四种页表: PML5 页表、PML4 页表、页目录指针页表(Page-Directory Pointer Table)、页目录页表(Page-Directory Table) 和页表(Page Table), 并使用 CR3 寄存器指向 PML5 页表的物理地址。虚拟地址 [55, 48] 域称为 PML5 索引,用于在 PML5 页表中获得 PML5E(PML5 Entry), PML5E 记录了下一级页表 PML4 的物理地址。虚拟地址 [47, 39] 域称为 PML4 索引,用于在 PML4 页表中获得 PML4E(PML4 Entry), PML4E 记录下一级 Page-Directory Pointer 页表的物理地址。虚拟地址 [38, 30] 域称为页目录指针索引, 用于在 Page-Directory Pointer 页表中索引 PDPTE(Page-Directory Pointer Table Entry), PDPTE 记录了下一级页表 Page-Directory 的物理地址。虚拟地址 [29, 21] 域称为页目录索引,用于在 Page-Directory 页表中索引 PDE(Page Directory Entry), PDE 记录了下一页表 Page Table 物理地址。虚拟地址 [20, 12] 域称为页表索引,用于在 Page Table 页表中索引 PTE(Page Table Entry), PTE 记录了物理页的物理地址。虚拟地址 [11, 0] 域称为页内偏移,用于在物理页内索引物理地址.

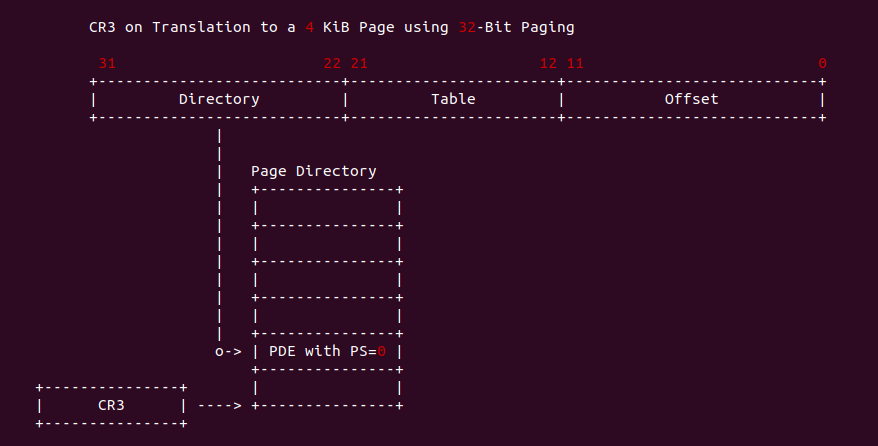

页表遍历

MMU 通过遍历页表将一个虚拟地址转换成物理地址。例如在 X86 架构中使用 32-Bit 分页机制,系统使用 CR3 寄存器存储 Page Table 页表的起始物理地址,然后将虚拟地址 VA 向右偏移 22 位之后获得了虚拟地址的 Directory 区域, 结合 Page Directory 就可以获得对应的 PDE, 此时 PDE 内记录了 Page Table 页表的起始物理地址。

在获得 PDE 之后,将虚拟地址 VA 向右偏移 12 位并屏蔽 Directory 区域之后获得了虚拟地址的 Table 区域,结合 Page Table 既可以获得对应的 PTE,此时 PTE 内记录了物理页的起始物理地址.

在获得 PTE 之后,将虚拟地址 VA 的低 PAGE_SHIFT 位区域隔离出来就可以获得 Offset 区域,结合物理页的起始物理地址,就可以在物理页内找到一个物理地址,此地址就是虚拟地址映射的物理地址.

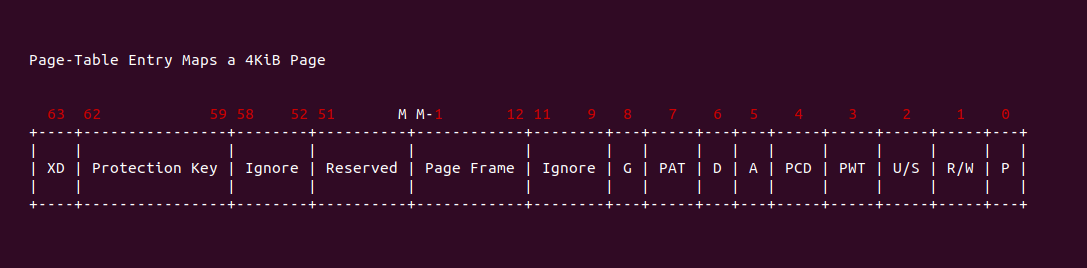

页表权限访问控制

MMU 的主要功能是访问权限控制,MMU 通过页表内记录的权限信息确定虚拟内存是否对物理地址空间有访问权限。当 CPU 访问虚拟地址时,MMU 硬件会自动(透明)查询页表,并检查页表的内容以此确定 CPU 是否对物理地址空间有权限访问. 上图是典型的 PTE 页表结构,每个区域都控制不同的访问权限,例如:

- P: Present 标志位,指示页表是否存在,如果清零表示映射的物理区域不在内存,可能被放置到 SWAP 空间; 如果置位表示页表映射的物理区域存在内存里.

- R/W: 读写标志位, 该标志置位表示虚拟内存可读可写; 反之标志位清零表示虚拟内存只读.

- U/S: 用户空间标识,该标志位置位时表示只允许用户空间进程访问虚拟内存; 反之清零表示只允许内核空间线程访问虚拟内存.

- PWT/PCD/PAT: Memory Type 标记集合,三个标志共同确认虚拟内存映射类型,比如 UC/WB/WC/WT

- A: 访问标志位,该标志置位时表示映射的物理区域被访问过; 反之清零表示映射的物理区域没有被访问过

- D: 脏标志位, 该标志位置位时表示映射的物理区域被写入过; 反之清零表示映射的物理区域没有被写入过

- G: 全局标志位,该标志位置位表示映射对所有的地址空间可见; 反之清零表示只对私有的地址空间可见

- Page Frame: 页帧字段,表示虚拟内存映射的物理区域的页帧号

- Protection Key: 页权限控制位

- XD: 禁止执行标志位,该标志位置位表示映射的虚拟区域不具有执行权限; 反之清理表示映射区域有执行权限

MMU 就是通过页表里不同的权限位来控制虚拟内存的方式,以此实现有的虚拟内存可读可写,有的内存只读,或者有的虚拟内存可执行. 每一级页表都具有三个区域: Page Frame、Access 域和 Atrribute 域. Page Frame 用于指向下一级页表或者最终物理区域的页帧号,Access 域表明下一级页表或者最终物理区域的访问权限,而 Atrribute 域则是下一级页表或者最终物理区域的映射属性. 不同级的页表之间页存在一定的差异,但基本保持上诉三个区域.