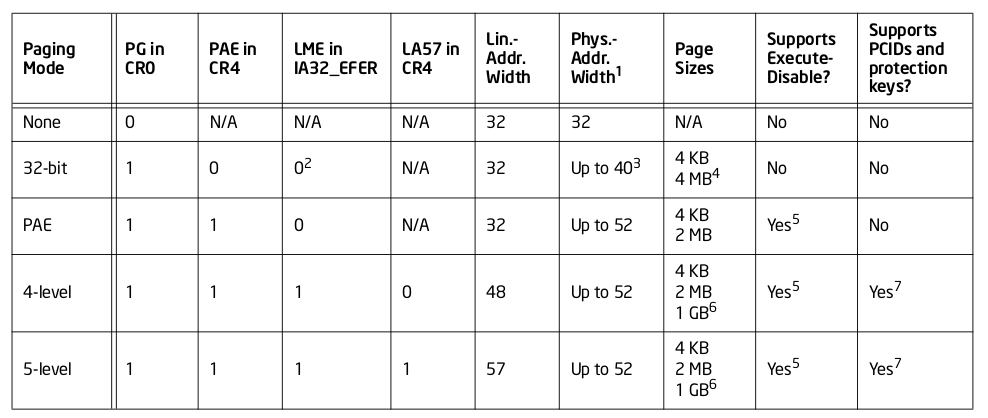

在 Intel® X86 和 IA-32 处理器上硬件支持: 32-Bit 分页模式、PAE 分页模式、4-level 分页模式 和 5-level 分页模式. 由于不同的处理器其支持的线性地址空间和物理地址空间范围不同,因此采用不同的分页模式导致系统能访问的空间存在差异. 另外不同的分页机制导致硬件上支持不同尺寸的物理页,例如 4KiB、2MiB、4MiB 和 1Gig 物理页.

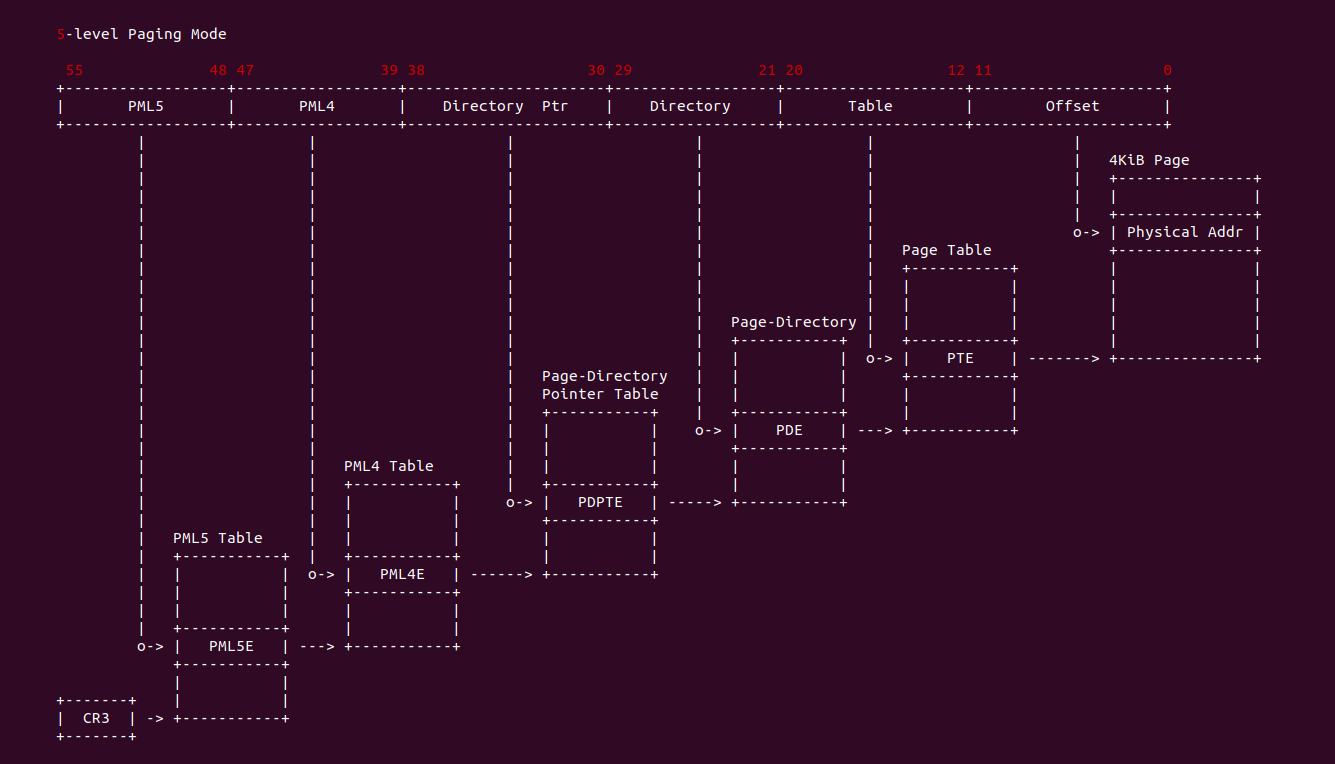

不同的分页模式的线性地址空间和物理地址空间位宽均不同,32-Bit 分页模式 支持 32 位的线性地址空间和高达 40 位物理地址空间,并且支持 4KiB 和 4MiB 两种尺寸的物理页; PAE 分页模式 支持 32 位的线性地址空间和高达 52 位的物理地址空间,并且支持 4KiB 和 2MiB 两种尺寸的物理页; 4-level 分页模式 支持 48 位线性地址和高达 52 位的物理地址空间,并且支持 4KiB、2MiB 和 1Gig 三种尺寸的物理页; 5-level 分页模式 支持 57 位的线性地址空间和高达 52 位的物理地址空间,并且支持 4KiB、2MiB 和 1Gig 三种尺寸的物理页。

Intel® 分页模式控制位

X86 架构下,同一个硬件可以支持多种分页模式,分页模式的控制通过多个寄存器的标志位进行控制,可以通过配置这些控制寄存器实现分页模式的启用和切换等,具体如下:

- CR0.WP 写保护标志位: 当置位时,禁止特权级程序向只读页面写入; 当清零时,允许特权级程序写入只读页面(不考虑U/S位设置). 该标志有助于实现像 UNIX 等操作系统使用的创建新进程(forking)的写时复制方法。在软件设置 CR4.CET 之前,必须设置此标志,且只要 “CR4.CET = 1”,则不能清除它.

- CR0.PG 分页标志位: 当置位时,启用分页; 当清零时,禁用分页。当分页被禁用时,所有线性地址被视为物理地址。如果 CR0.PE 标志没有置位,CR0.PG 标志不会起作用; 在 CR0.PE 标志为清零状态下置位 CR0.PG 标志会导致通用保护异常(#GP)

- IA32_EFER.LME 标志位: 使能 IA-32e 模式. 当置位时支持 IA-32e 模式(由于现在的 X86 架构不是真正的 64 位物理地址空间,因此需要使能该标志位); 当清零时不支持 IA-32e 模式.

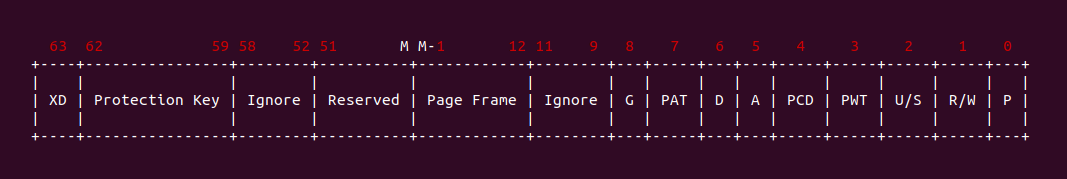

- IA32_EFER.NXE 标志位: 可执行禁止(Execute Disable Bit) 使能位. 当置位时页表支持 NX 标志位; 当清零时页表不支持 NX 标志位.

- CR4.PSE 页大小扩展标志位: 当置位时启用 32-Bit 分页模式的 4MiB 物理页; 当清除时,将 32-Bit 分页模式限制为 4KiB 大小的物理页.

- CR4.PAE 物理地址扩展标志位: 当置位时启用分页以产生超过 32 位的物理地址; 当清除时, 将物理地址限制为 32 位。在进入 IA-32e 模式之前需要设置 CR4.PAE 标志位

- CR4.PGE 全局页标志位: 当置位时,启用全局页面功能; 当清零时,禁用全局页面功能。全局页面功能允许将经常使用或共享的页面标记为对所有用户都是全局的(使用页目录指针表项、页目录项或页表项中的全局标志)。全局页面不会在任务切换或写入CR3寄存器时从 TLB 中刷新。在启用全局页面功能之前,必须先启用分页, 颠倒这个顺序可能会影响程序的正确性,并且会影响处理器的性能。

- CR4.LA57 57 位线性地址标志位: 在 IA-32e 模式下,当置位时,处理器使用 5 级分页来转换 57 位线性地址; 当在 IA-32e 模式下清零时,处理器使用 4 级分页来转换 48 位线性地址。在 IA-32e 模式下,此位不能被修改。

- CR4.PCIDE PCID 使能标志位: 当置位时,启用进程上下文标识符(PCID)。仅适用于 IA-32e 模式

- CR4.SMEP SMEP 使能标志位: 当置位时,启用特权级别执行预防,用于防止用户空间和内核空间越权访问

- CR4.SMAP SMAP 使能标志位: 当置位时,启用特权级别执行预防,用于防止用户空间和内核空间越权访问

- CR4.PKE Protection Keys 使能位: 4 级分页和 5 级分页将每个用户模式线性地址与一个保护键关联。当置位时,此标志通过 “CPUID.(EAX=07H,ECX=0H):ECX.OSPKE” 表明操作系统支持使用 PKRU 寄存器来指定每个保护键的用户模式线性地址是否可以读取或写入。此位还通过使用 RDPKRU 和 WRPKRU 指令来启用对 PKRU 寄存器的访问

- CR4.CET 控制流执行技术标志位: 当置位时,启用控制流执行技术。此标志只能在设置 CR0.WP 后设置,且必须在清除CR0.WP 之前清除

- CR4.PKS 启用特权级别页面的保护键: 4 级分页和 5 级分页将每个特权级别线性地址与一个保护键关联。当置位时,此标志允许使用 IA32_PKRS MSR 来指定每个保护键的特权级别线性地址是否可以读取或写入。

- EFLAGS.AC 对齐检查/访问控制标志: 如果在 CR0.AM 位置位,仅当 EFLAGS.AC 为 1 时,才启用用户模式数据访问的对齐检查。当引用未对齐的操作数时,例如奇数字节地址上的字,或者不是四的整数倍地址上的双字,将会生成对齐检查异常。对齐检查异常仅在用户模式(特权级别 3)下生成。默认特权级别为 0 的内存引用,例如段描述符加载,在用户模式下执行的指令不会生成此异常。对齐检查异常可用于检查数据的对齐。这在与要求所有数据对齐的处理器交换数据时非常有用。对齐检查异常还可用于通过使指针不对齐将一些指针标记为特殊指针。这样可以避免检查每个指针的开销,并且仅在使用特殊指针时处理它。如果在 CR4.SMAP 置位,且当 EFLAGS.AC 为 1 时,才允许对用户模式页面进行明确的特权级别数据访问.

软件通过使用 MOV 到 CR0 指令设置 CR0.PG 来启用分页。在执行此操作之前,软件应确保控制寄存器 CR3 包含处理器用于线性地址转换的第一个分页结构的物理地址,并且该结构已按需进行初始化。CR0.PG、CR4.PAE、CR4.LA57 和 IA32_EFER.LME 的值如何确定是否启用分页,以及如果启用分页,则使用四种分页模式中的哪一种.