目录

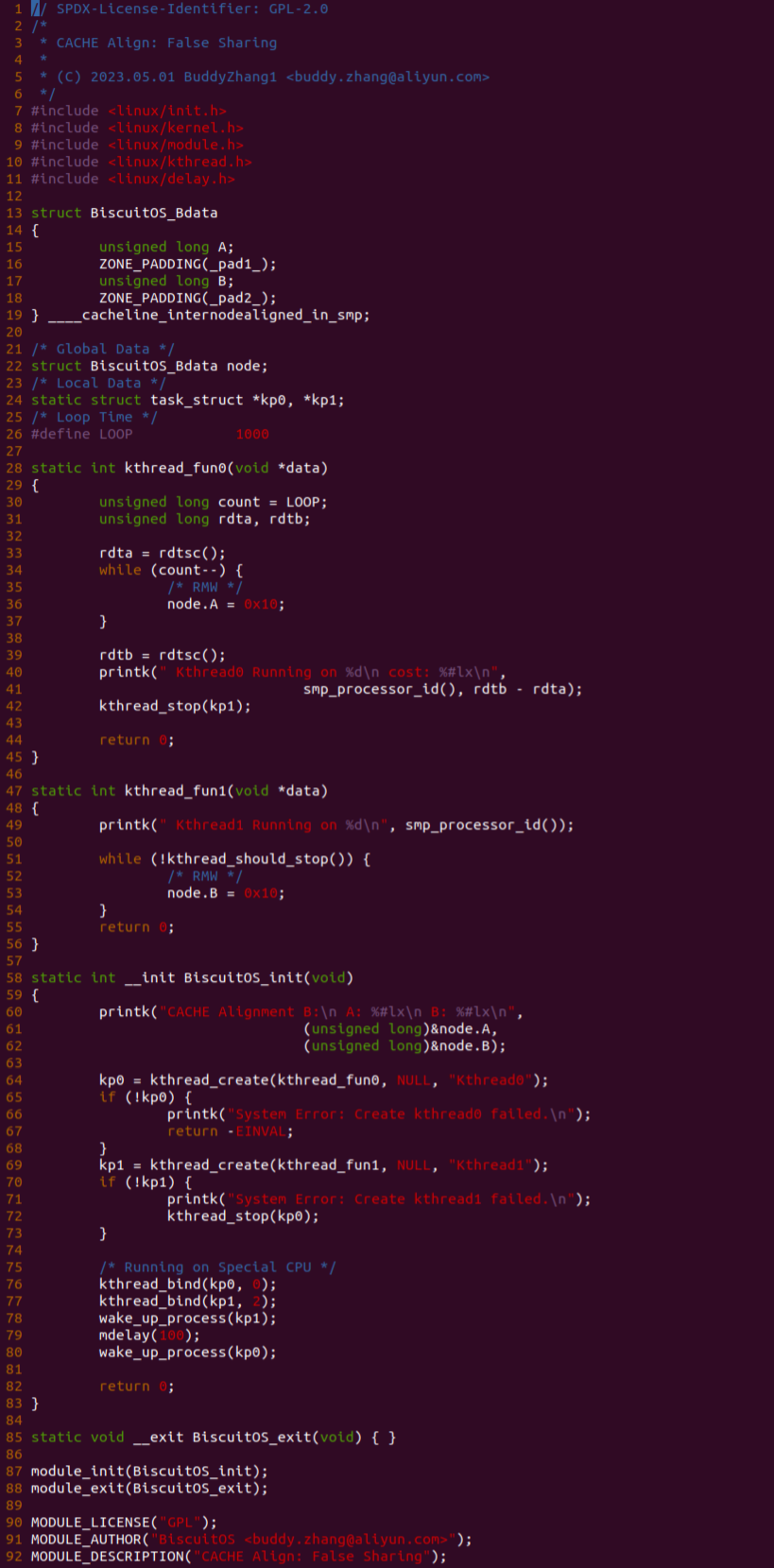

Intel® X86 ™Processors 架构 CACHE 机制

ARM 架构 CACHE 机制(弃用)

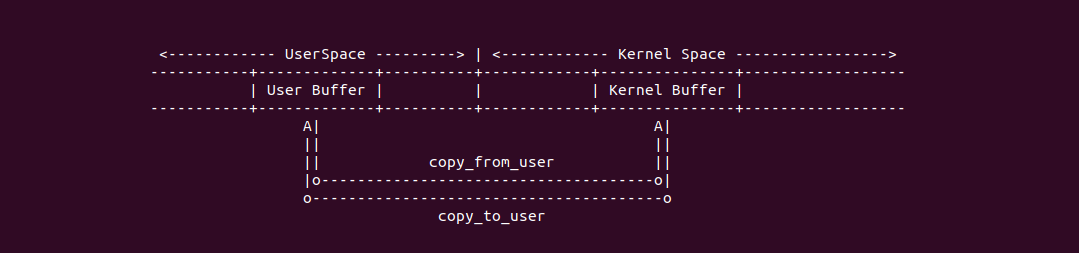

Linux CACHE 机制

CACHE 实践教程

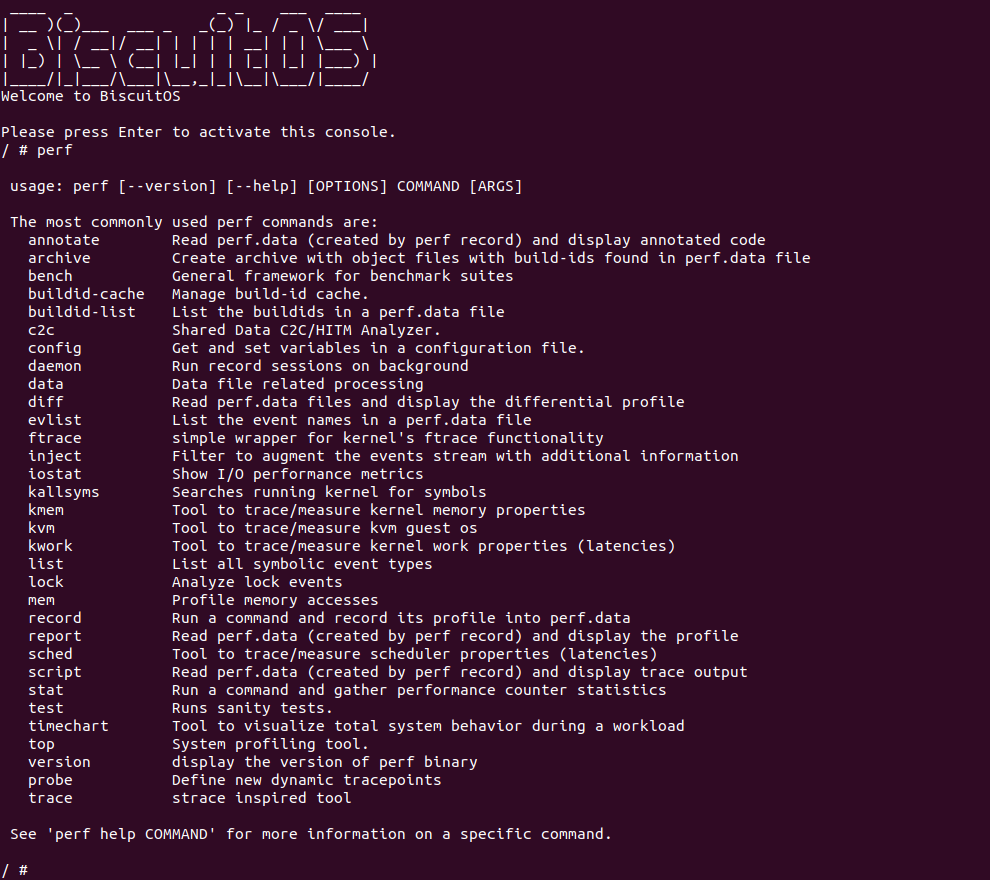

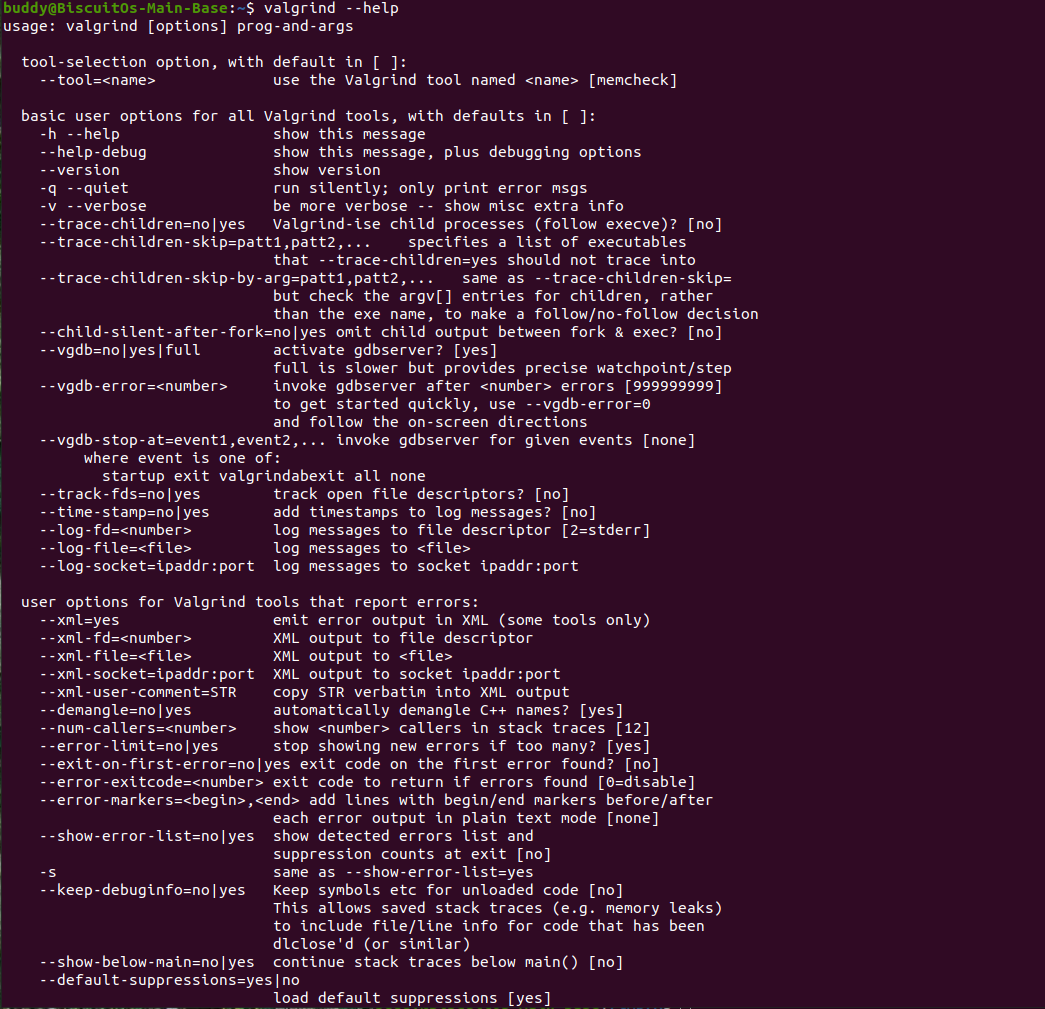

CACHE 调试工具合集

OProfile: Performance System profiler

CACHE BUG/Fault

Spectre: CVE-2017-5753/CVE-2017-5715

Meltdown: CVE-2017-5754

CACHE 进阶研究

CACHE 与 TLB 研究(Updating)

CACHE 与 Combine Write Buffer(Updating)

CACHE 与 Store Buffer(Updating)

CACHE 与 Memory Barrier(Updating)

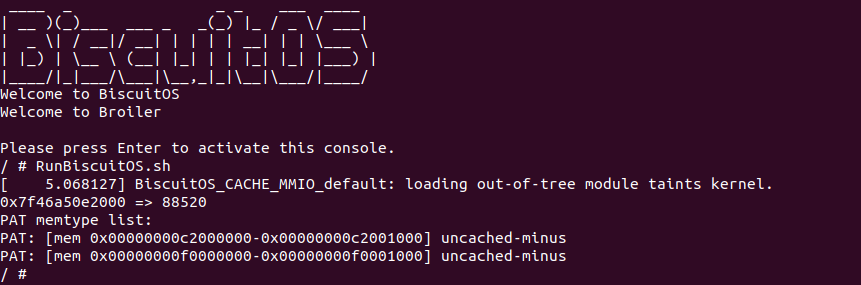

初识 CACHE

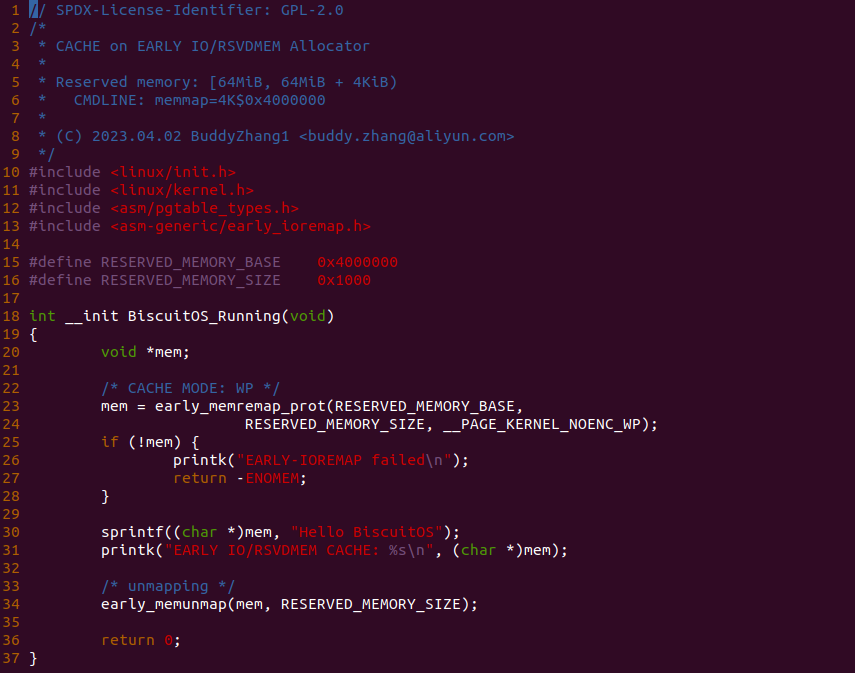

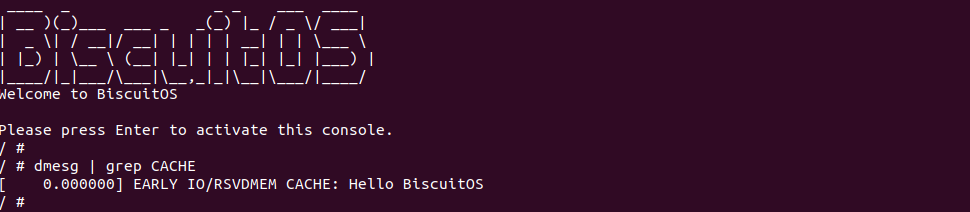

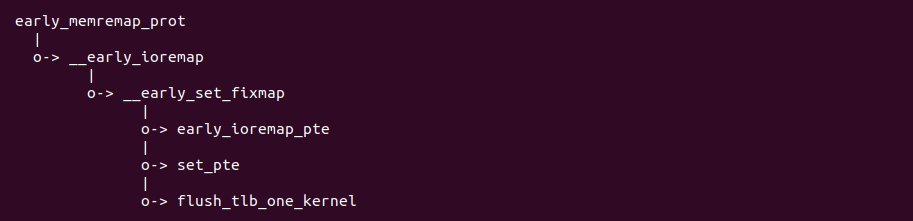

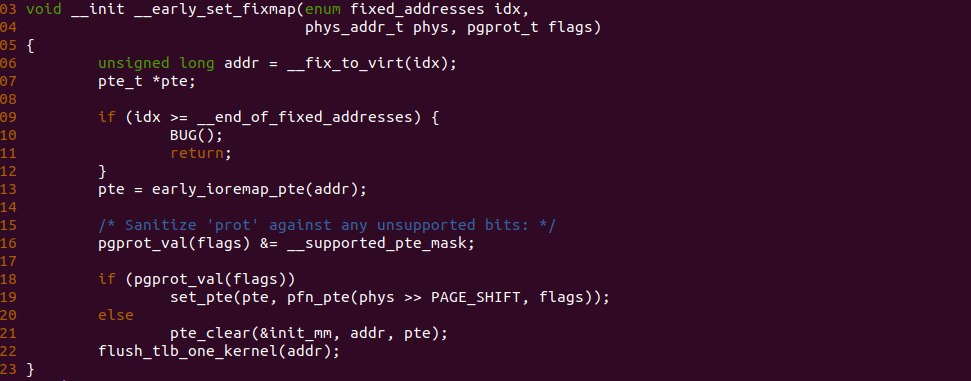

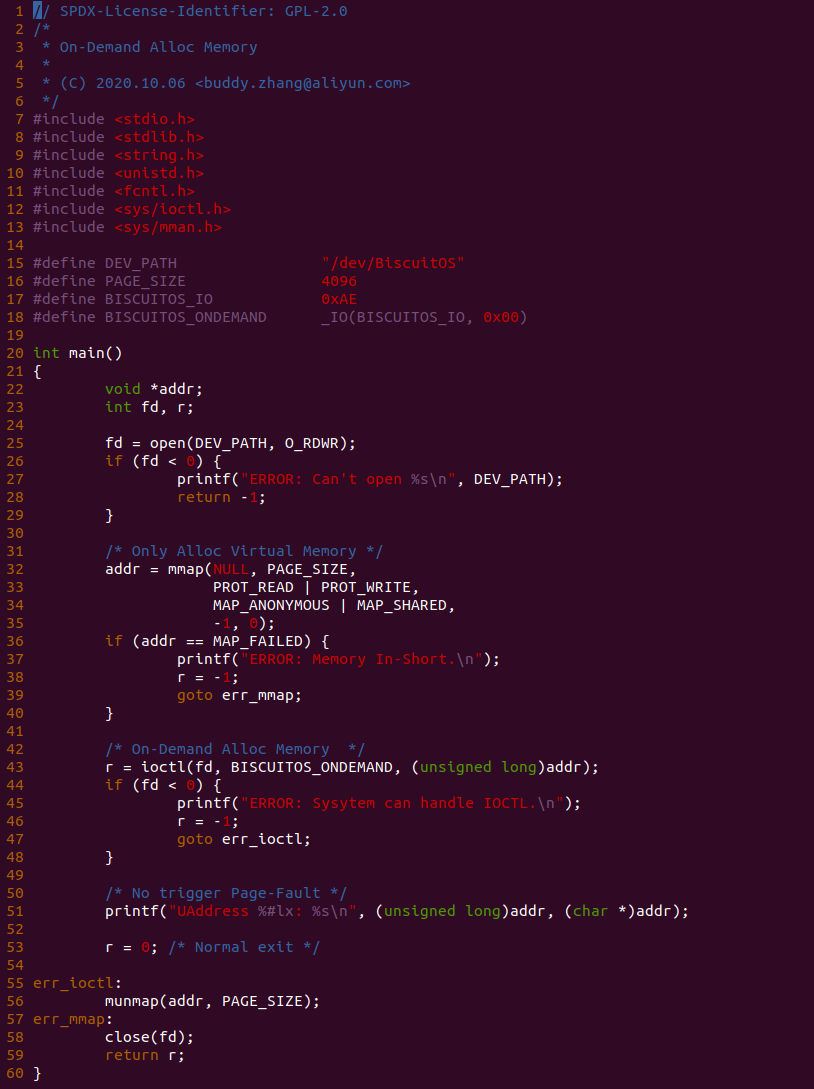

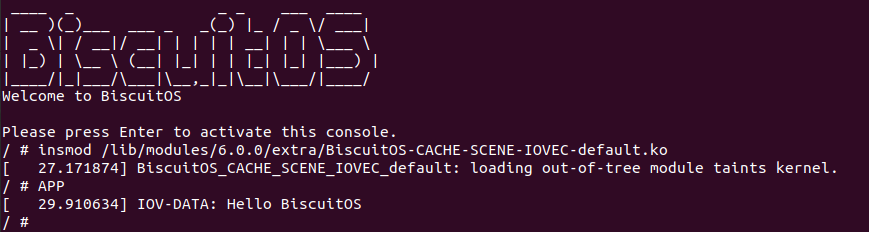

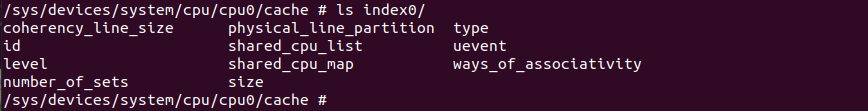

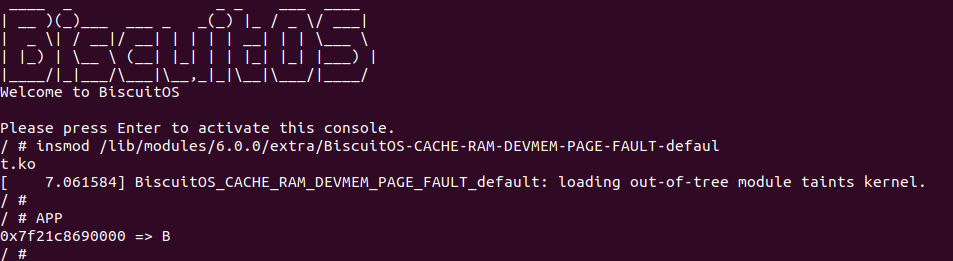

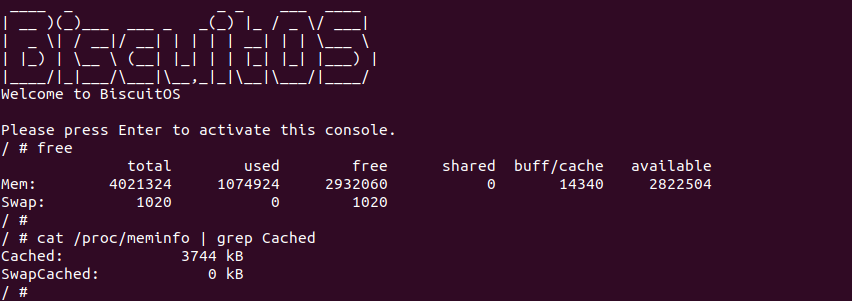

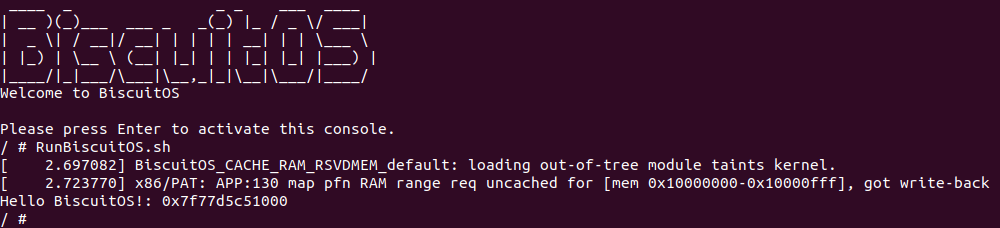

什么是 CACHE? CACHE 应该怎么用? SMP 多核架构下 CACHE 起到什么作用? 学会了 CACHE 是否改变对软件的认知? …. BiscuitOS 社区推出的 CACHE 实践专题通过图形化、实践化的方法带大家了解、学习、并使用 CACHE,首先通过一个实践案例认识 CACHE,其在 BiscuitOS 的部署逻辑如下:(第一次使用 BiscuitOS 实践的童鞋请先戳 CACHE 实践)

cd BiscuitOS

make menuconfig

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough --->

(4096) Memory Size(MiB)

(hugepagesz=1G hugepages=1) CMDLINE on Kernel

[*] Package --->

[*] CACHE --->

[*] CACHE on BiscuitOS --->

# 源码目录

# Module

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-default/

# 部署源码

make download

# 在 BiscuitOS 中实践

make build

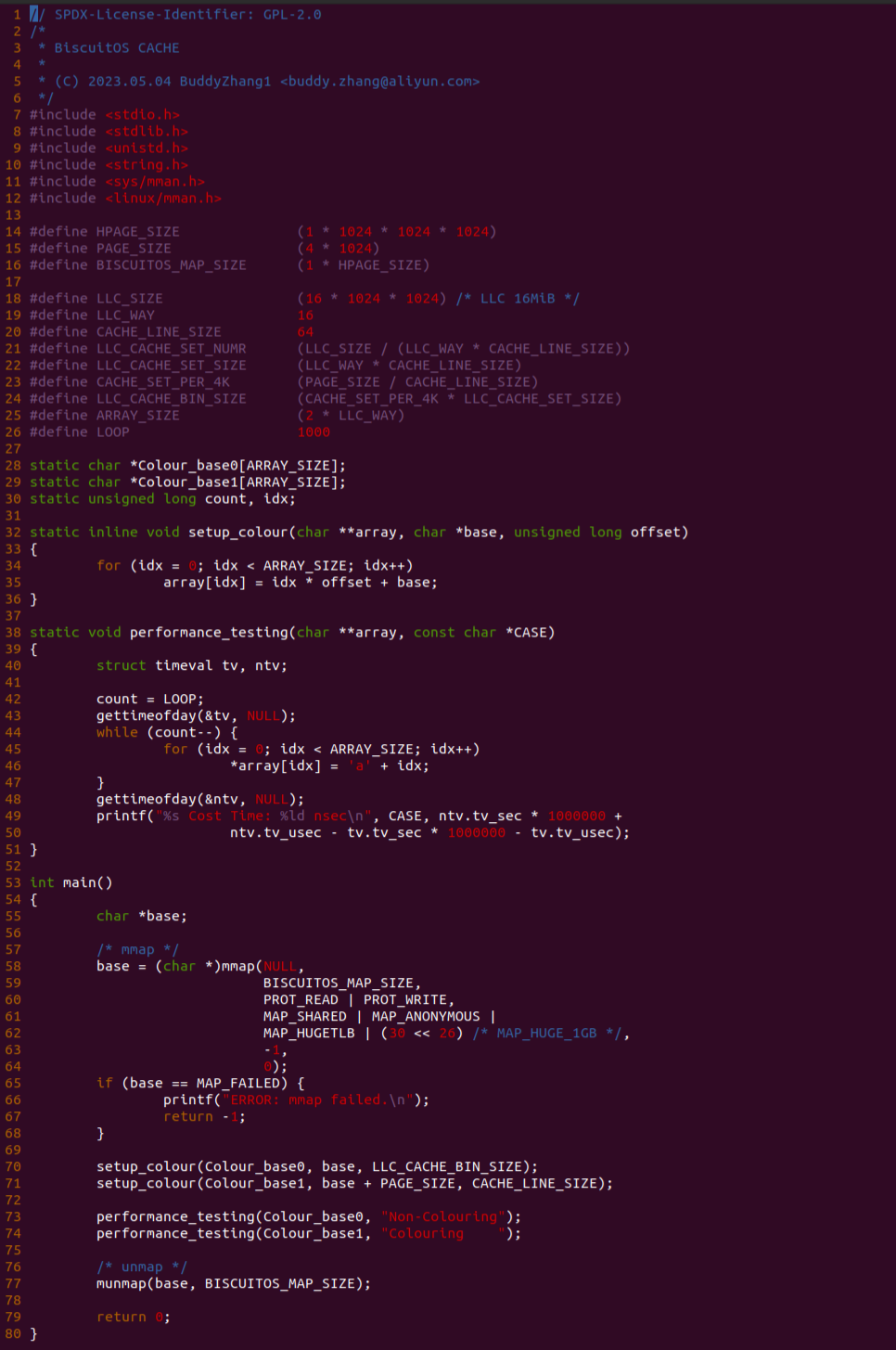

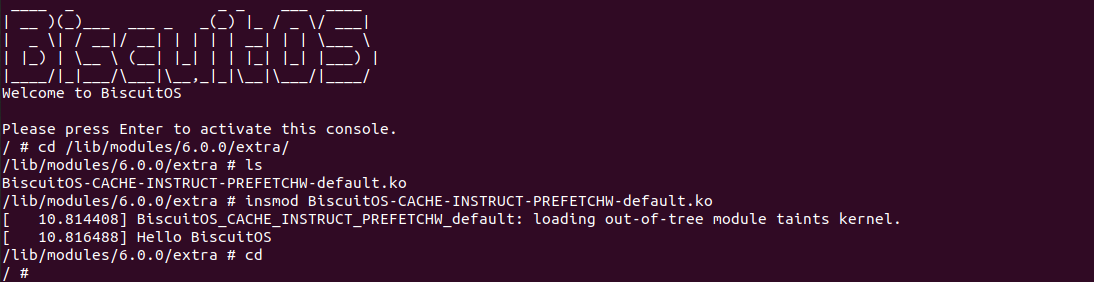

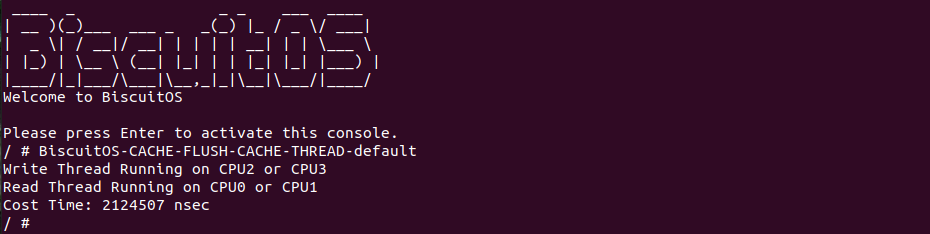

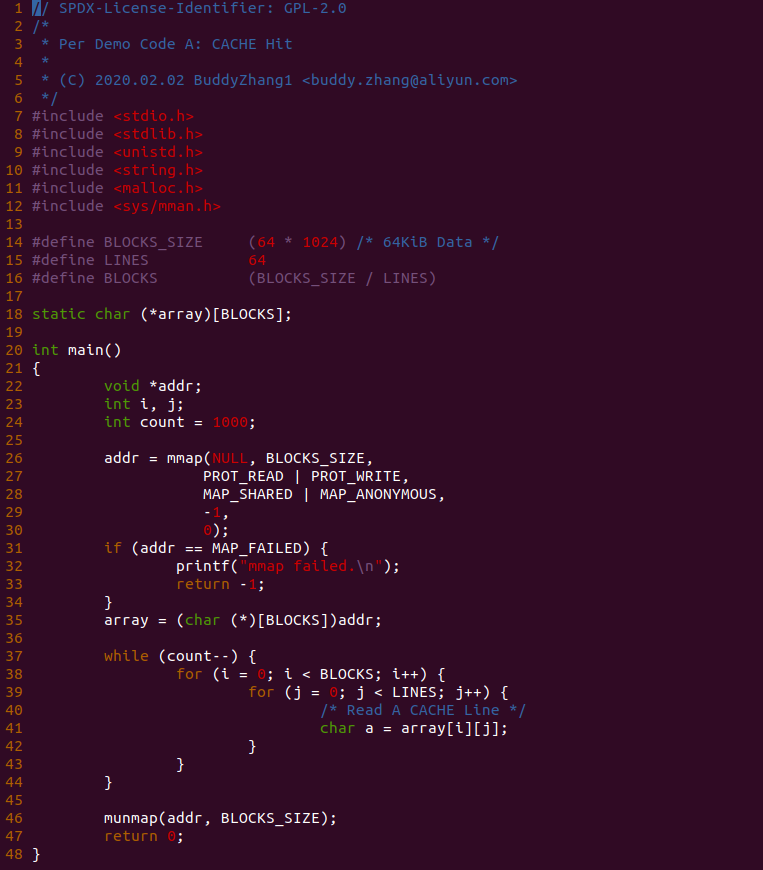

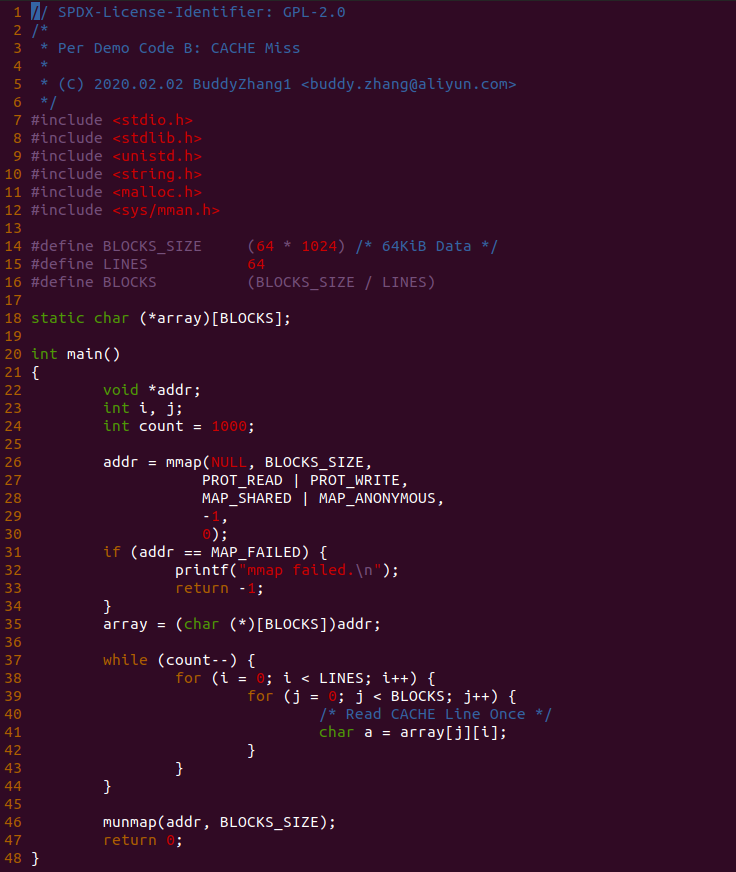

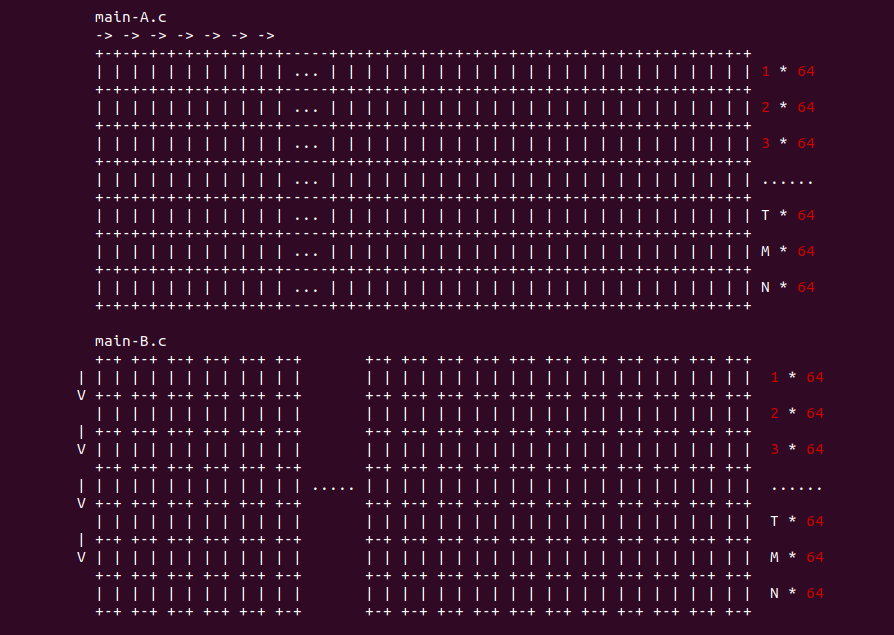

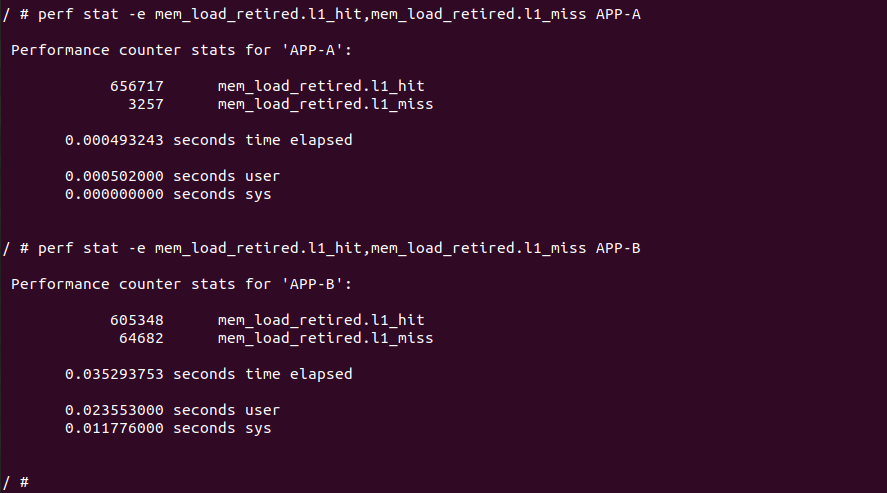

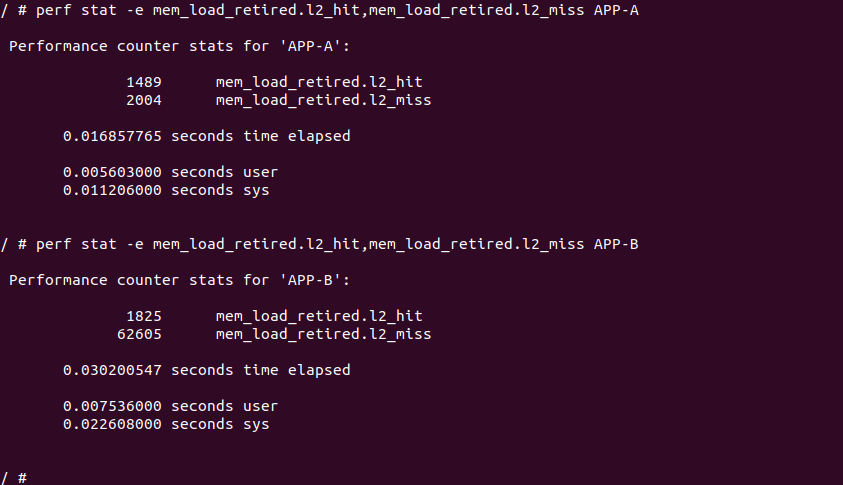

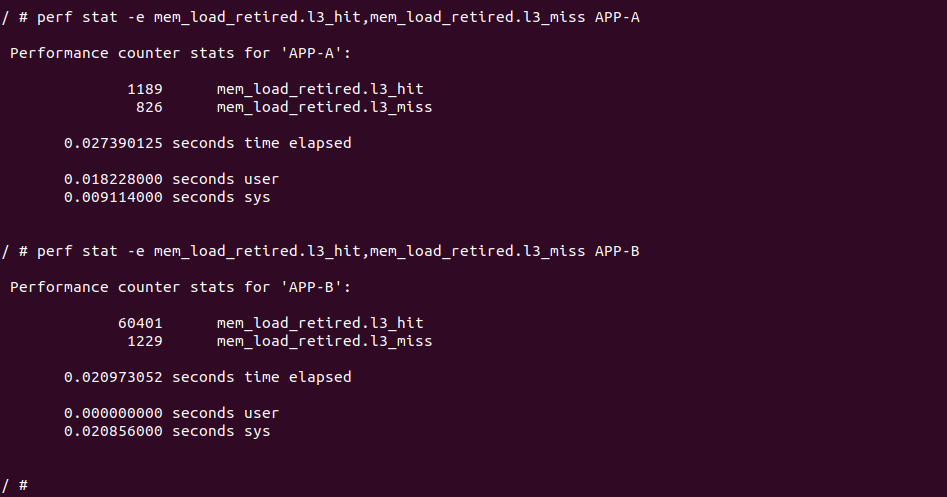

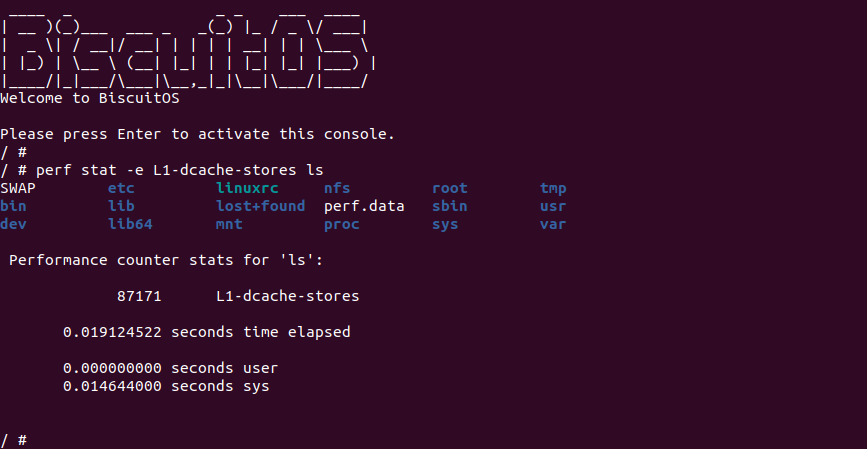

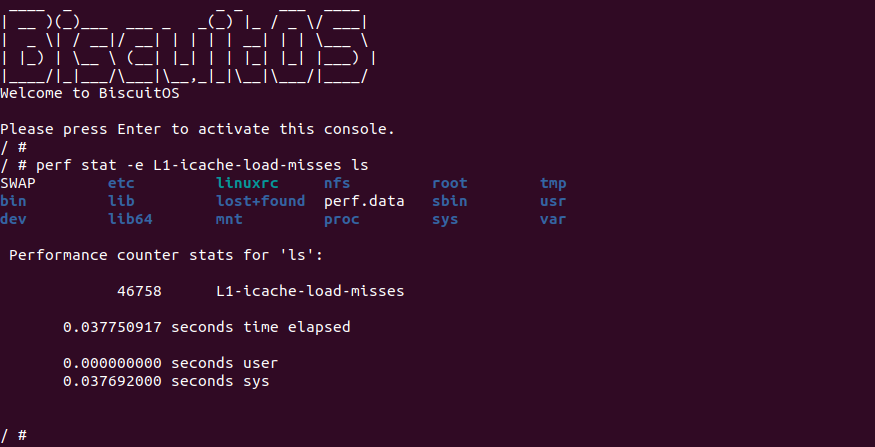

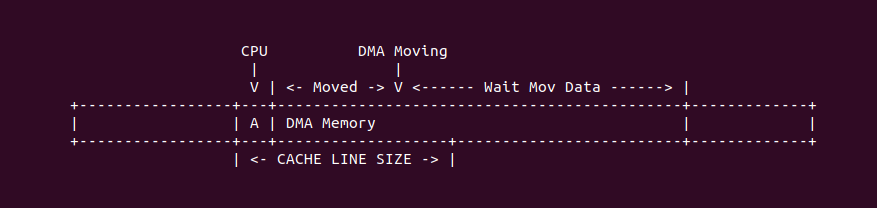

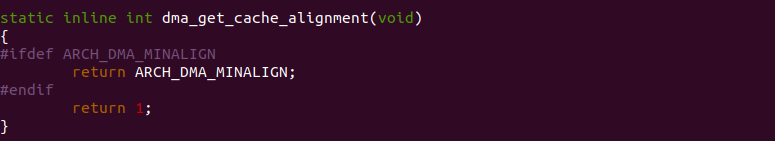

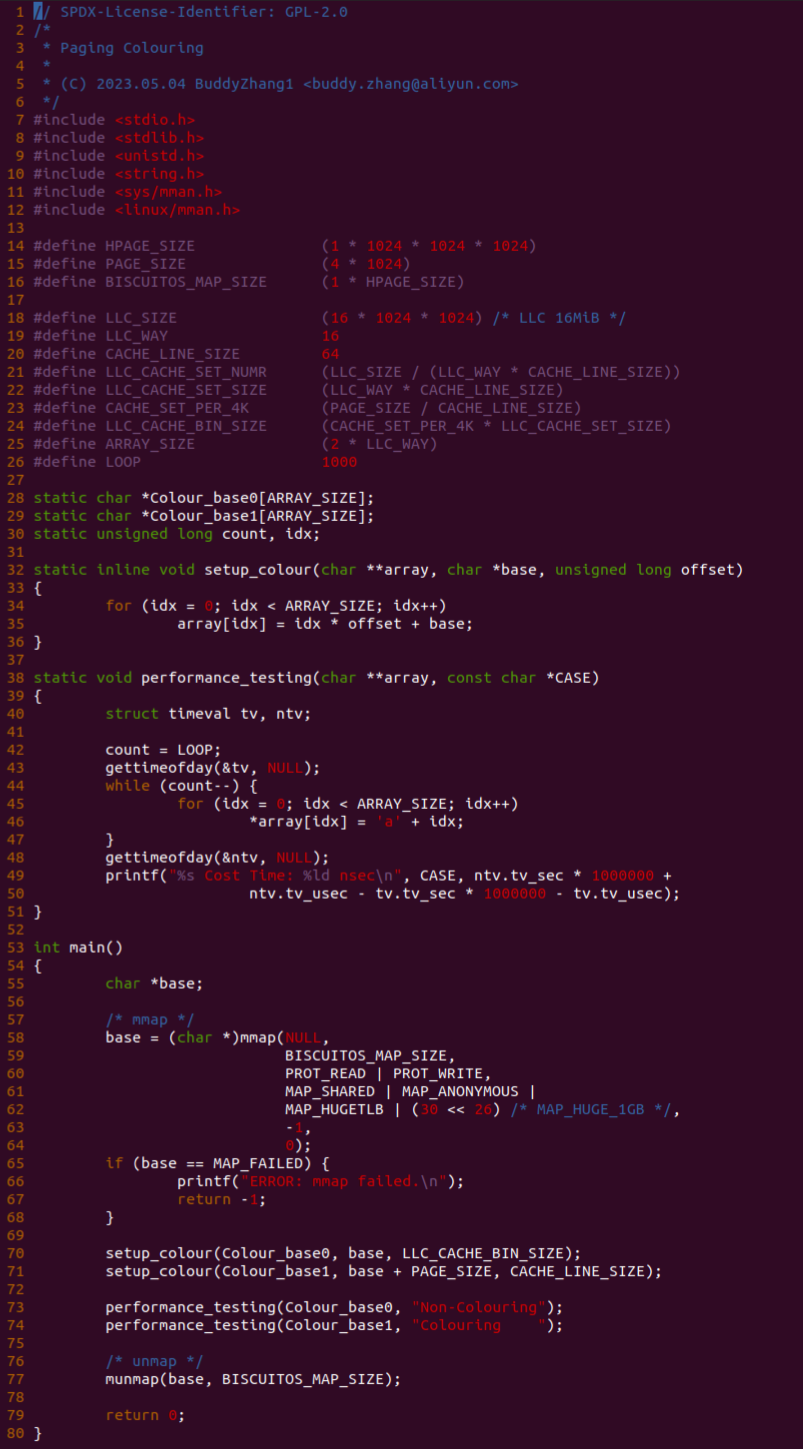

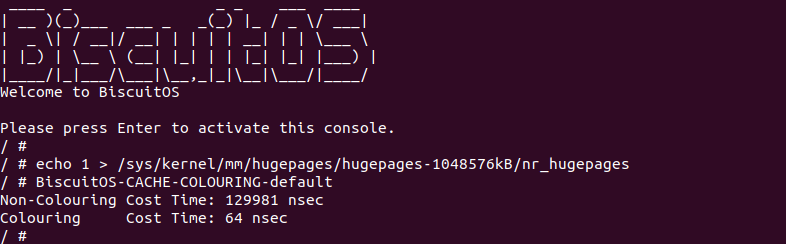

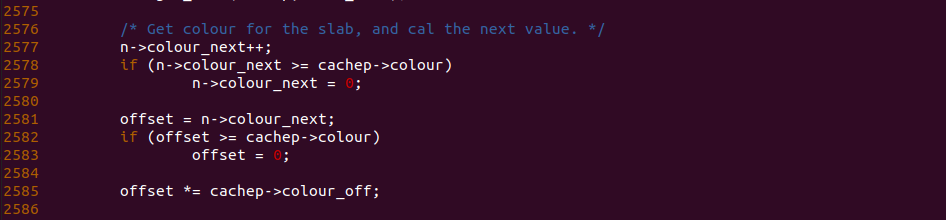

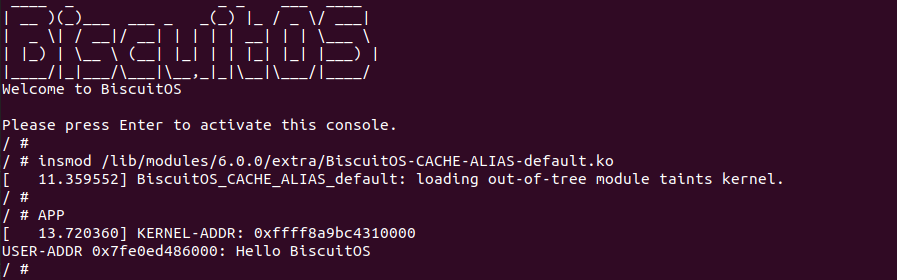

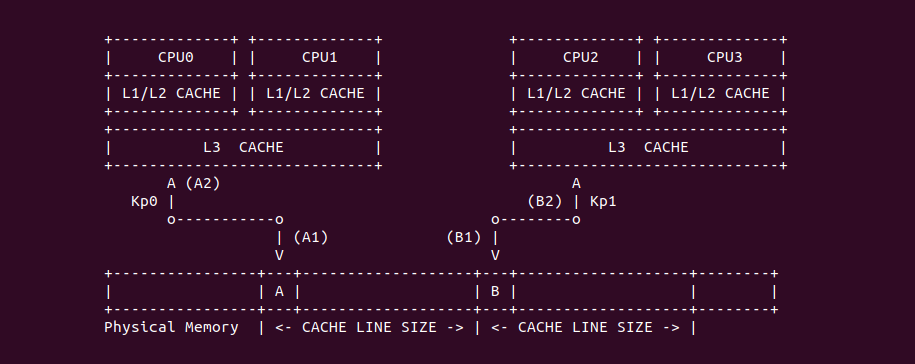

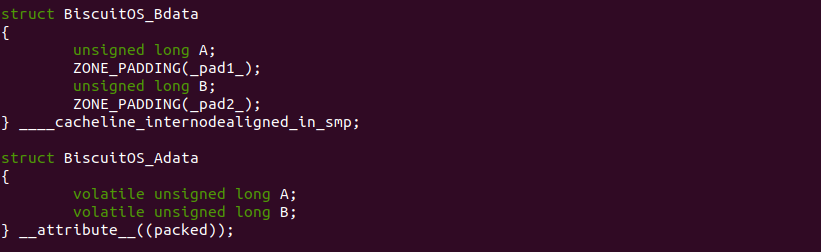

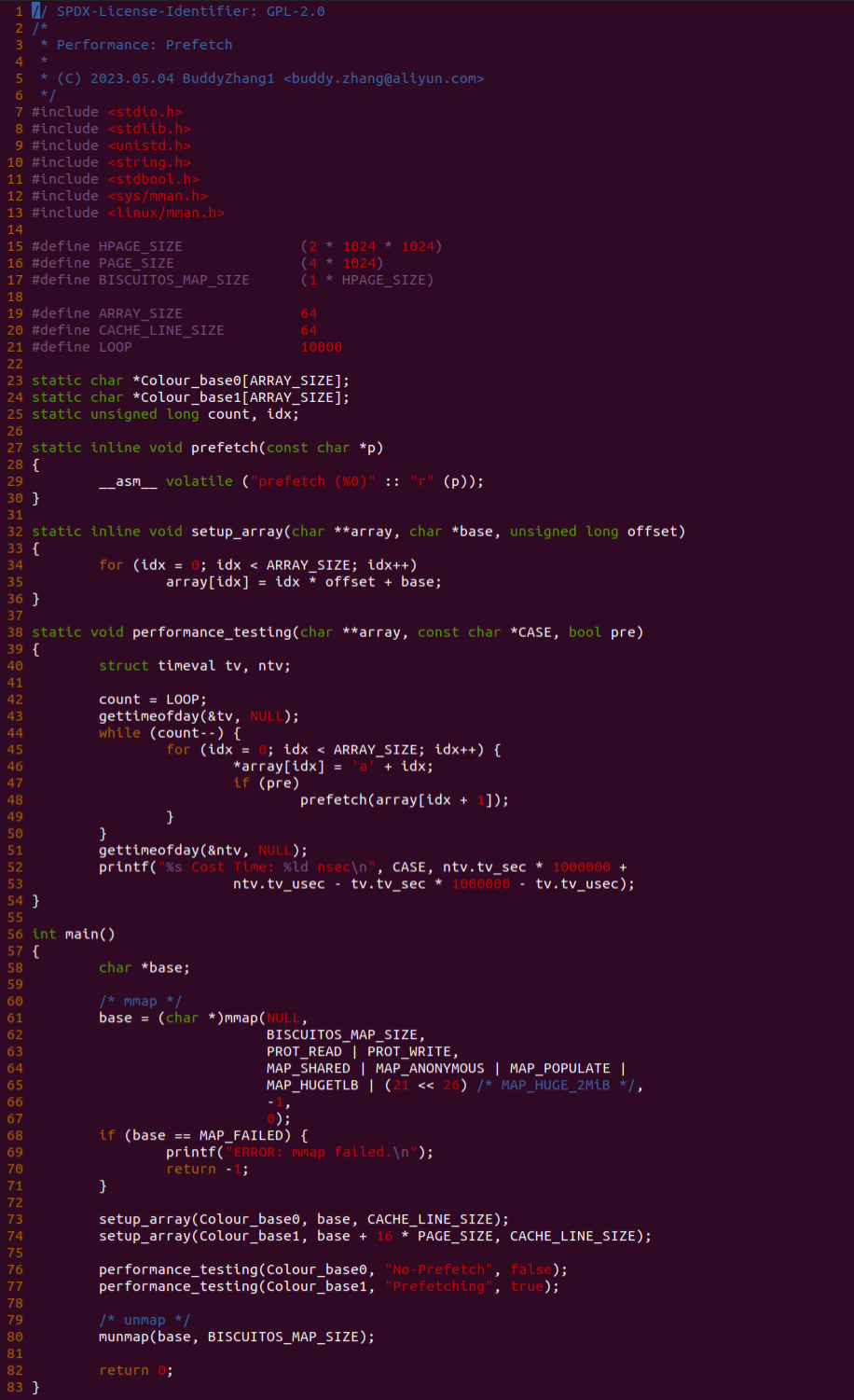

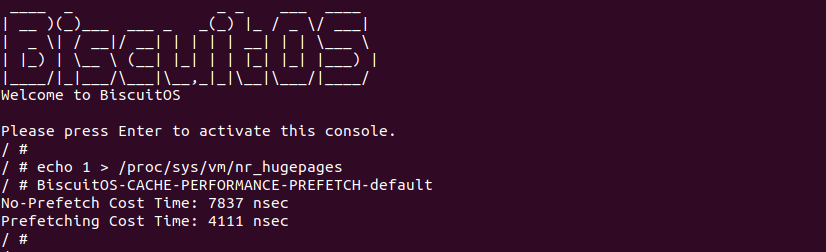

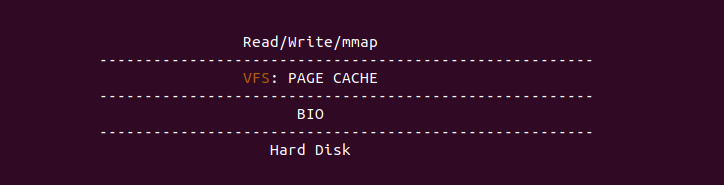

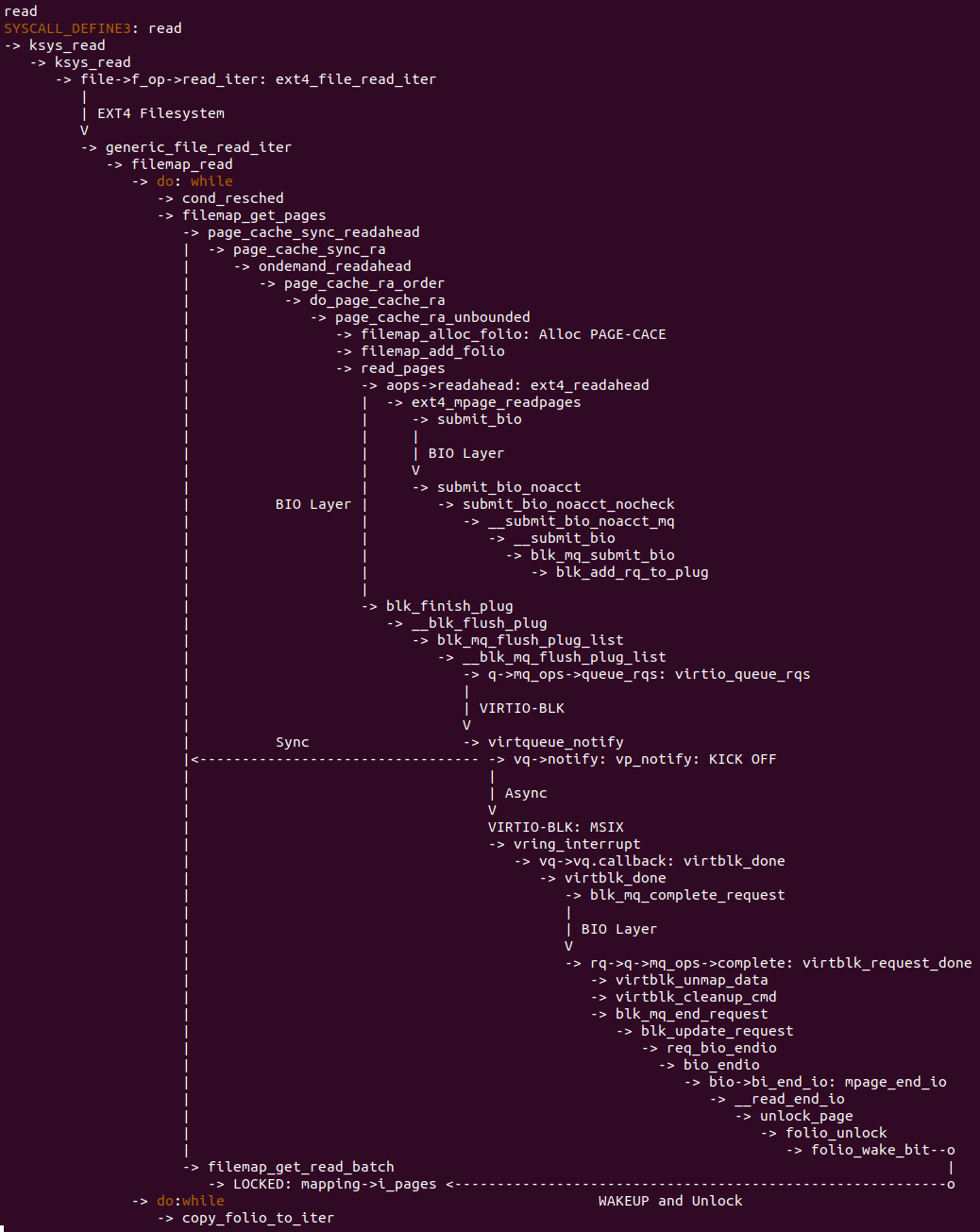

实践案例是一个用户空间的程序,逻辑很简单,定义了两个数组 Colour_base0[] 和 Colour_base1[], 并申请了一个匿名大页,Colour_base0[] 按 LLC_CACHE_BIN_SIZE 为粒度从匿名大页起始处连续采集 ARRAY_SIZE 个虚拟地址,将这些虚拟地址存储到数组里; Colour_base1[] 则按 CACHE_LINE_SIZE 粒度从大页起始虚拟地址之后 PAGE_SIZE 处连续采集 ARRAY_SIZE 个虚拟地址; 接下来将两个数组传入 performance_testing() 函数里进行性能测试,测试的逻辑是循环 LOOP 次,每次程序都会遍历访问数组的每个成员,最后统计循环耗时. 两个数组的数据量是相同的,按理来说性能差异应该很小。那么接下来在 BiscuitOS 上实践该案例:

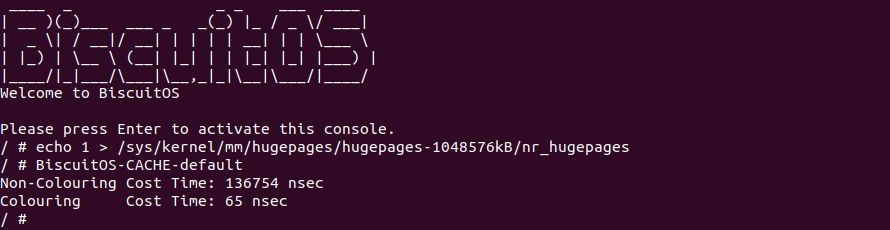

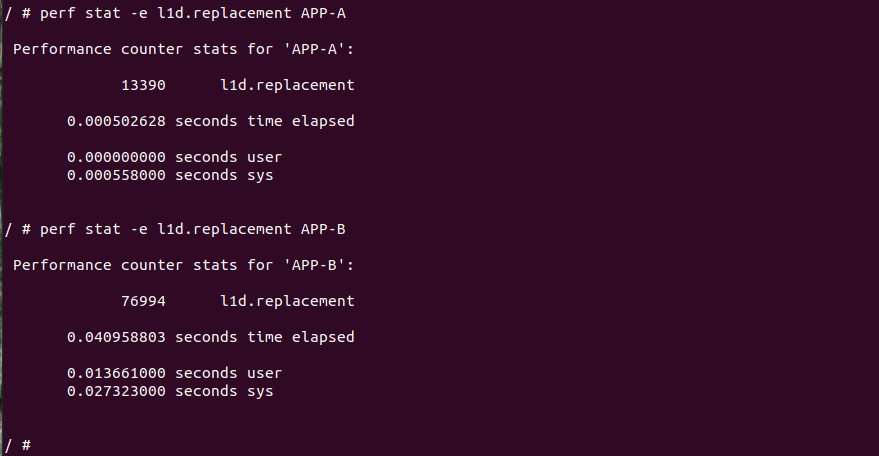

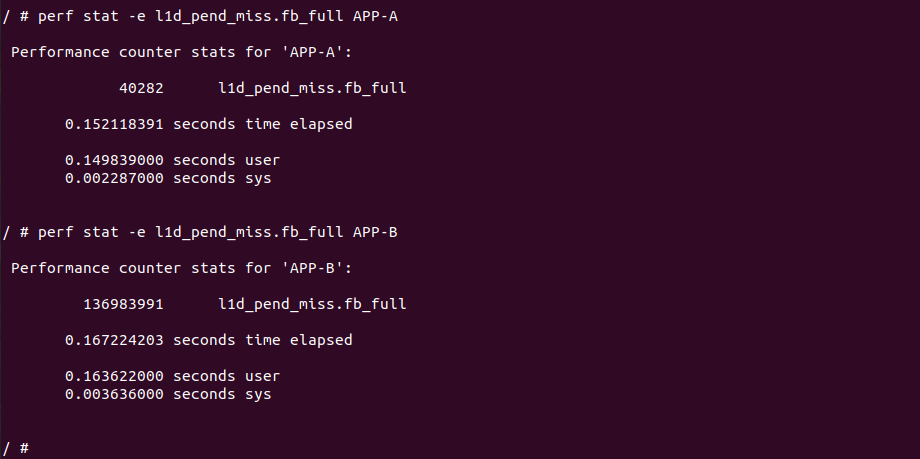

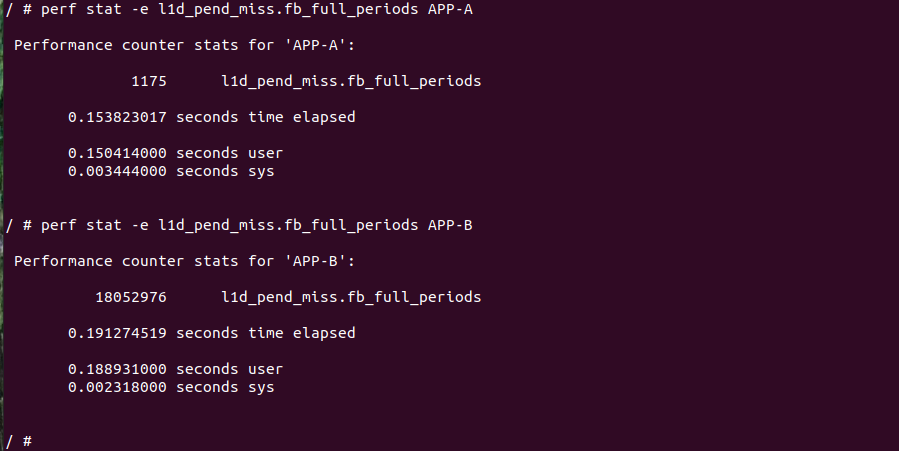

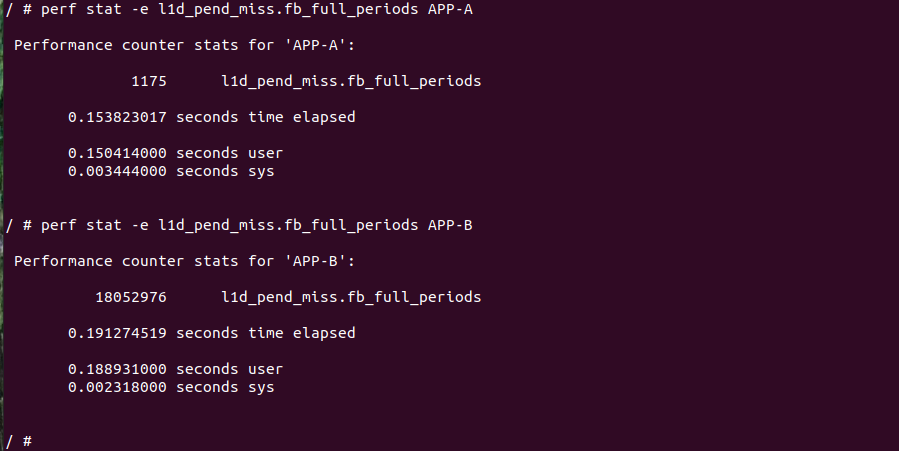

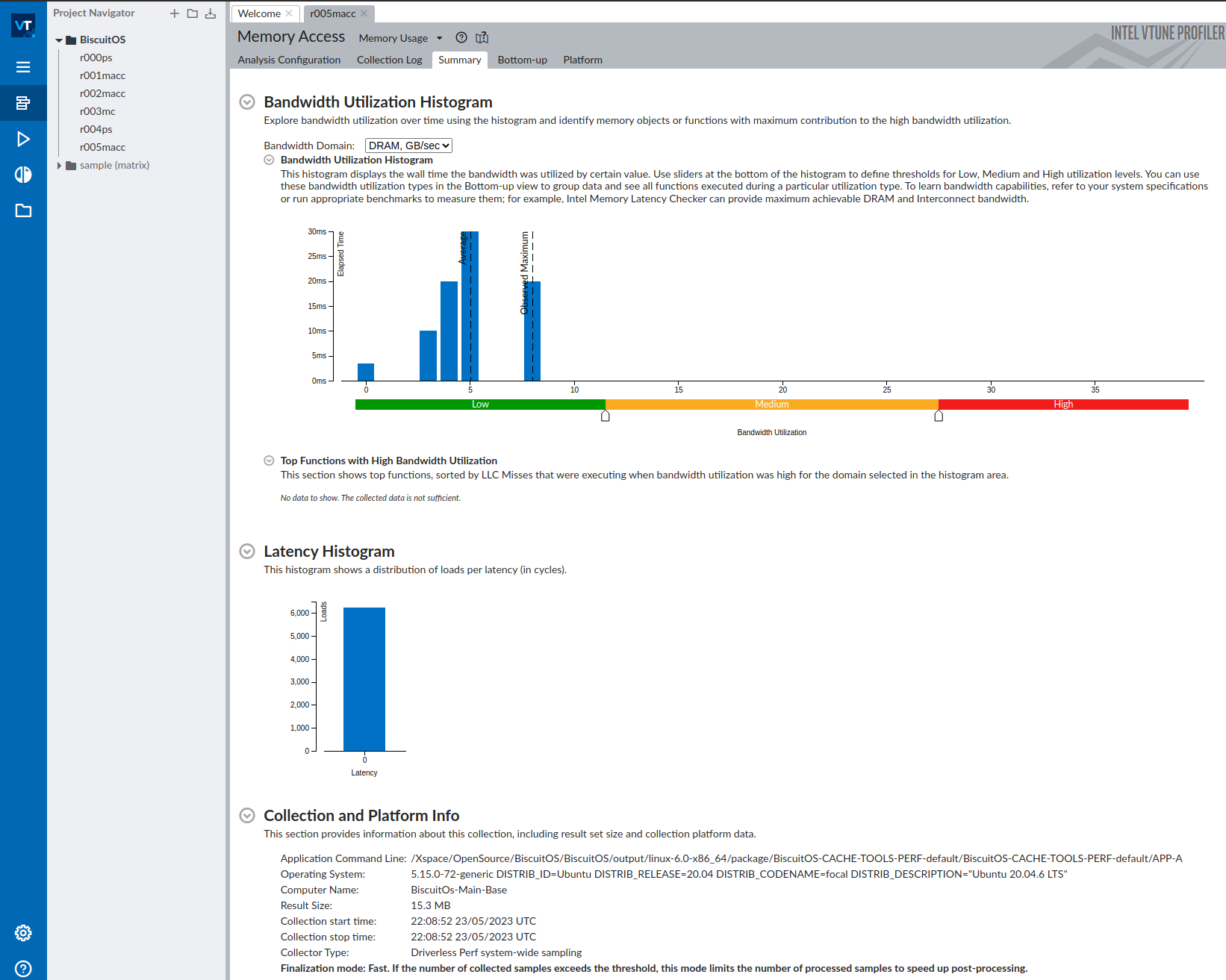

BiscuitOS 运行之后,向内核申请一个 1G 的 Hugetlb 大页,然后运行测试程序,可以看到两侧测试性能差异巨大。回看程序,都是访问相同的数据量,为什么会存在这么大的性能差异,这就是 CACHE 的魅力,是不是很魔法,明明软件上没有任何差异的操作,结果天差地别, 在从另外一个层面认识 CACHE:

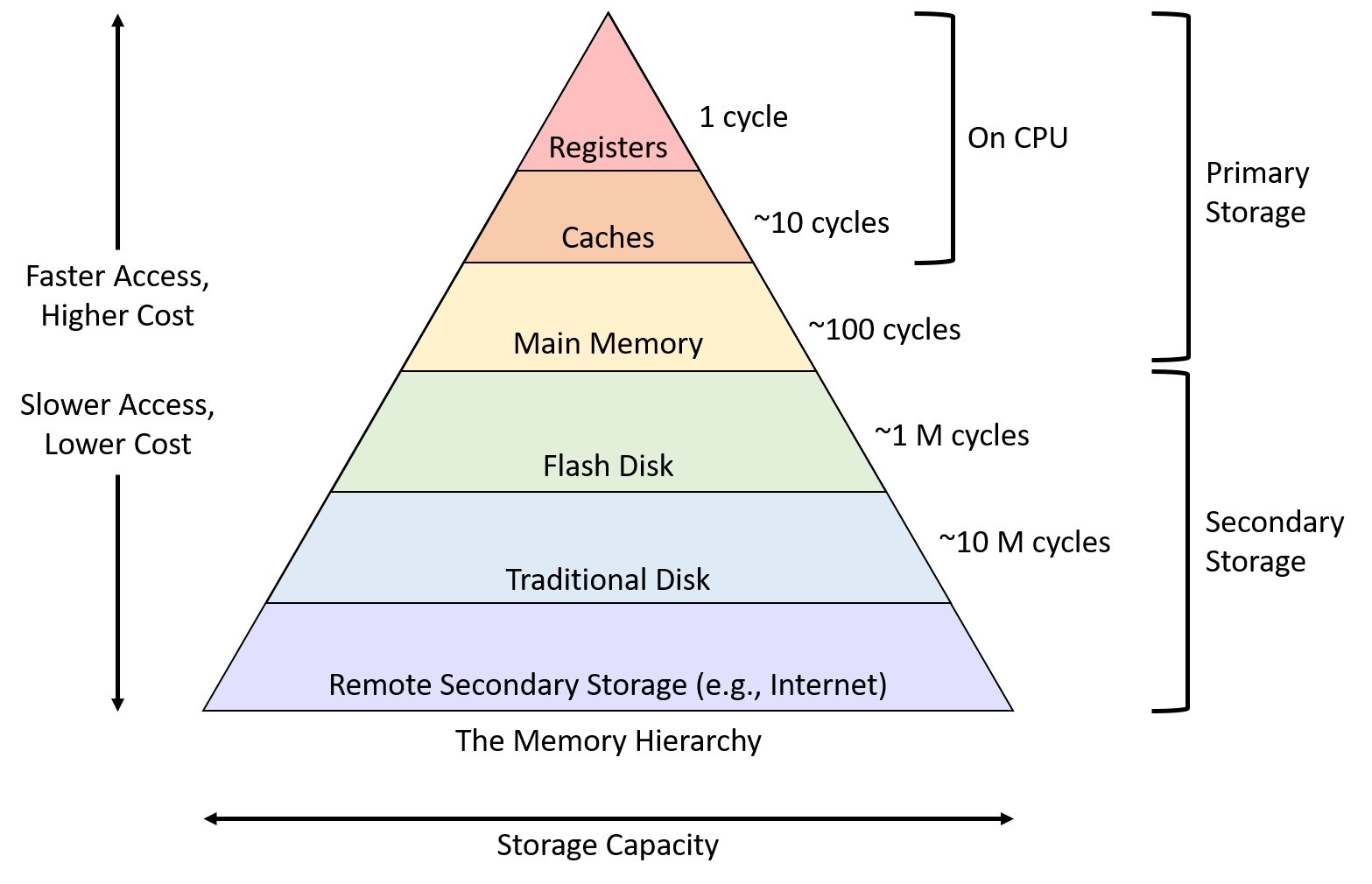

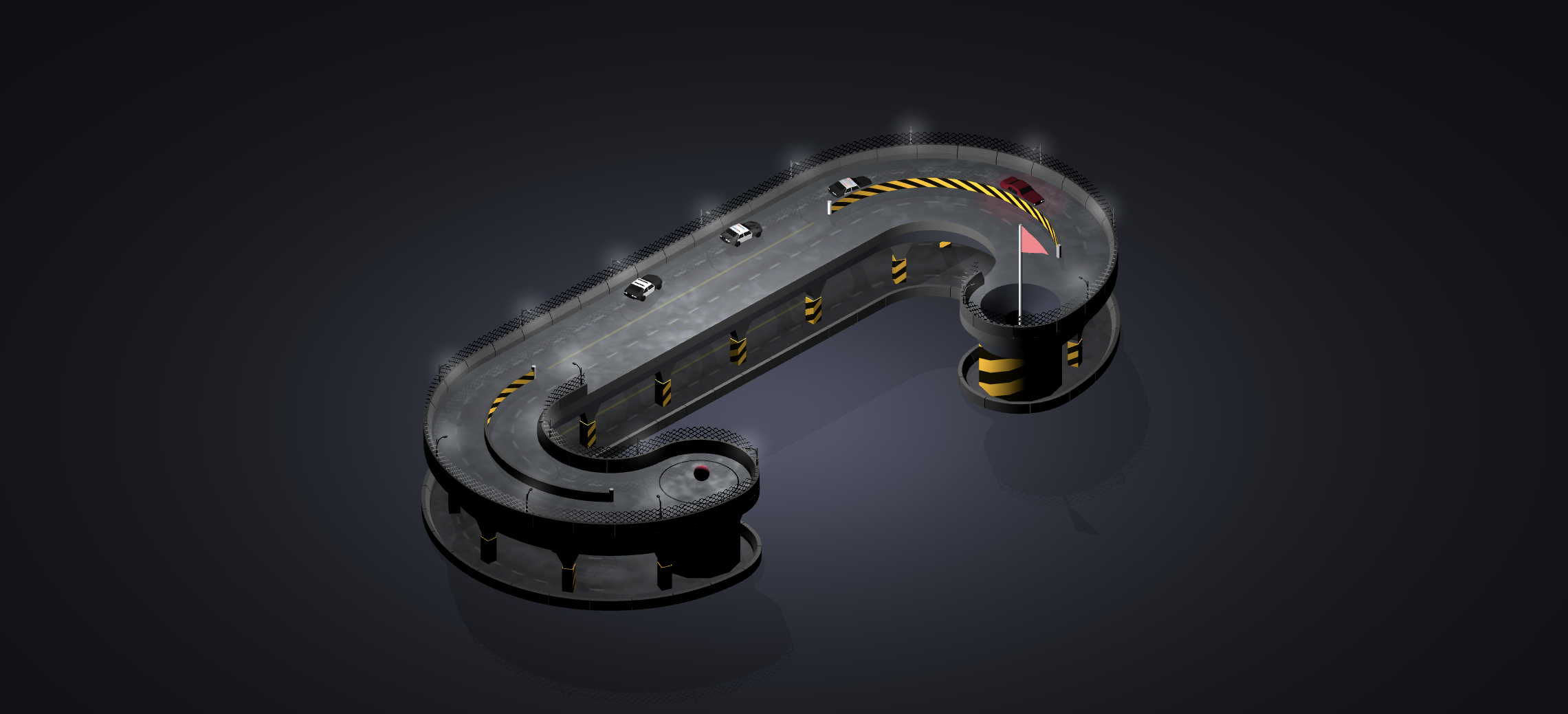

上图是典型的存储系统性能金字塔,可以看到 CACHE 位于 Register 和 Main Memory 之间,为什么 CACHE 的使用可带来性能的极致提升,这还得从一个故事讲起: 假设将 CPU 访问数据比作开发者在图书馆找资料,那么:

- CPU 访问 L1 CACHE 相当于开发者在书桌上的书本里查找资料

- CPU 访问 L2 CACHE 相当于开发者发现桌上的书本没有找到,那么从身后的书包里的书进行查找

- CPU 访问 L3 CACHE 相当于开发者发现书包的书本没有找到,那么从远处的书架上的书进行查找

- CPU 访问内存相当于书架上的书没有找到,那么去问管理员,管理员告诉你书在五楼某个书架,然后你从一楼跑去五楼的书架上去找书

- CPU 访问磁盘相当于你跑到 5 楼的书架却发现书已经没了,从管理员那里知道这本书正在捕获,需要等半年之后才能到,于是你等了半年之后等到了书.

从上面的实践案例和故事是不是对 CACHE 有了初步认识,在单核年代 CACHE 是比较容易理解的,就是加速内存的访问,但到了多核年代,事情变得越来越复杂,虽然硬件自动完成很多工作了,但对于折腾性能不休的我们,学习 CACHE 从中对多核架构下的编程将带来颠覆性的认知,从而利用 CACHE 优化程序的性能,使收益最大化。BiscuitOS 社区提供的 CACHE 专题将从以下几个方面对 CACHE 进行讲解,开发者可以按照以下顺序进行学习:

- CACHE 实践教程: 实践是认知的源泉,千里之行始于实践

- CACHE 通用基础: 基础不牢地动山摇,夯实基础,厚积薄发

- Linux CACHE 机制: 学以致用,Coding on Linux

- Intel® X86 ™Processors 架构 CACHE 机制: 洞悉前沿科技

- CACHE 调试工具合集: 工欲善其事,必先利其器

- CACHE 应用场景: 丢掉幻想,直接实战

- CACHE BUG/Fault: 思其过,行长远

- CACHE 进阶研究: 得其意,忘其形

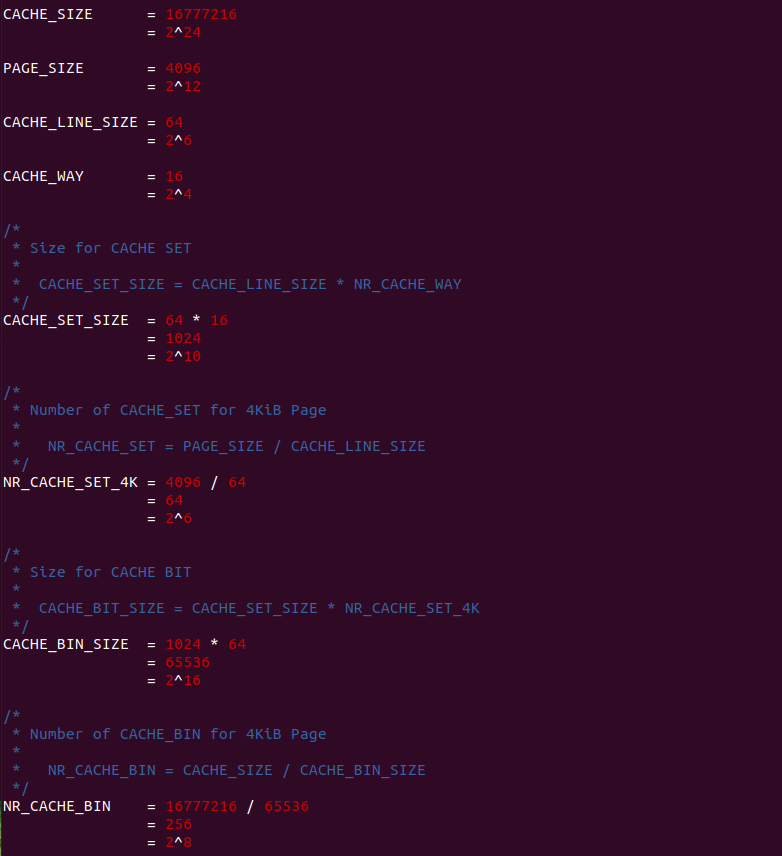

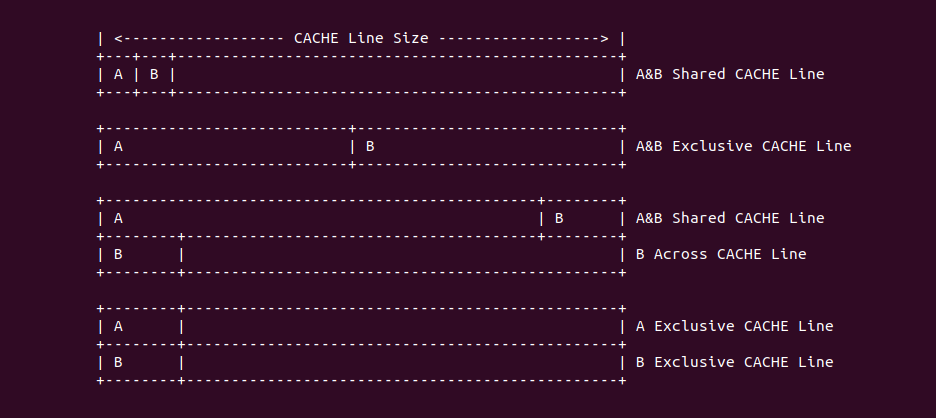

CACHE 基础概念

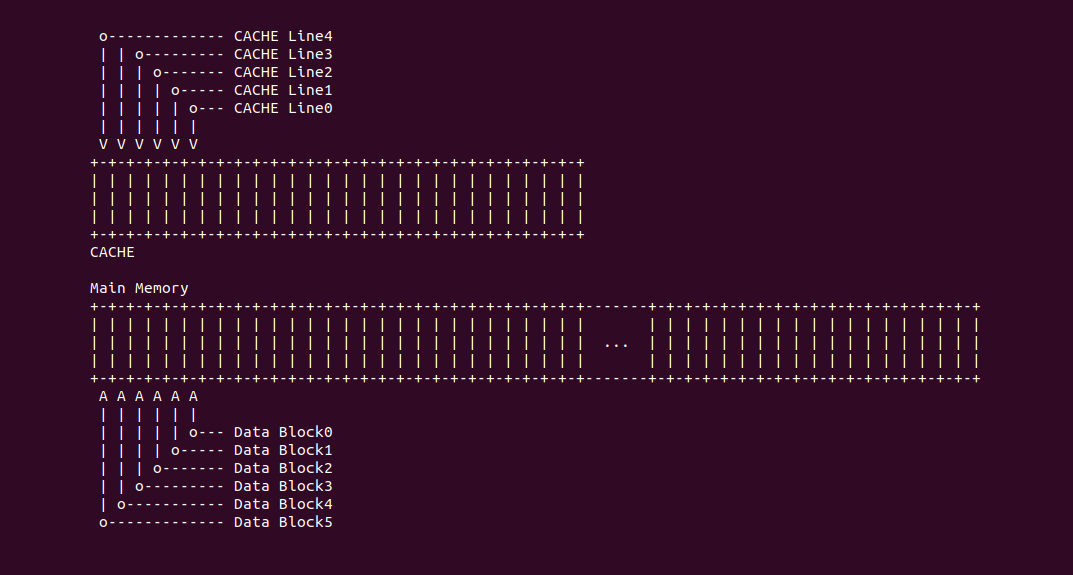

CACHE 是由一组称为缓存行(CACHE Line)固定大小的数据块组成,其长度称为 CACHE Line Size, 在有的架构中 CACHE Line Size 为 64 个字节。每个 CACHE Line 完全是在一个突发读操作周期中进行填充或更新, 即使处理器只访问存储器上的一个字节,CACHE 控制器也会将 CACHE Line Size 的数据块加载到 CACHE 里. 同理将内存中 CACHE Line Size 大小的数据块称为 Data Block.

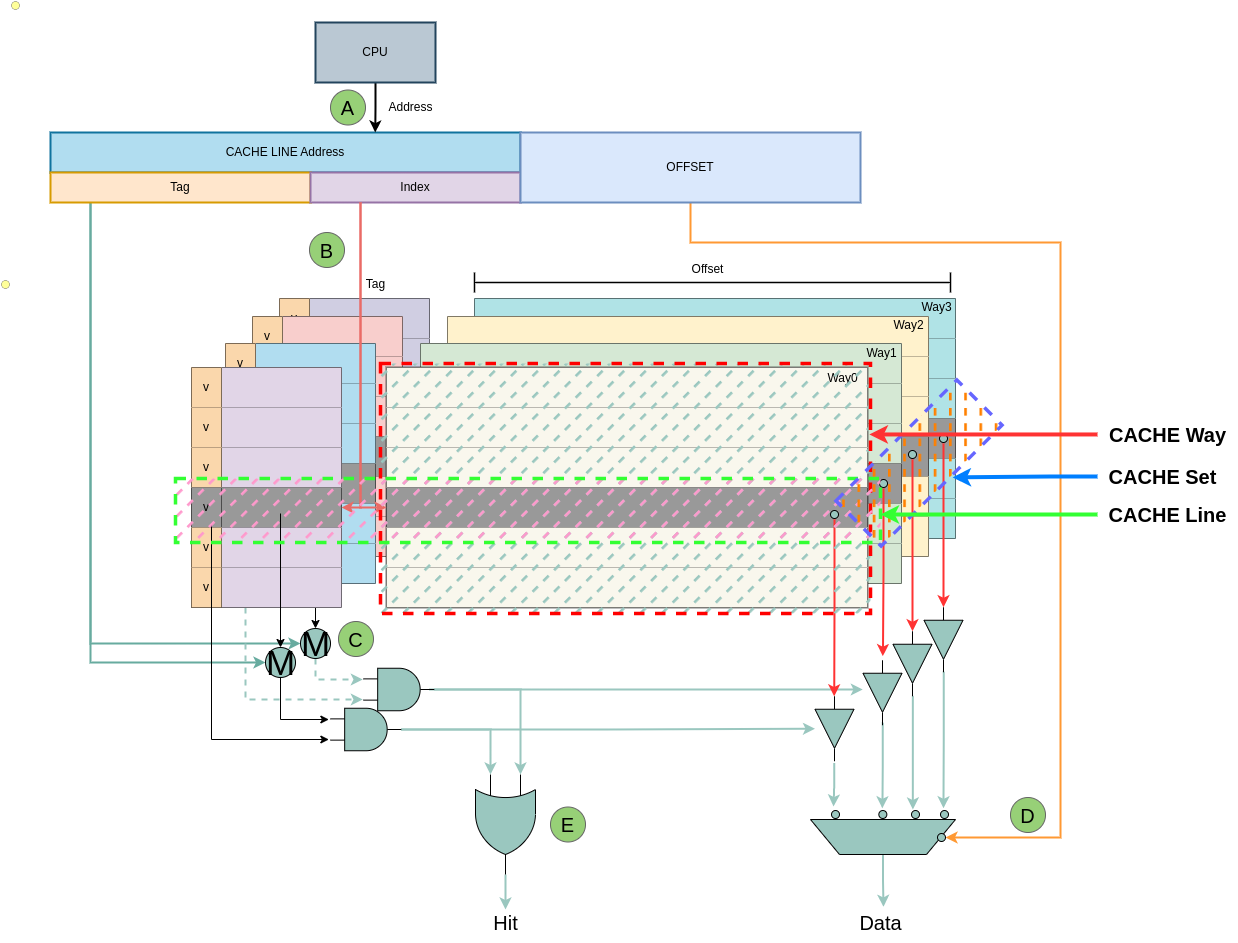

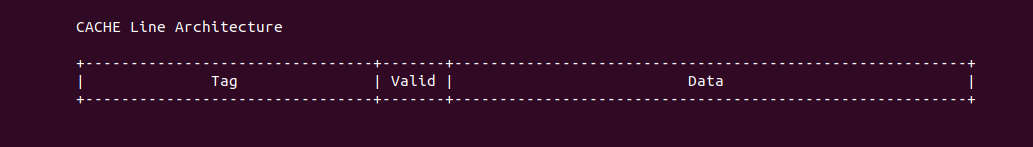

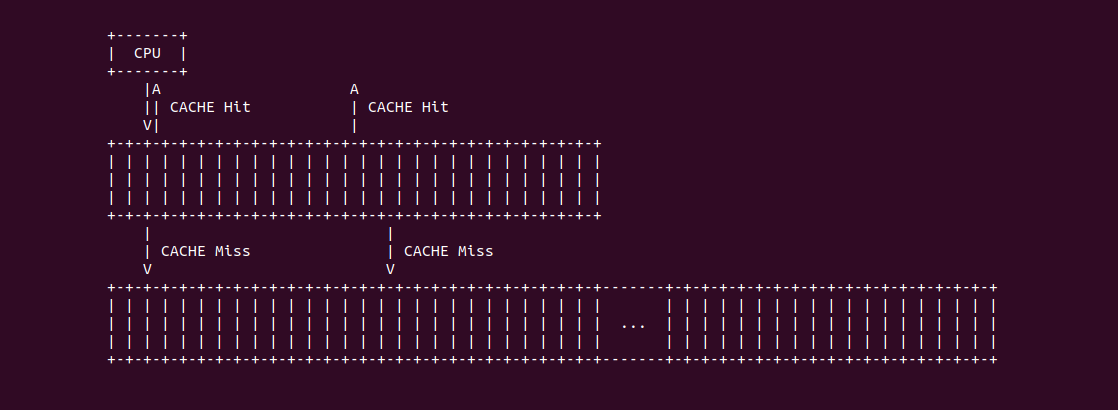

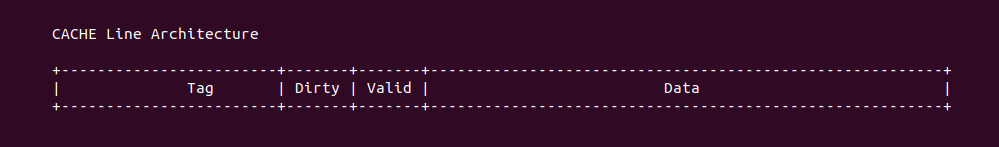

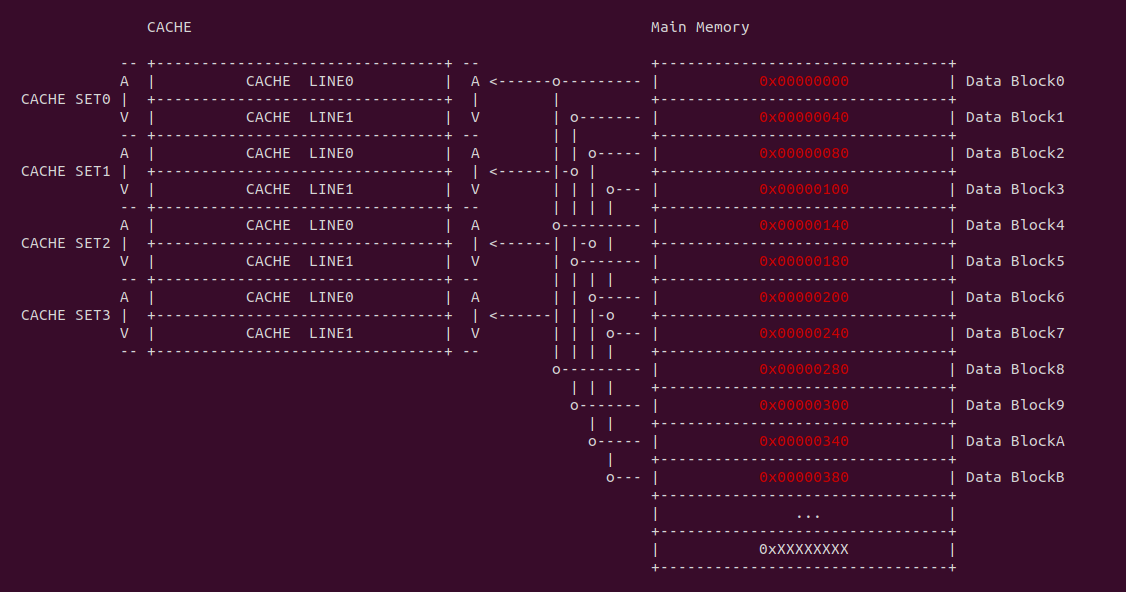

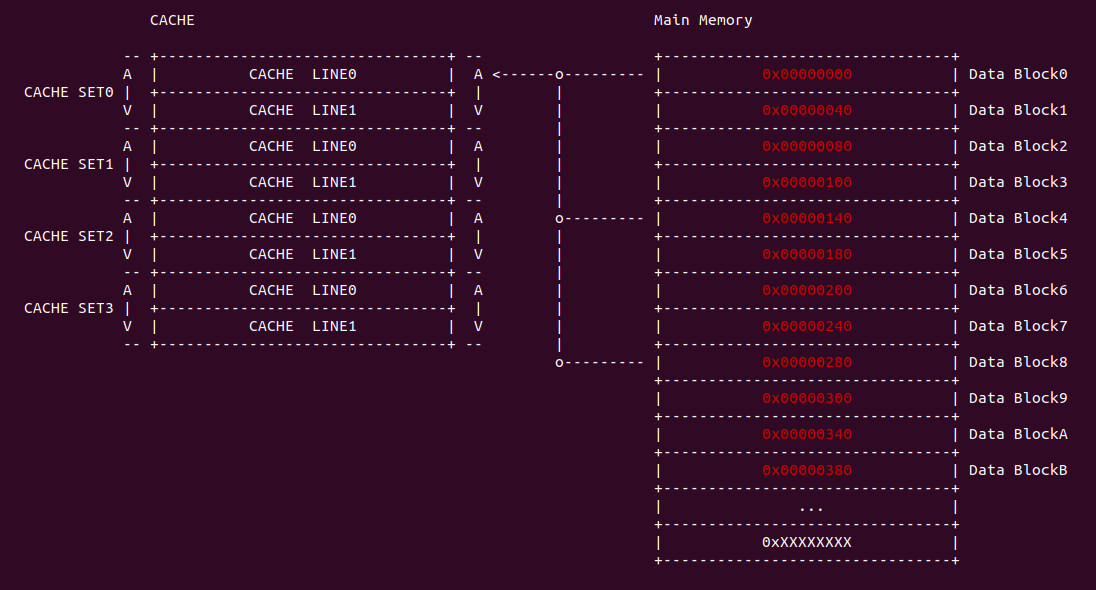

CACHE Line 是 CACHE 最基础的组成单位,将 N 个 CACHE Line 组成的集合称为 CACHE Set, 那么称 CACHE 是 N 路组相联(N-Way Set-associative Cache), 所以从硬件结构来看 CACHE 被划分成 N 个垂直面,每个垂直面上有多个 CACHE Line,对所有的 CACHE 垂直面进行一次横切的 CACHE Line 合集就是 CACHE Set. CACHE Line 由两部分组成: Tag 和 Offset 部分,其中 Tag 字段由于匹配具体的 Data Block,Tag 字段中还包含了 valid 标志位,该位置位说明 CACHE Line 的内容有效,反之 CACHE Line 的内容无效。CACHE Line 的 Offset 部分存储 Data Block 的内容.

- CACHE Hit(命中): 指的是 CPU 要访问的地址正好缓存在 CACHE Line 中

- CACHE Miss(缺失): 指 CPU 要访问的地址没有缓存在 CACHE Line 中.

- CACHE 颠簸: 指的是 CPU 访问多个地址导致某个 CACHE Line 来回更新和填充.

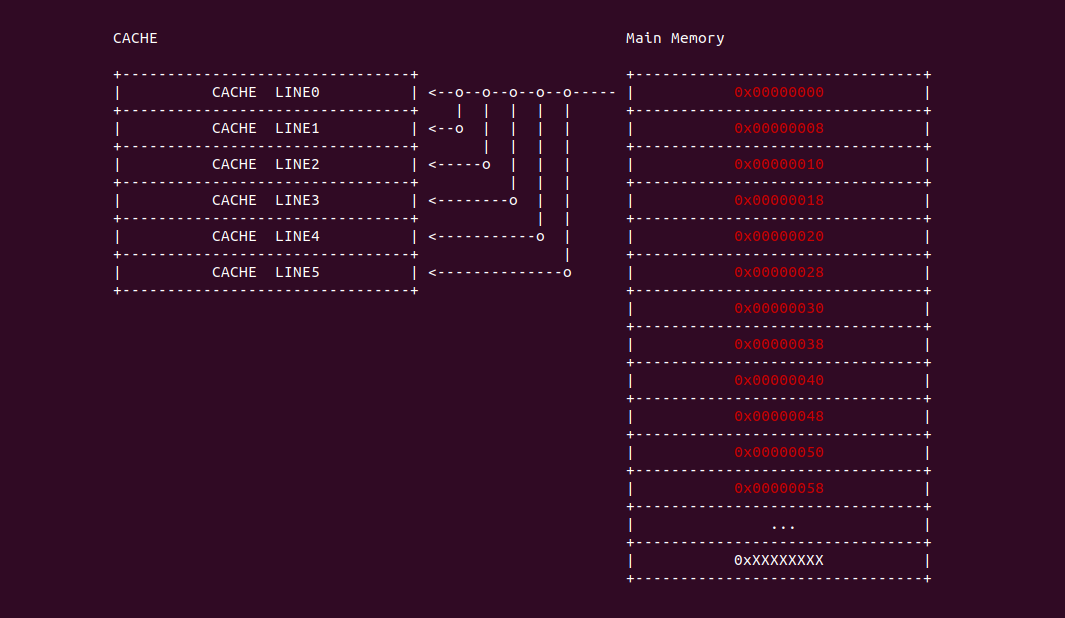

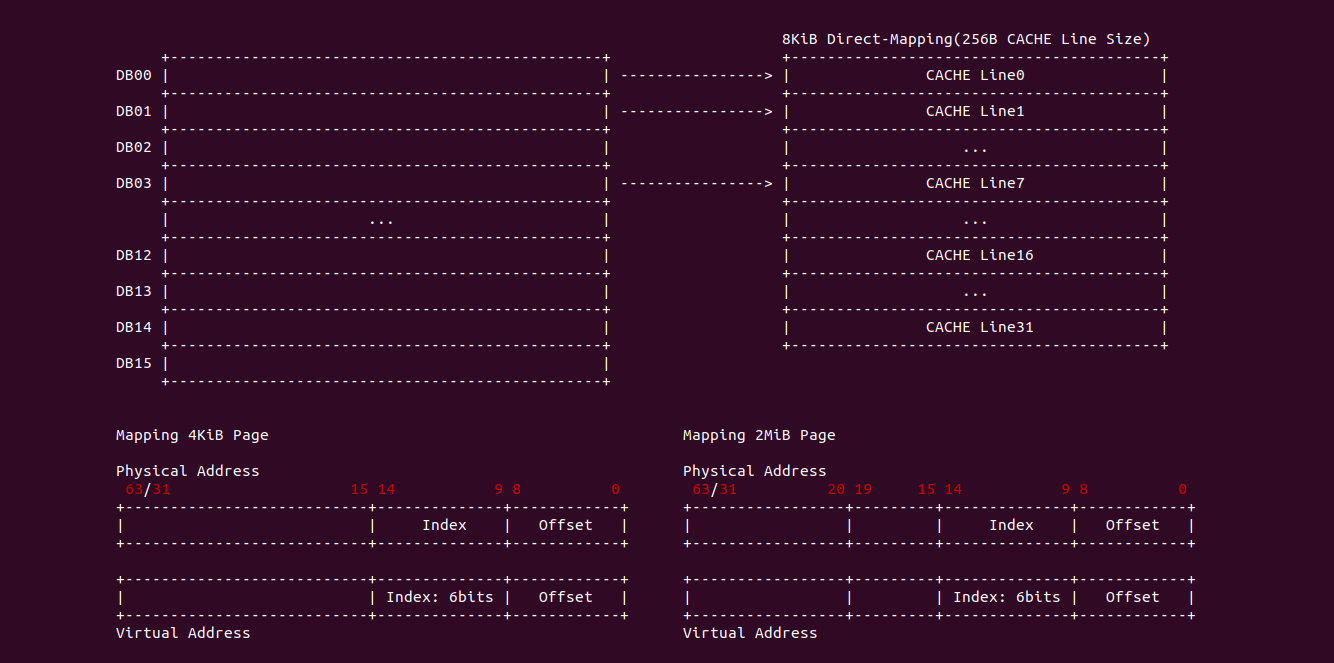

直接映射

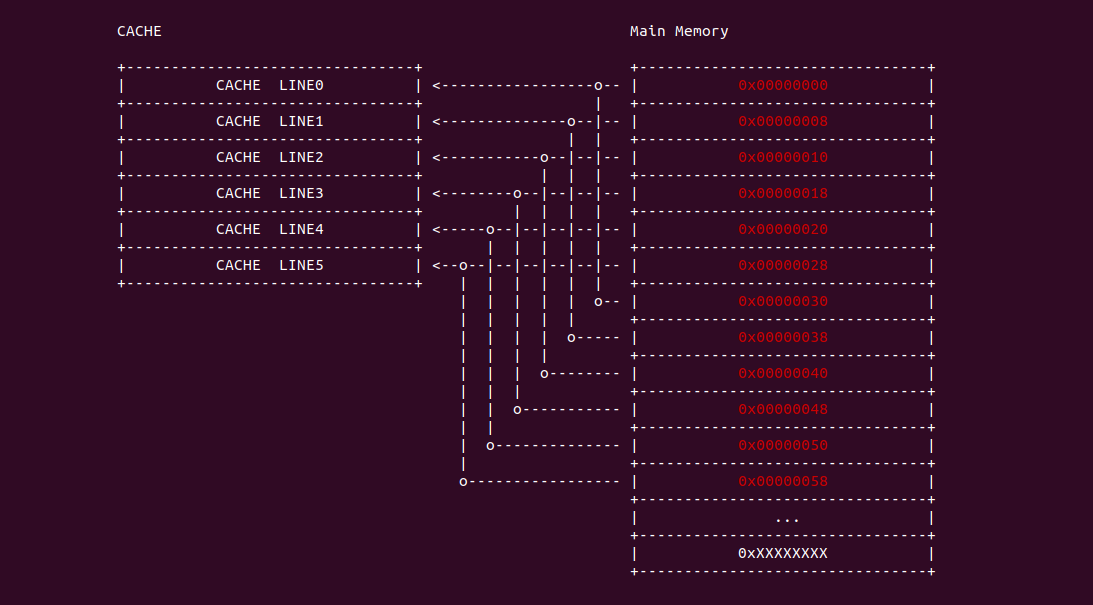

直接映射(Direct-mapped) 指的是内存中的 data block 按顺序映射到指定的 CACHE Line, 且每个 data block 只能映射到一个 CACHE Line 里,那么内存 data block 与 CACHE Line 一一对应,那么可以使用一个线性公式表示两者之间的关系,这个线性公式是求模公式,模数即为 CACHE Line 的数量,内存地址求模之后就可以知道其映射的 CACHE Line,那么模相同的内存 data block 会映射到同一个 CACHE Line 里. 例如上图的案例中,内存 data block 的长度和 CACHE LINE 的长度都是 64Bytes,内存 data block 0x0000000 只能被加载到 CACHE Line0, 0x00000008 只能加载到 CACHE Line1,以此类推,由于 0x00000030 的模数与 0x00000000 相同,那么其也映射到 CACHE Line0 上。相比其他的 CACHE 设计方案,直接映射有自己的简单的优点,但缺点也很明显:

- 优点: 硬件设计简单、成本低

- 缺点: 灵活性差,内存 data block 只能映射到固定的 CACHE Line 上,很容易与同一 CACHE Line 的 data block 冲突,从而引起Cache 颠簸. CACHE 的容量比较大才能显示直接映射的优势.

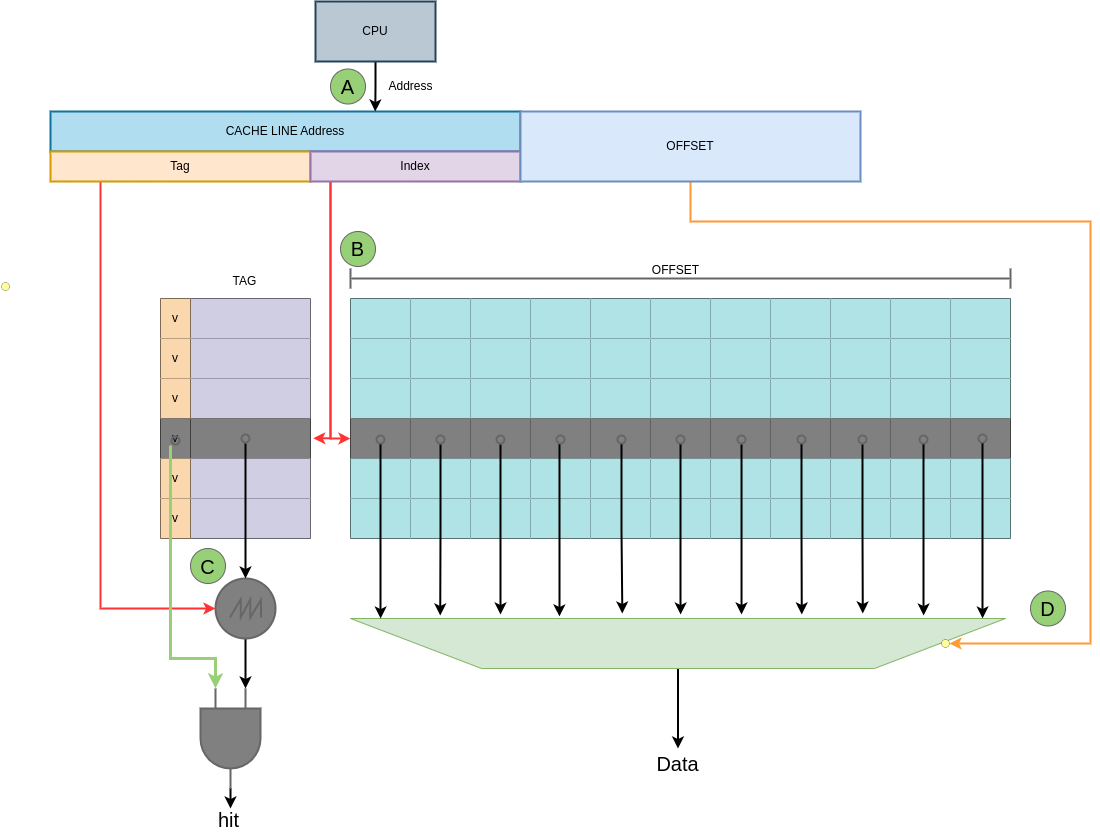

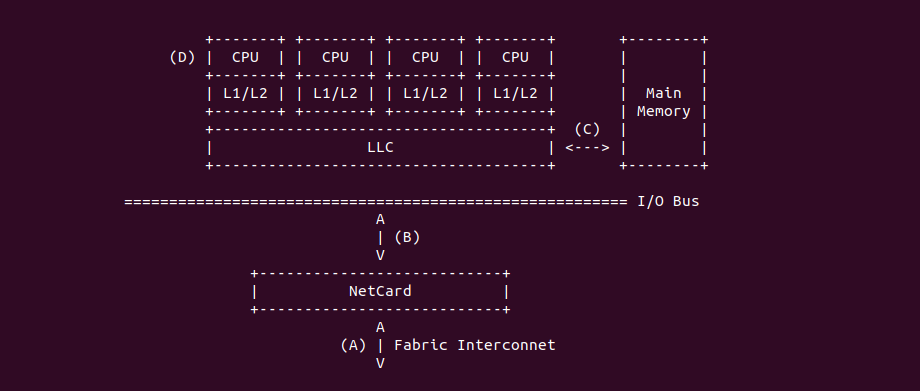

直接映射硬件设计简单, CACHE 内部在一个平面内将所有的 CACHE LINE 按顺序依次排列组成,每一行就是一个 CACHE Line,每个 CACHE Line 包含了两部分,TAG 和 OFFSET,其中 TAG 部分还包含了一个 valid 位,Valid 位置位时表示 CACHE Line 维护的数据有效, 反之该位清零时表示 CACHE Line 维护的数据无效. 硬件处理过程如上图:

- A: CPU 生成需要访问地址,地址被划分成 3 个部分: Tag、Index 和 Offset

- B: CACHE 从访问地址的 Index 部分在 CACHE 中找到对应的 CACHE Line

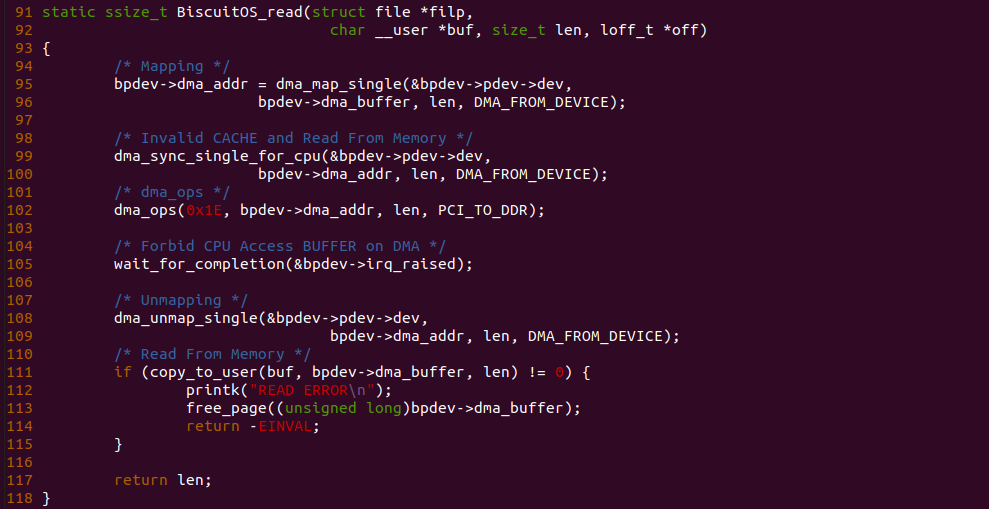

- C: 将 CACHE Line 的 Tag 部分与访问地址的 Tag 部分进行比较,当匹配上且 CACHE Line Tag 的 valid 位置位,那么命中(Cache hit); 反之如果 valid 位清零或者 Tag 字段不匹配,那么缺失(Cache miss).

- D: 当命中之后,CACHE 根据访问地址的 Offset 字段从 CACHE Line 中获得最终的值.

全相联映射

全相联映射(Full-associative) 指的是内存中的 data block 可以映射到任意 CACHE Line. 例如上图的案例中内存 0x00000000 可以映射到任一 CACHE Line 上,0x00000008 也可以映射到任一个 CACHE Line. 由于内存 data block 可以映射到任一 CACHE Line,因此 CACHE 需要花费更多的时间或者更多的资源去查找对应的 CACHE Line 中是否包含所需的数据.

- 优点: 灵活性好,CACHE 只要有空闲的 CACHE Line 就可以加载内存 data block.

- 缺点: 利用率不高,因为存在一个 m 位的标记,使 CACHE Line 中包含一些对存储无用的信息. 速度慢、硬件成本高,每次访问 CACHE 需要依次遍历,直到命中才能确认 data block 是否在 CACHE 中.

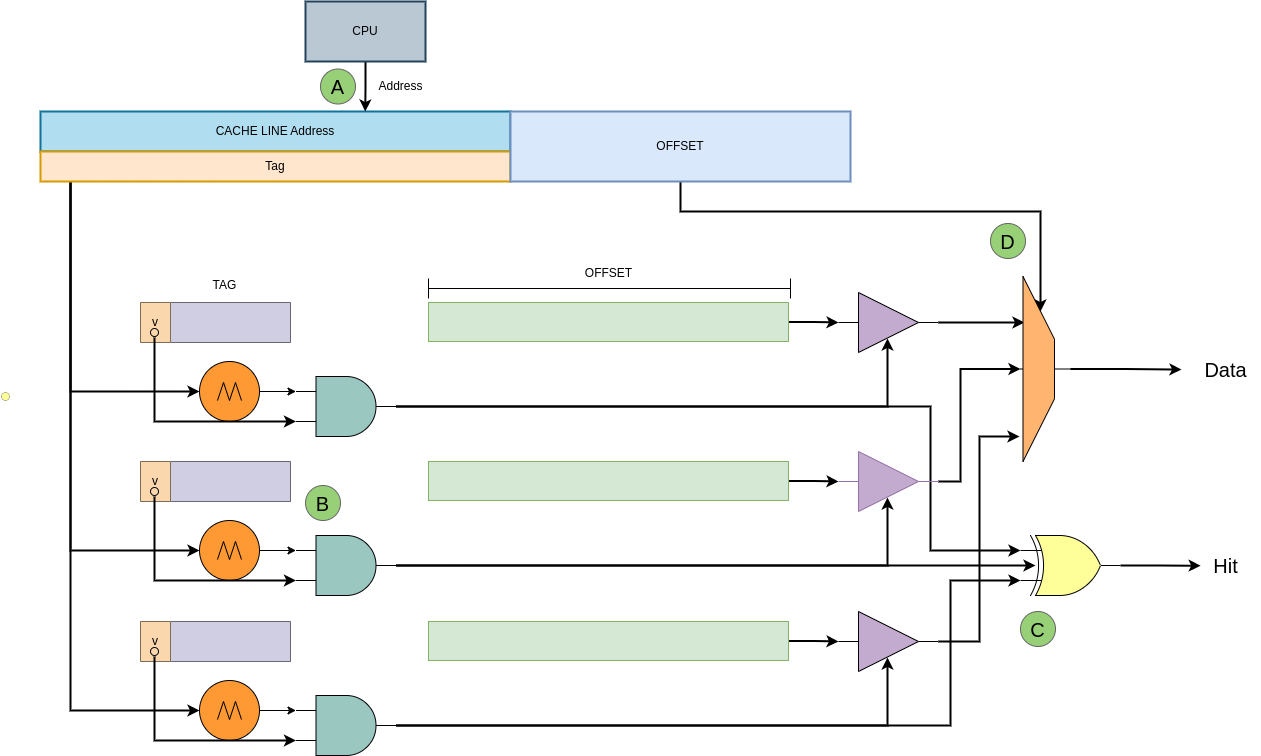

全相联映射的硬件相对复杂,CACHE 内部在一个平面内将所有的 CACHE LINE 按顺序依次排列,每个 CACHE Line 都存在一个比较模块,用于比较 CACHE Line 的 Tag 部分,其中 TAG 部分还包含了一个 valid 位,Valid 位置位时表示 CACHE Line 维护的数据有效, 反之该位清零时表示 CACHE Line 维护的数据无效. 全相联结构的 CACHE 有着最大的灵活性,因此缺失(Cache miss)率是最低的,但从硬件结构来看,由于有着大量的内容需要进行比较,它的延迟也是最大的,因此一般这种结构的 CACHE 都不会有很大的容量. 硬件处理过程如上图:

- A: CPU 生成需要访问地址,地址被划分成 2 个部分: Tag 和 Offset

- B: CACHE 从访问地址的 Tag 部分依次与 CACHE Line 的 Tag 部分进行比较

- C: 当匹配上且 CACHE Line Tag 的 valid 位置位,那么命中(Cache hit); 反之如果 valid 位清零或者 Tag 字段不匹配,那么缺失(Cache miss).

- D: 当命中之后,CACHE 根据访问地址的 Offset 字段从 CACHE Line 中获得最终的值.

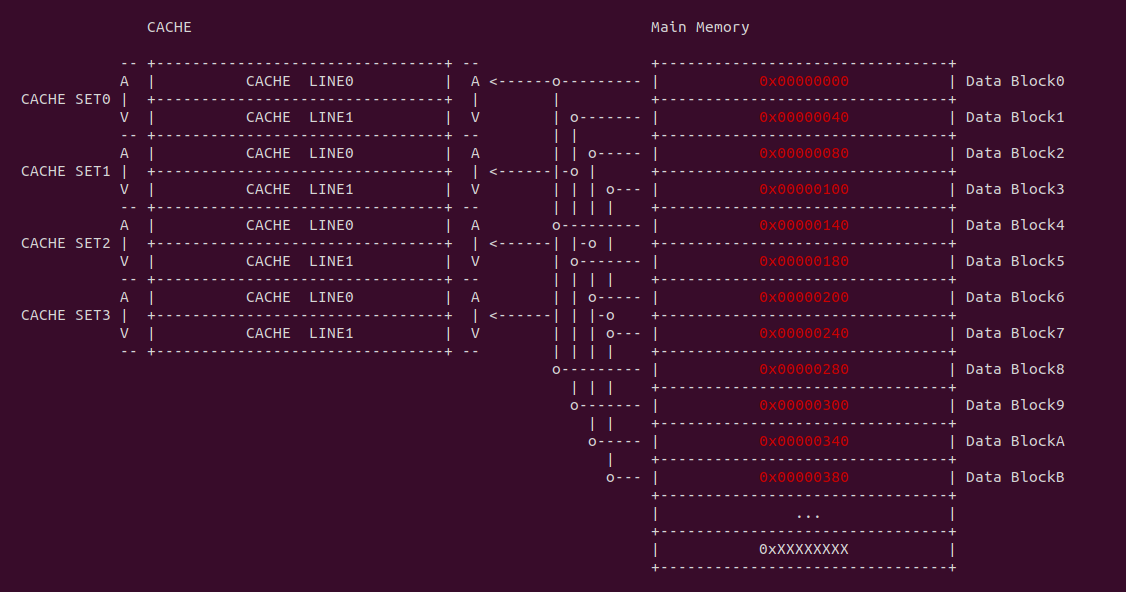

组相联映射

组相联映射(Set-associative) 是直接映射和全映射的折中方案,将多个 CACHE Line 组成一个组称为 CACHE Set,同样将多个 Data block 组成一个组称为 Data Set,每个 Data Set 按直接映射的方式映射到指定的 CACHE Set. Data Set 内的任意 Data block 可以映射到 CACHE Set 中任意 CACHE Line. 对于组相联映射的 CACHE 来说,一个 Data block 可以被加载到 CACHE Set 的 N 个 CACHE Line,那么称这个 CACHE 是 N 路组相联的 CACHE(n-way set-associative Cache). 相比其他两种映射方式,组相联映射组内具有一定的灵活性,而且组内行数较少,比较的硬件电路比全相联方式简单,并且空间利用率比直接映射方式高.

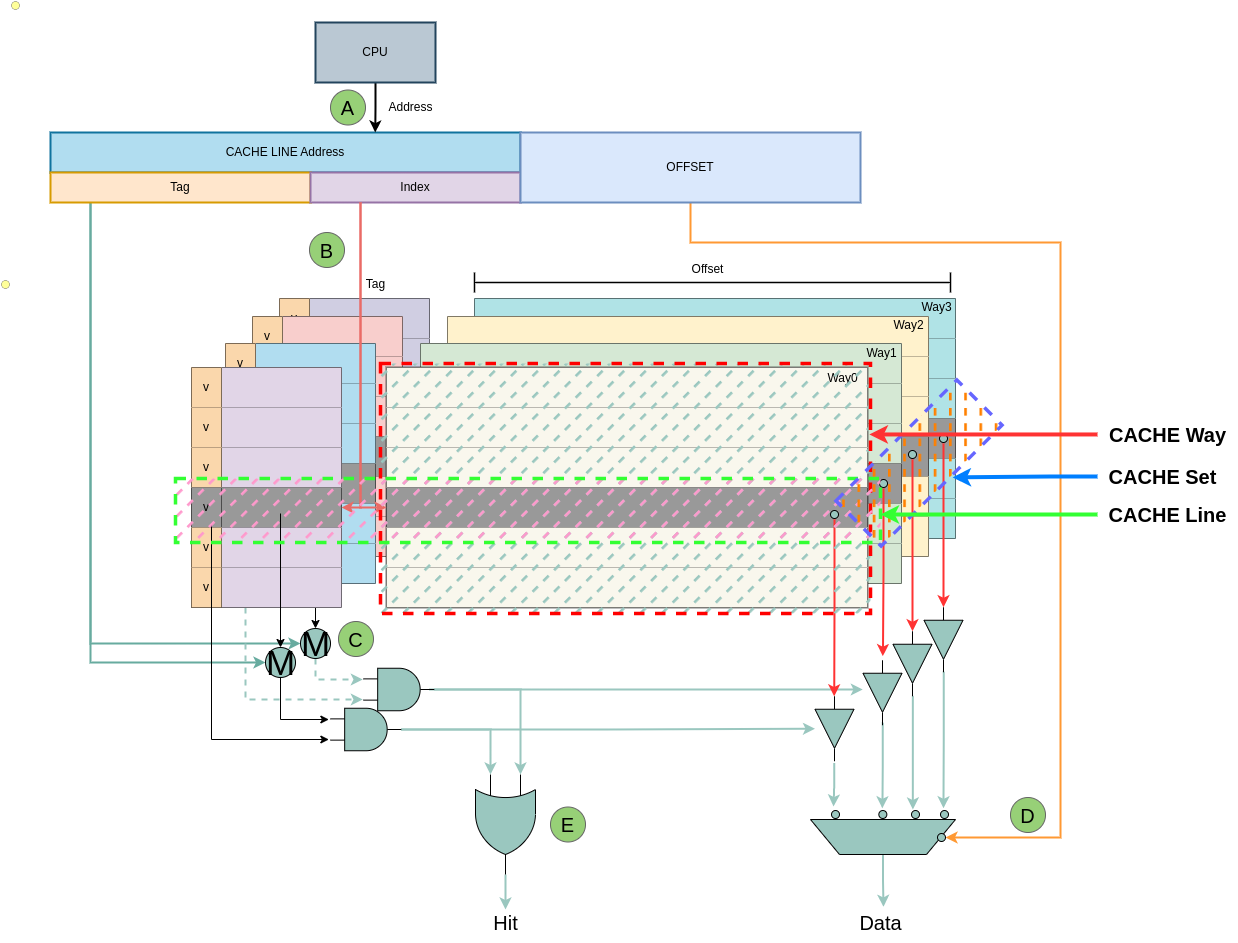

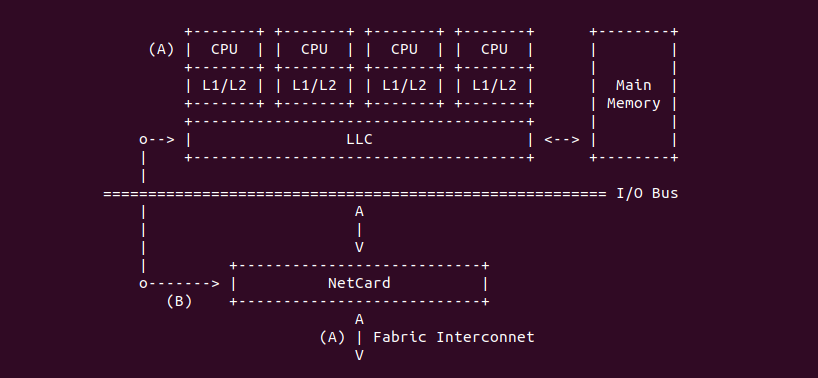

组相联映射的硬件是一个立体的结构,每个 CACHE Way 就是一个垂直平面,多个 CACHE Way 组成了一个立体的存储结构,那么一个 CACHE Set 就是在多个 CACHE Way 组成的立体结构上进行一次横切,那么同一个 Data Set 里面的 Data block 可以存储在横切之后 CACHE Set 里任意一个 CACHE Line 里. 硬件处理过程如上图:

- A: CPU 生成需要访问地址,地址被划分成 3 个部分: Tag、Index 和 Offset

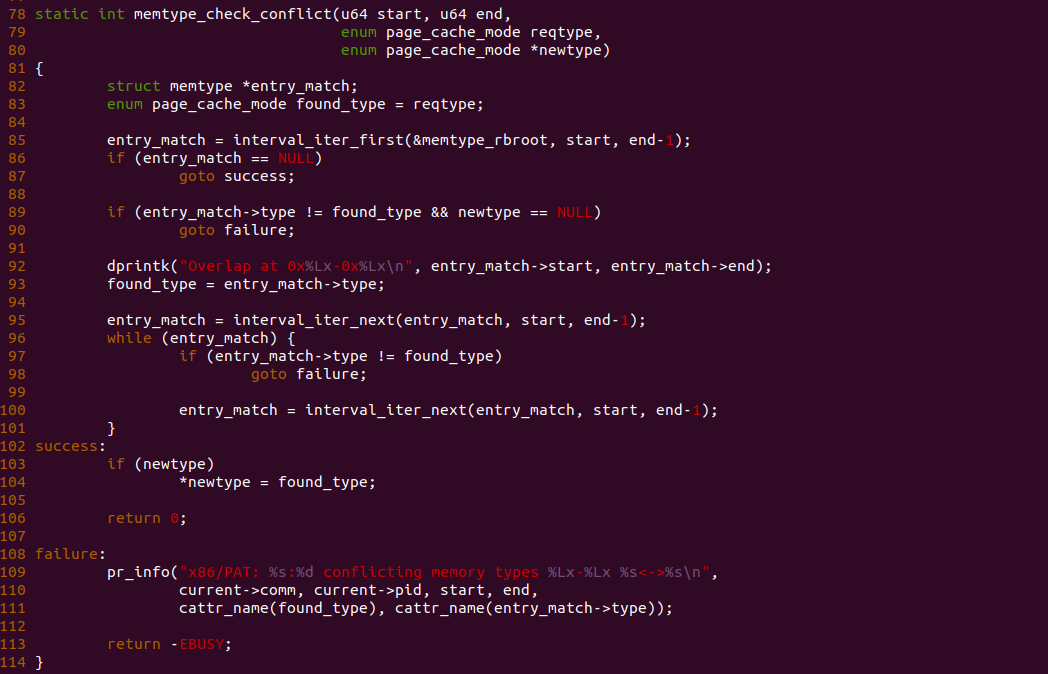

- B: CACHE 从访问地址的 index 部分在 CACHE 中找到对应的 CACHE Set.

- C: 依次将 CACHE Set 里的 CACHE Line 的 Tag 部分与访问地址的 Tag 部分进行比较,如果匹配上且 Tag 的 valid 位置位,那么命中(Cache hit); 反之如果 valid 位清零或者 Tag 字段没有匹配,那么缺失(Cache miss).

- D: 当命中之后,CACHE 根据访问地址的 Offset 字段从 CACHE Line 中获得最终的值.

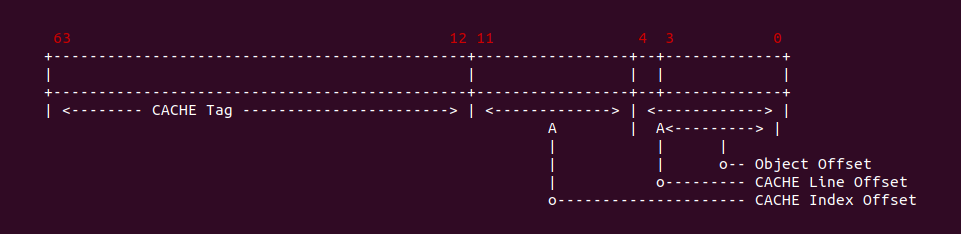

CACHE Tag and Index

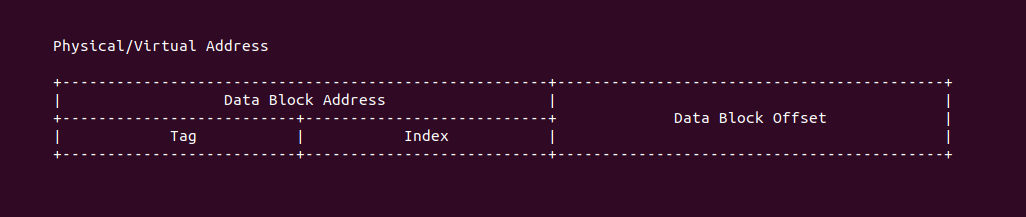

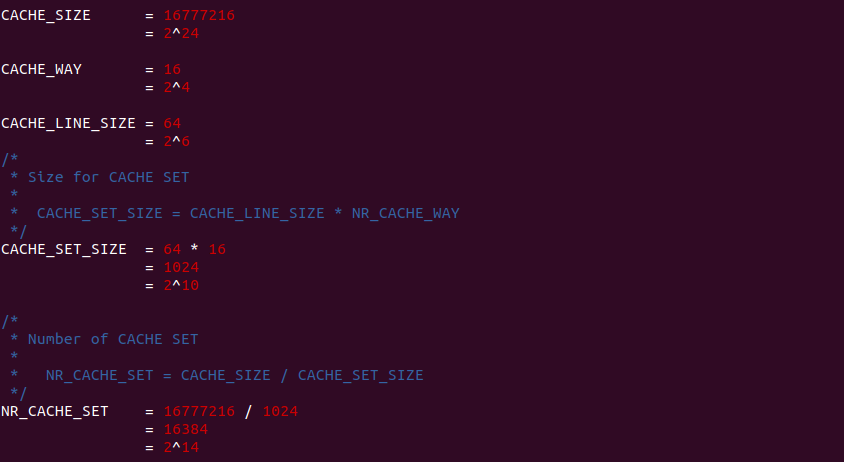

对于一段索引 CACHE 的内存地址(可以是虚拟机地址或者物理地址),其分为以上三部分: Tag、Index 和 Offset. 三者组合可以在 CACHE 中定位唯一的 CACHE Line,其中 Index 字段用于定位 CACHE Set,Tag 用于在 CACHE Set 中定位到指定的 CACHE Line,Offset 用于在 CACHE Line 的数据域定位指定的数据.

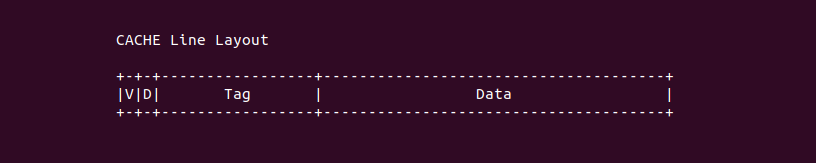

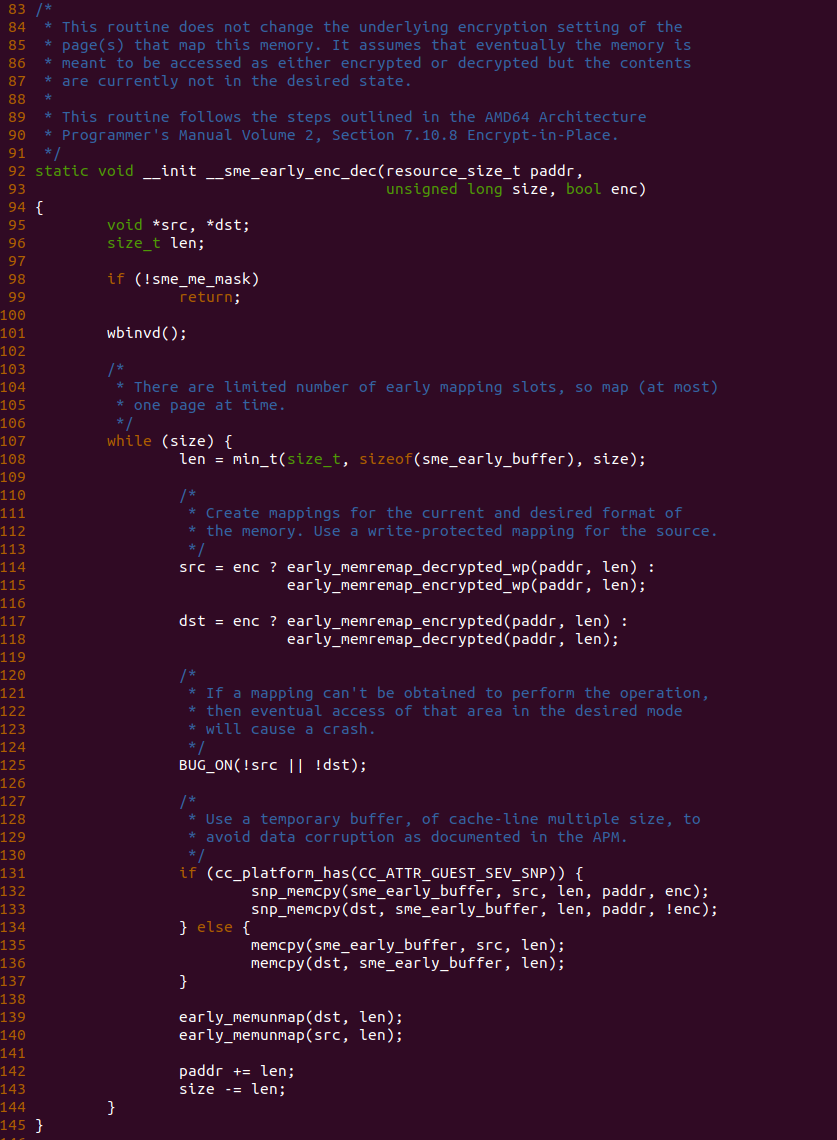

CACHE Line 内部结构如上图,其由 Tag、Flags 和数据域组成。Tag 部分用于在内存地址 Index 找到 CACHE Set 的情况下,与内存地址 Tag 相比较以此找到指定的 CACHE Line; Flags 字段包括 Valid 位,在数据 CACHE 中还包括 Dirty 位,Valid 位用于指明 CACHE Line 是否有效,Dirty 位则表明 CACHE Line 是否包含脏数据; Data 数据域包含了从 Data Block 取来的 CACHE Line Size 字节的数据.

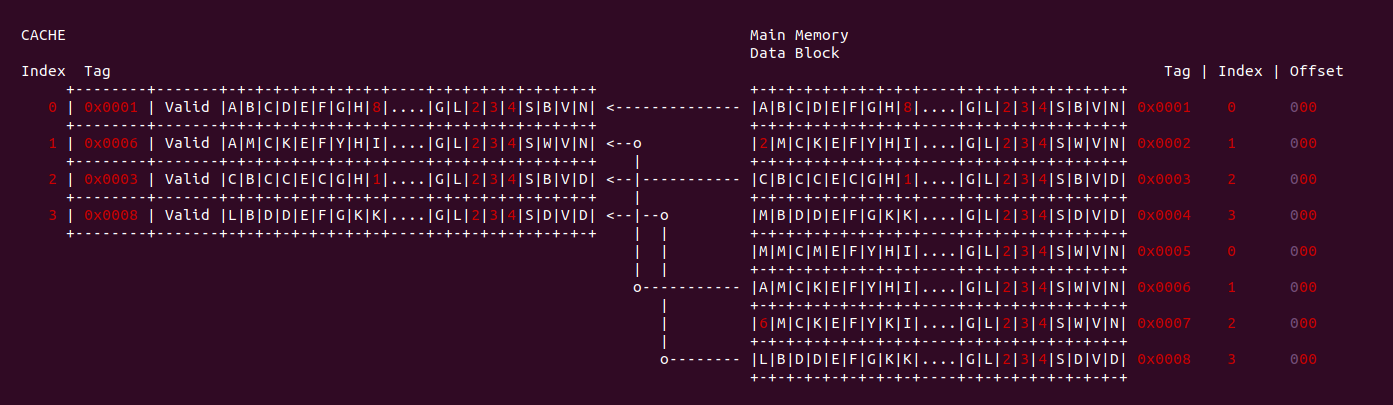

内存 Data Block 首次加载到 CACHE 时,先根据内存地址的 Index 字段在 CACHE 中找到对应的 CACHE Set,然后将 CACHE Set 中找到一个合适的 CACHE Line 将内存地址 Tag 字段存入 CACHE Line 的 Tag 字段,然后将内存 Data Block 的数据存储到 CACHE Line 的 Data 区域. 例如 Data Block 的地址为 0x00061000, 其 Index 为 1, 那么其被加载到 CACHE 时其会选择 CACHE Set 为 1,由于案例中 CACHE Set 只包含一个 CACHE Line,那么 Data Block 加载到 CACHE Line1 里,此时 CACHE 将 Data Block 的 Tag 字段 0x0006 存储到 CACHE Line1 的 Tag 字段,并将 Data Block 的数据加载到 CACHE Line1 的 Data 域. 以上便是一个最简单的 CACHE Load 内存的过程.

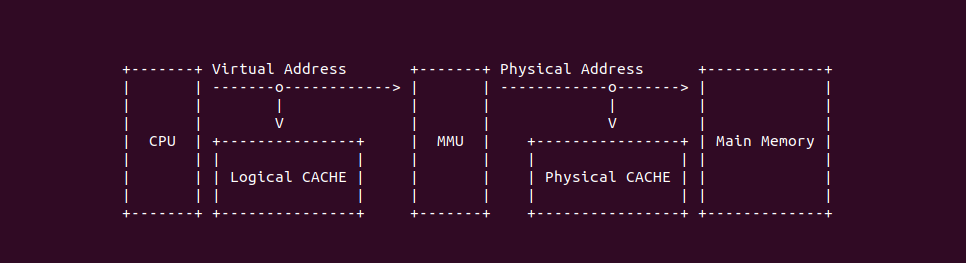

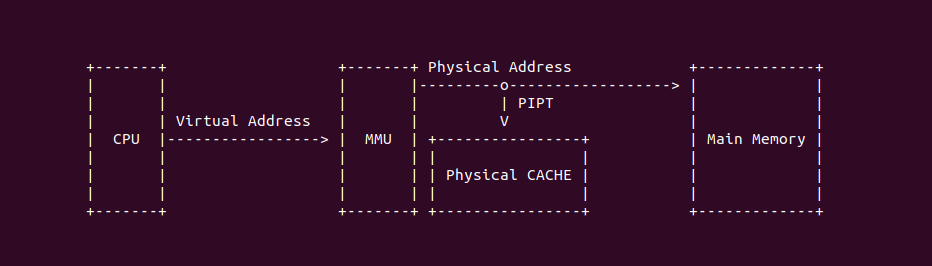

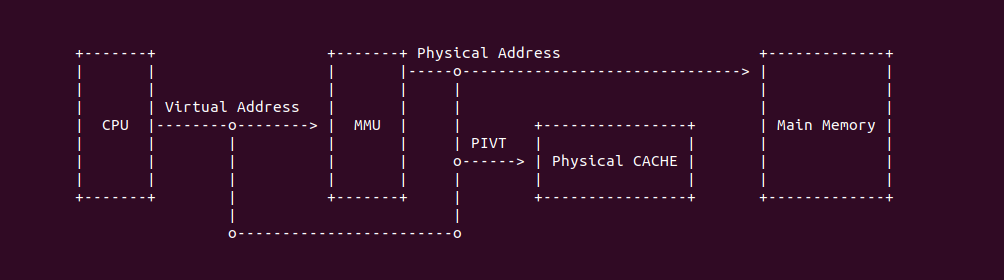

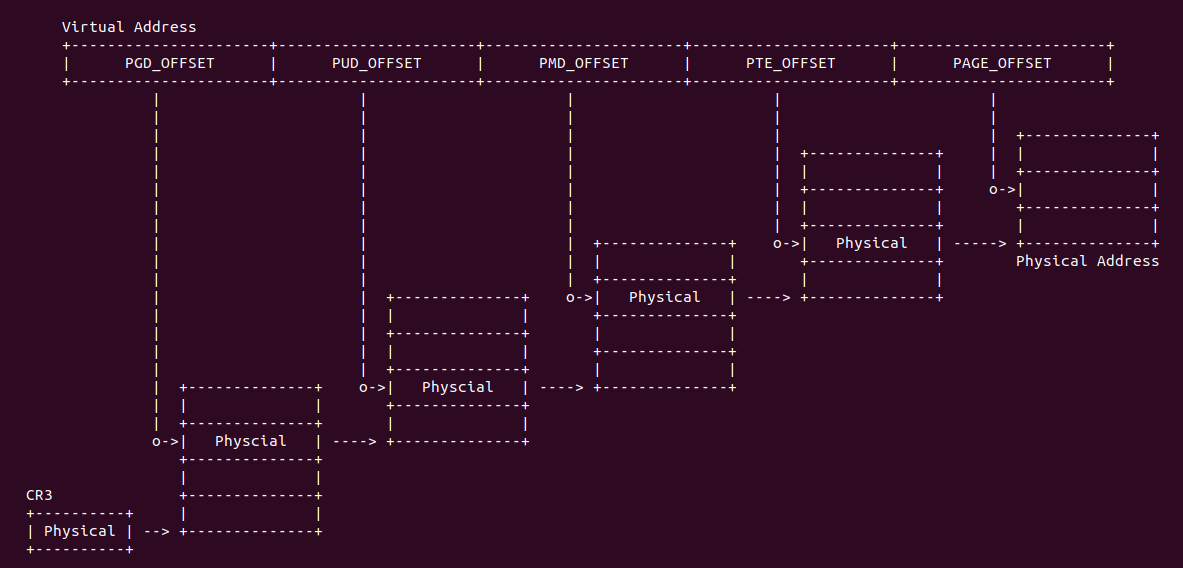

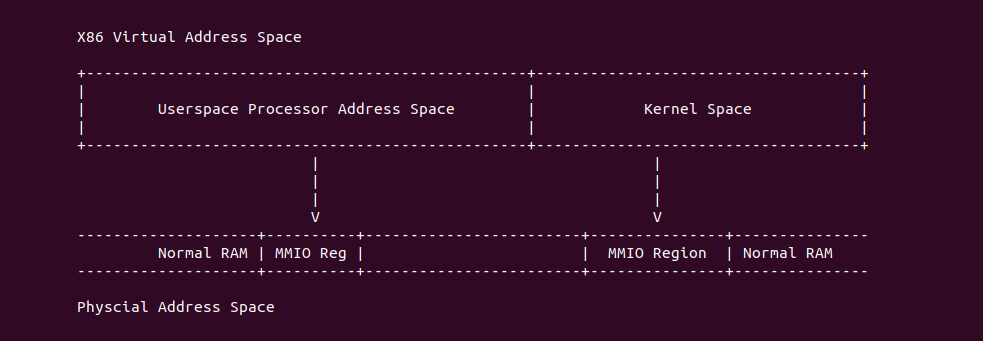

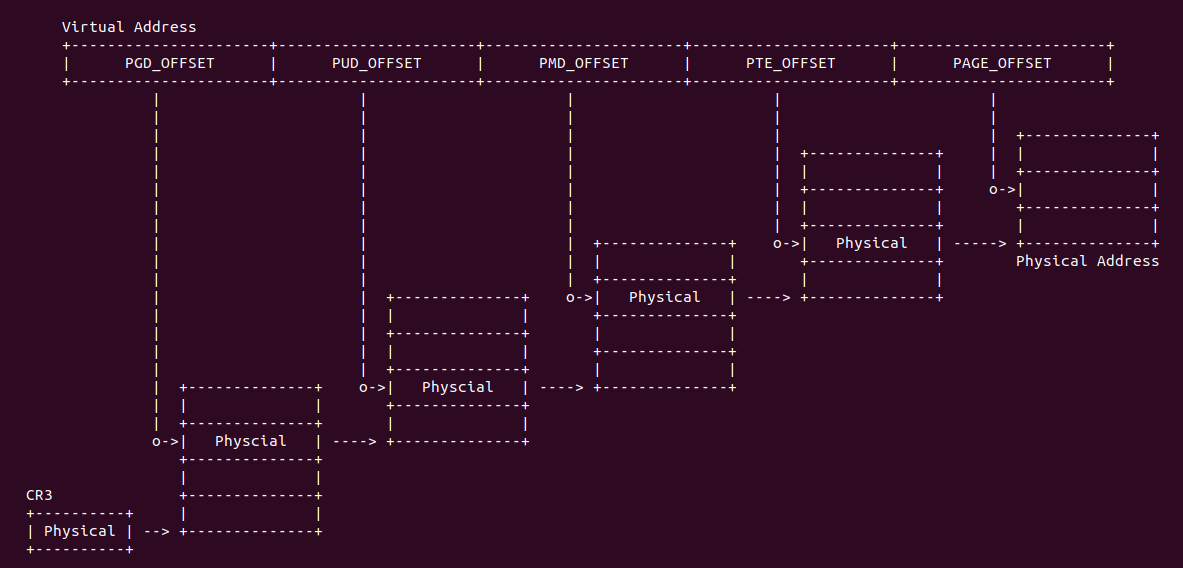

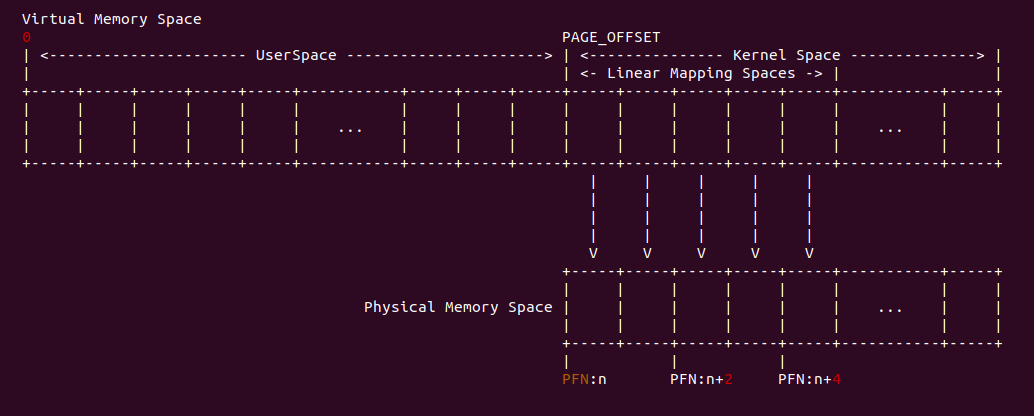

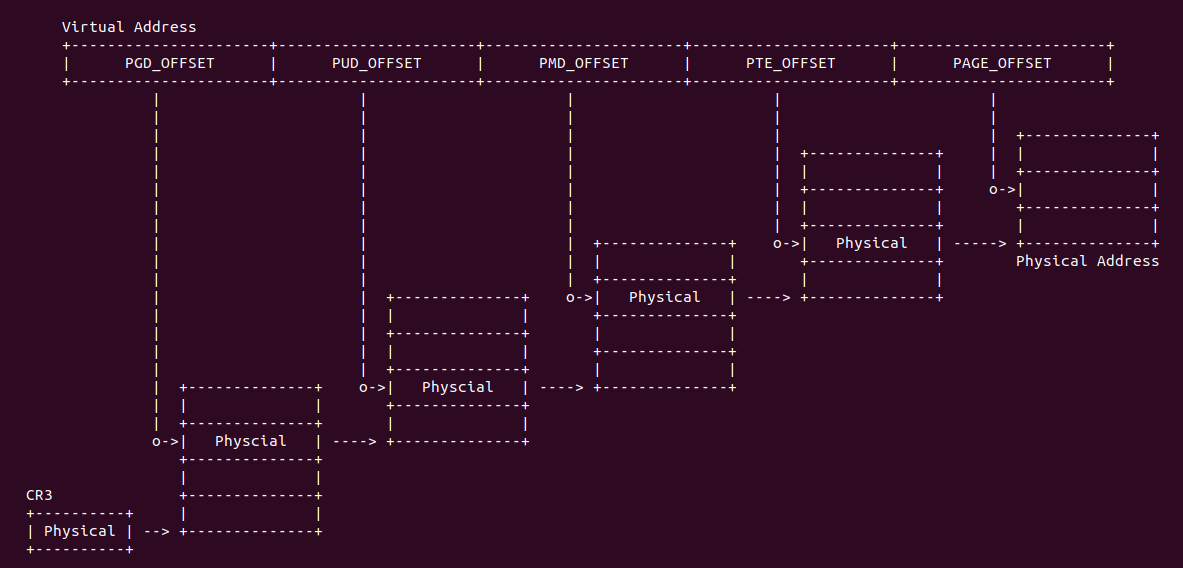

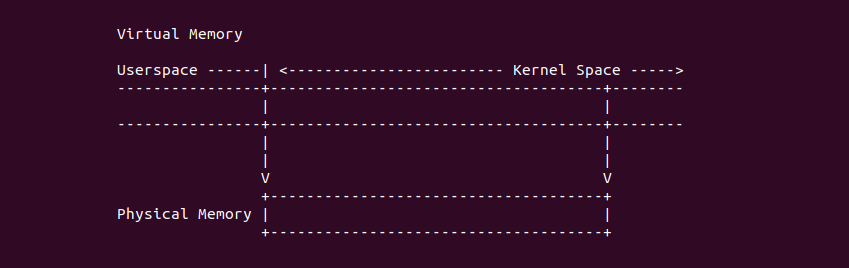

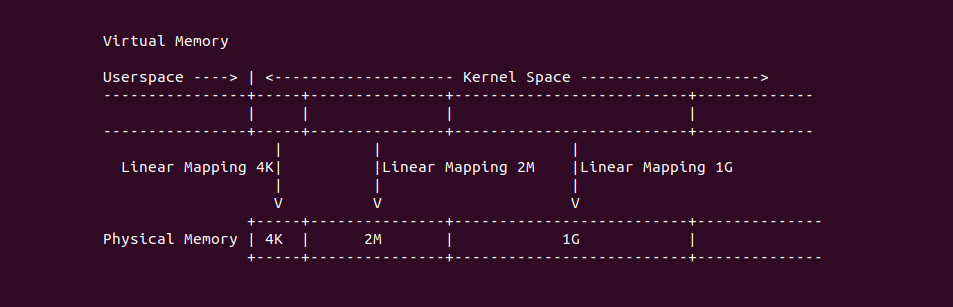

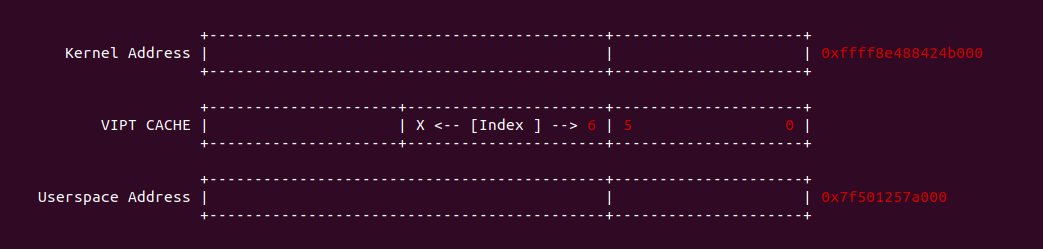

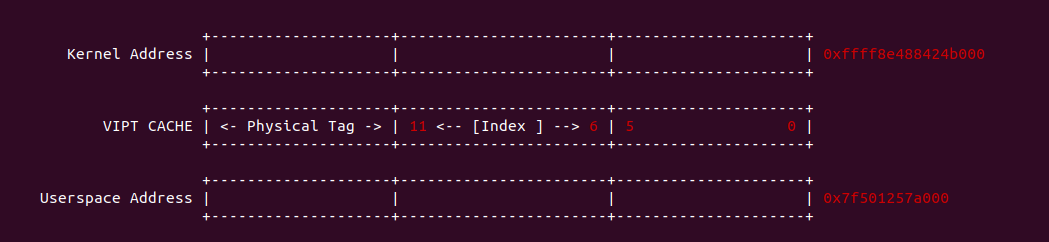

在开启分页之后,CPU 直接使用的是虚拟地址,但索引 CACHE 的内存地址可以是物理地址,也可以是虚拟地址,存在这样的逻辑是因为 CACHE 的位置决定的。当 CACHE 位于 CPU 和 MMU 之间,那么称为逻辑 CACHE,可以使用虚拟地址的 Index 索引 CACHE Set,并称虚拟地址的 Index 为 VI(Virtual Index); 当 CACHE 位于 MMU 和主存之间,那么称为 物理 CACHE, 可以使用物理地址的 Index 索引 CACHE Set,并称物理地址的 Index 为 PI(Physical Index). 另外需要使用物理地址 Tag 确认 CACHE Line 的 Tag,那么物理地址 Tag 为 PT(Physical Tag), 同理需要使用虚拟地址 Tag 确认 CACHE Line 的 Tag,那么虚拟地址 Tag 称为 VT(Virtual Tag).

CACHE 歧义(Ambiguity)

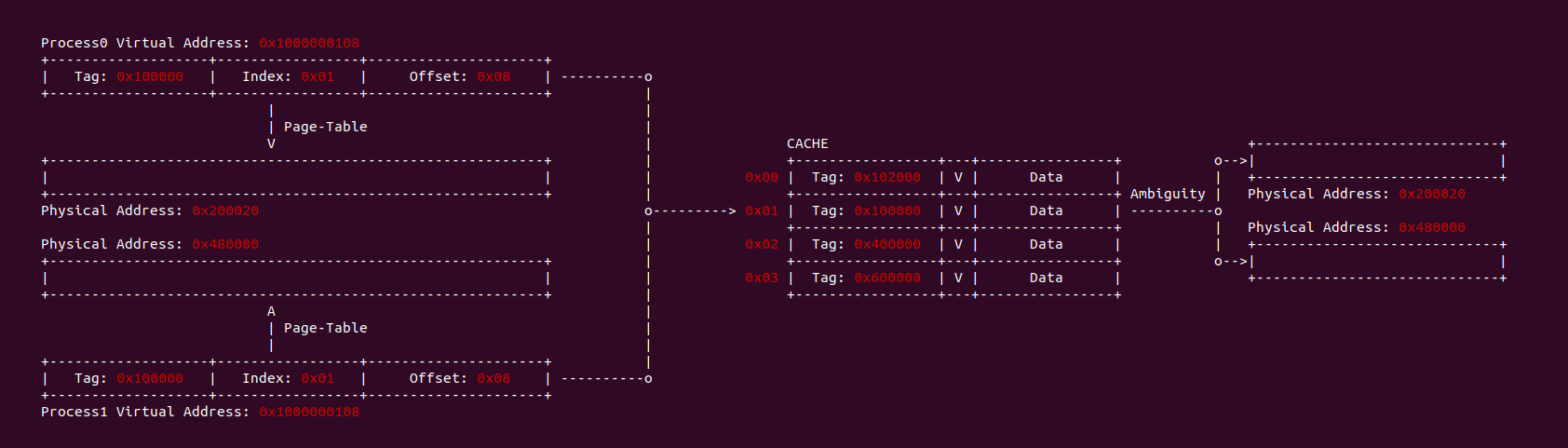

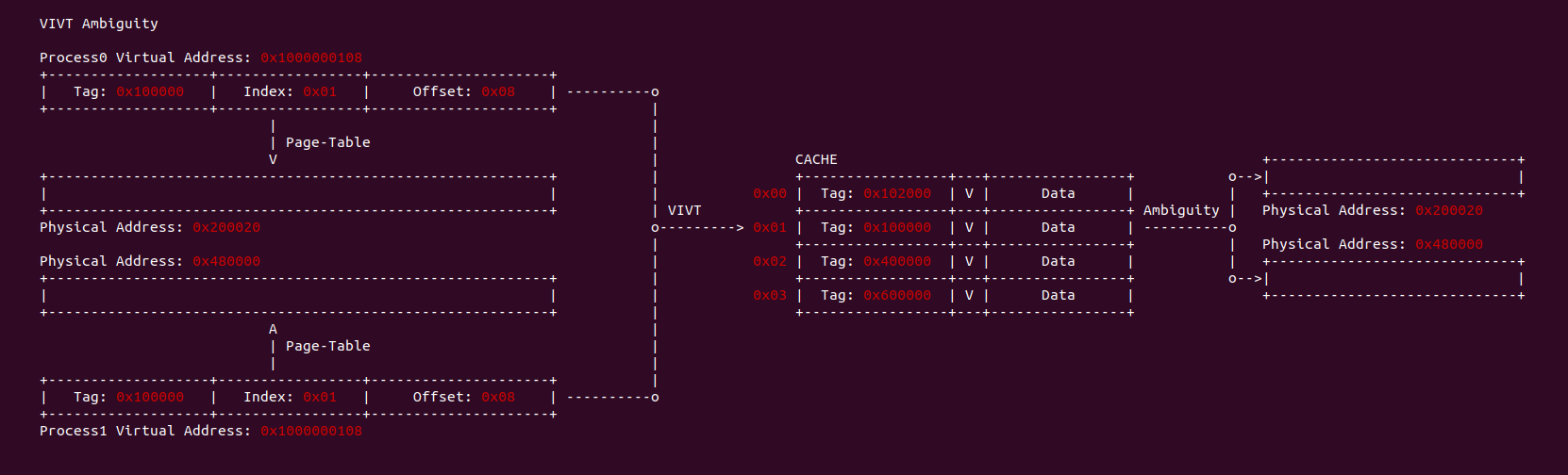

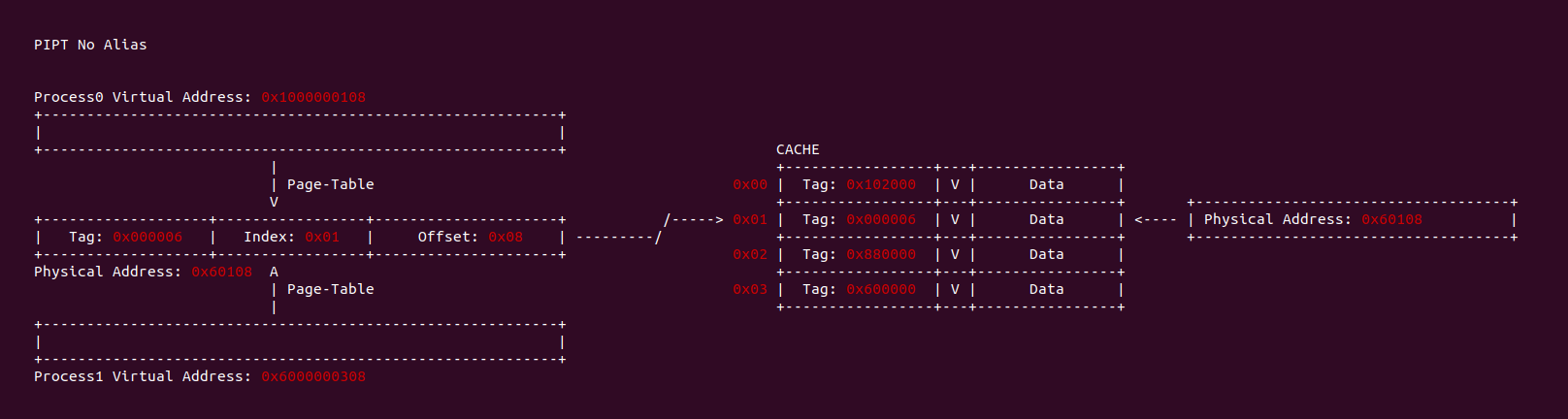

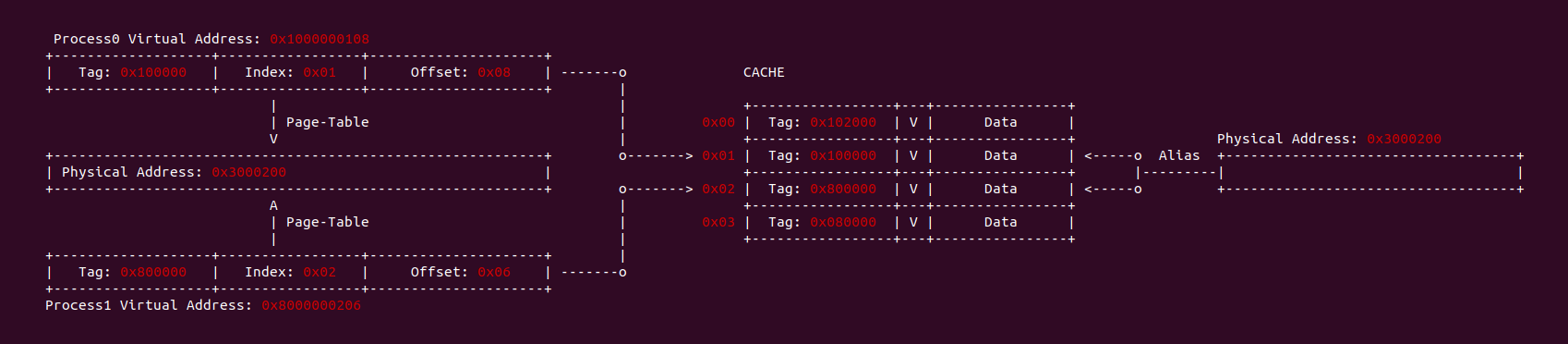

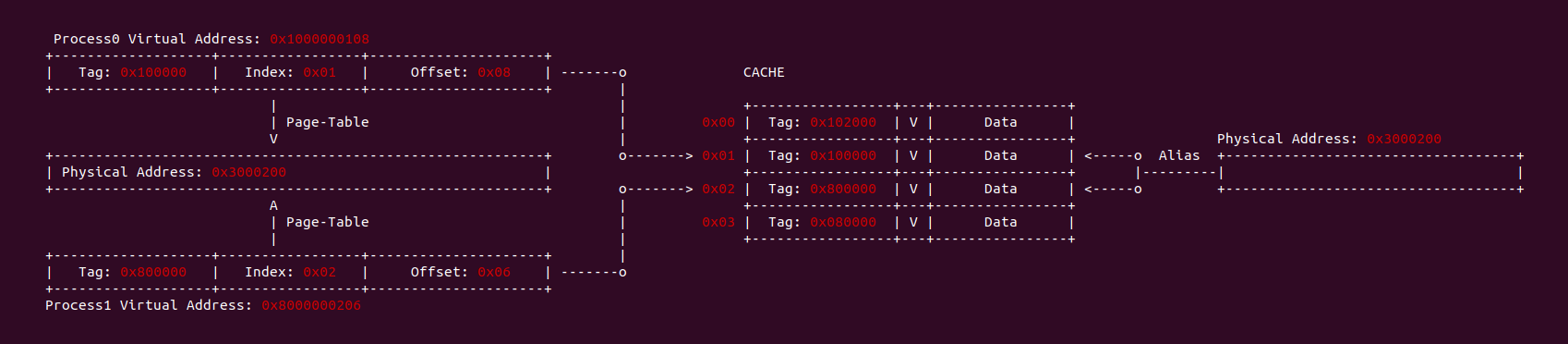

当 CACHE 控制器使用虚拟地址索引 CACHE Line,即使用 VIVT(Virtual Index Virtual Tag),当两个进程相同的虚拟地址映射到不同的物理地址,例如上图中进程 0 的虚拟地址 0x1000000108 映射了物理地址 0x200020, 而进程 1 同样的虚拟地址 0x1000000108 映射了物理地址 0x300020. 由于 CACHE 控制器使用了虚拟地址 Index 所有 CACHE Set,那么两个虚拟地址的 Index 都是 0x01, 并且使用虚拟地址的 Tag 确认 CACHE Line 的 Tag,此时两个虚拟地址都有相同的 Tag,因此两个进程的虚拟地址在 CACHE 中找到了同一个 CACHE Line,换个角度就是同一个 CACHE Line 映射不同的物理地址, 称这种现象为 CACHE 歧义(Ambiguity). 内核通过如下方法避免歧义:

- 进程切换时 flush cache,并使主存 Data Block 有效。针对 WriteBack 高速缓存,首先应使主存数据有效,保证已经修改数据 CACHE Line 已经写入主存,避免修改的数据丢失.

- 进程切换时 flush cache,并使 CACHE Line 无效,保证切换之后的进程不会错误命中切换之前进程的 CACHE Line.

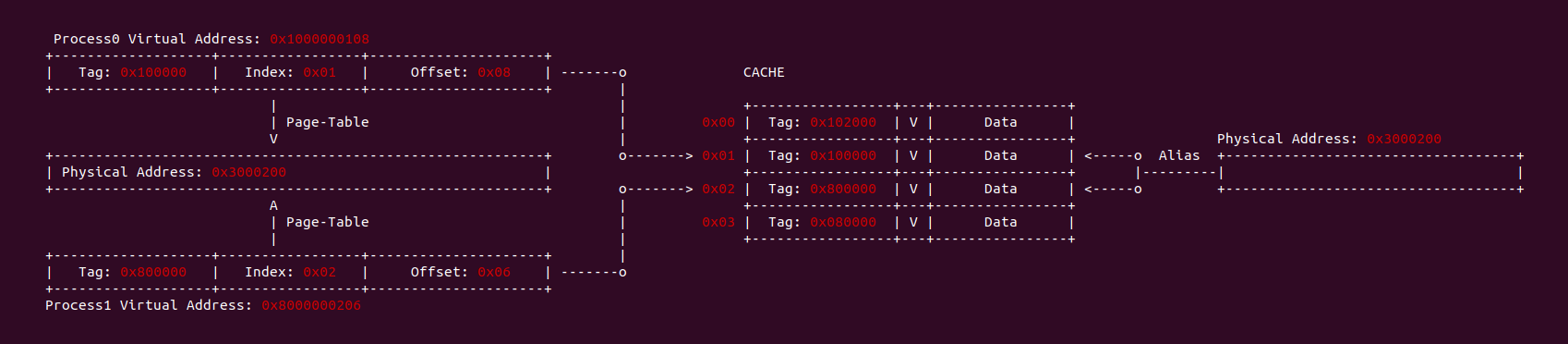

CACHE 别名(Alias)

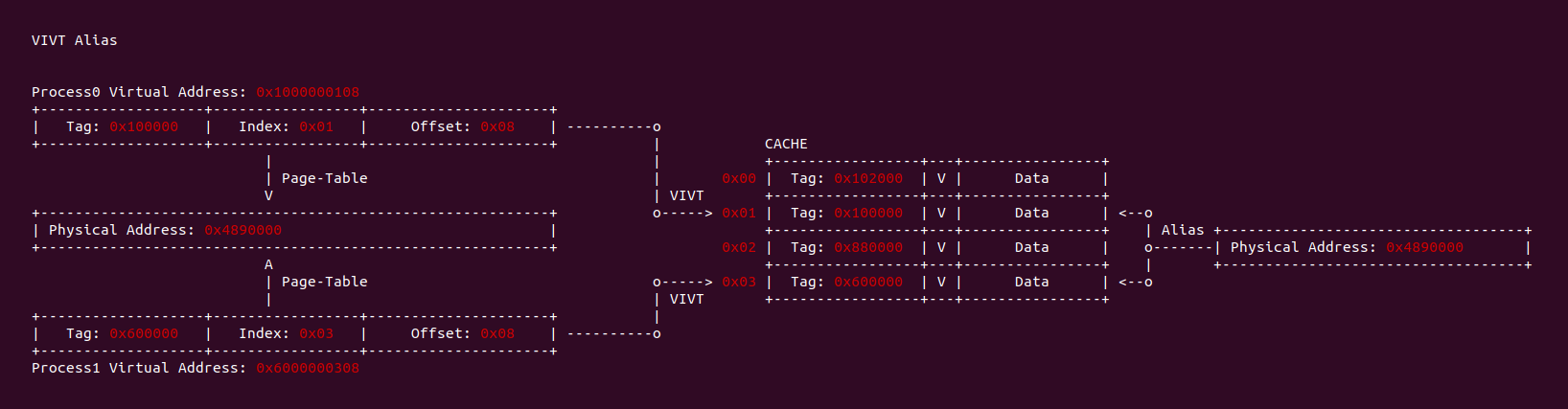

当 CACHE 控制器使用虚拟地址索引 CACHE Line,即使用 VIVT(Virtual Index Virtual Tag). 当两个进程不同的虚拟地址映射到同一个物理地址上,例如上图进程 0 的虚拟地址 0x1000000108 和进程 1 的虚拟地址 0x8000000206 都映射到了物理地址 0x3000200,由于 CACHE 控制器使用 VIVT,那么此时就会出现两个虚拟地址会索引到不同 CACHE Set 的 CACHE Line 上,换个角度就是一个物理地址被缓存到不同的 CACHE Line 里,称这种现象为 CACHE 别名(Alias). 别名问题会导致 CACHE 一致性问题(后面会讨论).

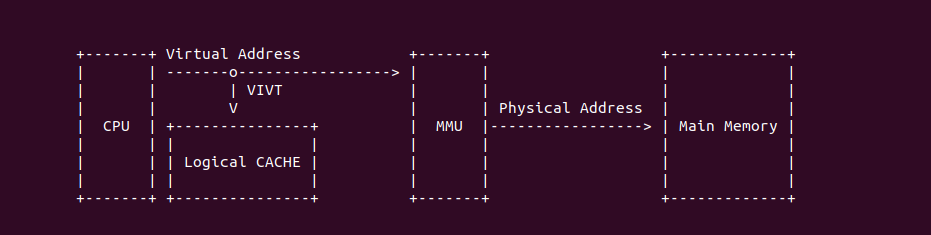

VIVT

VIVT(Virtual Index Virtual Tag) 指的是虚拟 CACHE 控制器通过虚拟地址提供的 Tag 和 Index 索引 CACHE Line. VIVT 不需要经过 MMU 翻译,具有很小的延时,但会引起别名和歧义问题.

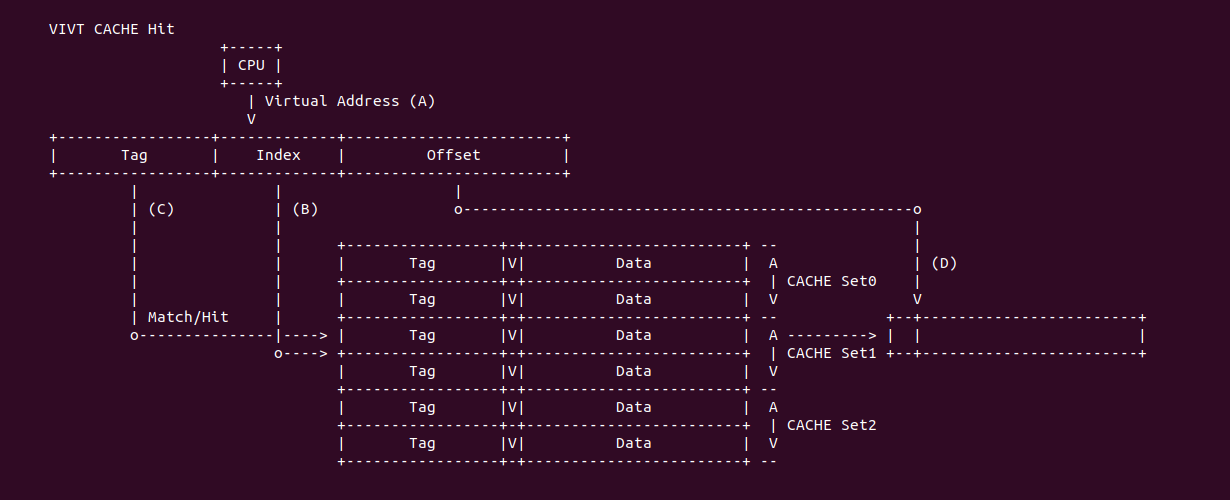

VIVT CACHE Hit: 当 CACHE 控制器使用 VIVT 索引 CACHE Line:

- (A) CPU 产生的虚拟地址可以直接传递给 CACHE 控制器进行索引

- (B) CACHE 控制器从虚拟地址中提取 Index 字段,Index 可以选择指定的 CACHE Set,此时选中 CACHE Set1,其组内包含了两个 CACHE Line

- (C) CACHE 控制器从虚拟地址中提取 Tag 字段,与 CACHE Set1 的所有 CACHE Line 的 Tag 字段进行比较,一旦 Tag 匹配,并且 Valid 字段有效,那么找到指定的 CACHE Line.

- (D) CACHE 控制器从 CACHE Line 中区域 Data 区域,并从虚拟地址提取 Offset 字段,最终在 CACHE Line 的 Data 区域中读取指定的数据.

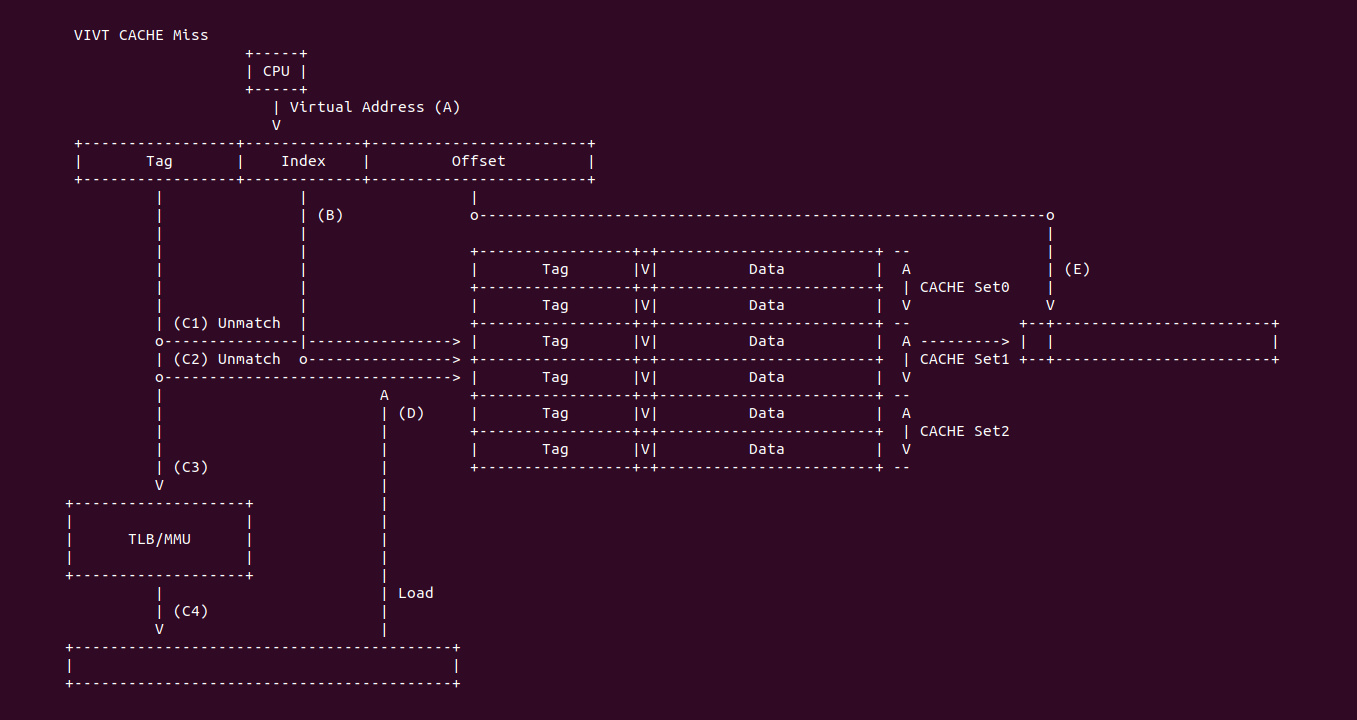

VIVT CACHE Miss: 当 CACHE 控制器使用 VIVT 索引 CACHE Line:

- (A) CPU 产生的虚拟地址可以直接传递给 CACHE 控制器进行索引

- (B) CACHE 控制器从虚拟地址中提取 Index 字段,Index 可以选择指定的 CACHE Set,此时选中的 CACHE Set1,其组内包含了两个 CACHE Line.

- (C1) CACHE 控制器从虚拟地址中提取 Tag 字段,与 CACHE Set1 的第一个 CACHE Line 的 Tag 字段进行比较,发现不匹配

- (C2) CACHE 控制器继续与 CACHE Set1 剩下的 CACHE Line Tag 字段进行比较,发现还是不匹配,那么 CACHE 控制器认为发送 CACHE Miss

- (C3) CACHE Miss 之后 CACHE 控制器将虚拟地址传递给 TLB 或者 MMU 查询虚拟地址对应的物理内存

- (C4) 系统从 TLB 或者 MMU 中找到了虚拟地址对应的物理内存(可能也找不到)

- (D) CACHE 控制器根据替换算法将 CACHE Set1 中指定的 CACHE Line 刷出,然后将找到的物理内存 Data Block 加载到该 CACHE Line,并更新 Tag 和 Valid 字段

- (E) CACHE 控制器继续将 CACHE Line 的 Data 域取出,然后配合虚拟地址的 Offset 域找到最终的数据.

VIVT 优缺点: 通过上面对 VIVT Hit 和 Miss 场景的分析,VIVI 模式下 CPU 不需要将虚拟地址转换成物理地址就可以在 CACHE 中找到 CACHE Line,在一定程度上提升了 CACHE 的速度,因为访问虚拟地址转换成物理地址可能需要几十到几百个周期,只有在 CACHE Miss 的时候才会发送虚拟地址到物理地址的转换,硬件设计上更加简单. 但 VIVT 模式容易引入歧义和别名问题, 具体如下:

在不同的进程地址空间里,虚拟地址虽然相同,但映射到不同的物理内存上,如果 CACHE 控制器使用虚拟地址的 Index 和 Tag 查找 CACHE Line,那么会出现同一个 CACHE Line 会映射不同的物理地址,这就是 VIVT 的歧义问题. 为了保证系统的正确工作,操作系统需要负责避免歧义出现,可以通过按需清除 CACHE Line,或者为每一个进程的地址空间添加标记(PCID/ASID),当进程切换时刷掉指定的 CACHE Line, 不过这样做会导致进程调度回来时出现大量的 CACHE Miss,影响程序的性能.

同样是不同进程不同的虚拟地址同时映射到同一个物理地址上,如果 CACHE 控制器使用虚拟地址的 Index 和 Tag 查找 CACHE Line,那么不同的虚拟地址可以找到不同的 CACHE Line,但找到的 CACHE Line 却缓存了同一个物理地址的 Data Block,也就同一个物理地址会被映射到不同的 CACHE Line,这就是 VIVT 的别名问题. 该问题会引起 CACHE 的一致性问题,例如更新了存在别名 CACHE Line 的数据,那么同别名的 CACHE Line 的数据没有被更新,导致 CACHE 数据一致性问题. 同歧义问题一样,可以通过 Flush CACHE 的方式避免别名问题,也可以针对共享的数据映射相同物理地址时采用 NOCACHE 的方式,但这样会损失 CACHE 带来的性能提升.

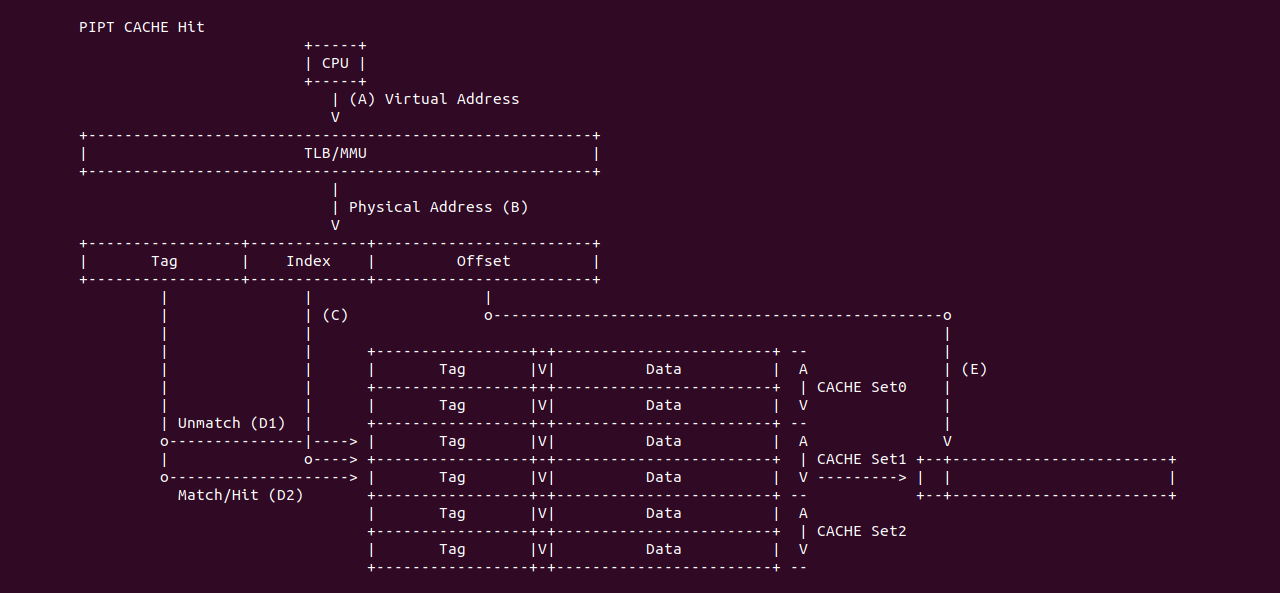

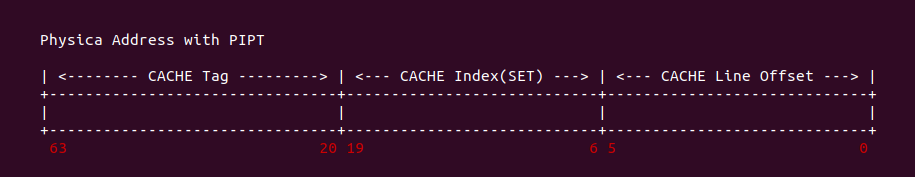

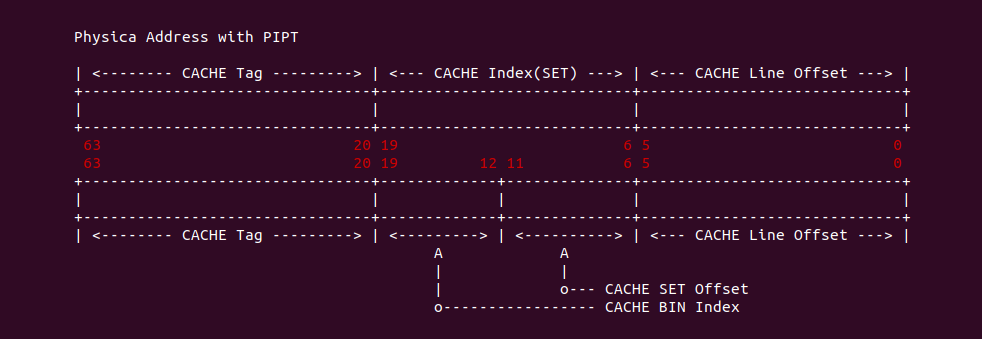

PIPT

PIPT(Physical Index Physical Tag) 指的是物理 CACHE 控制器通过物理地址提供的 Tag 和 Index 索引 CACHE Line. PIPT 需要将 CPU 产生的虚拟地址经过 TLB/MMU 翻译,获得物理地址之后才能在 CACHE 中查找 CACHE Line,因此 CACHE 的速度受限于 TLB/MMU 转换的效率. 由于物理地址的唯一性,那么 Physical Index 和 Physical Tag 也具有唯一性,那么不会引入 CACHE 别名问题和 CACHE 歧义问题.

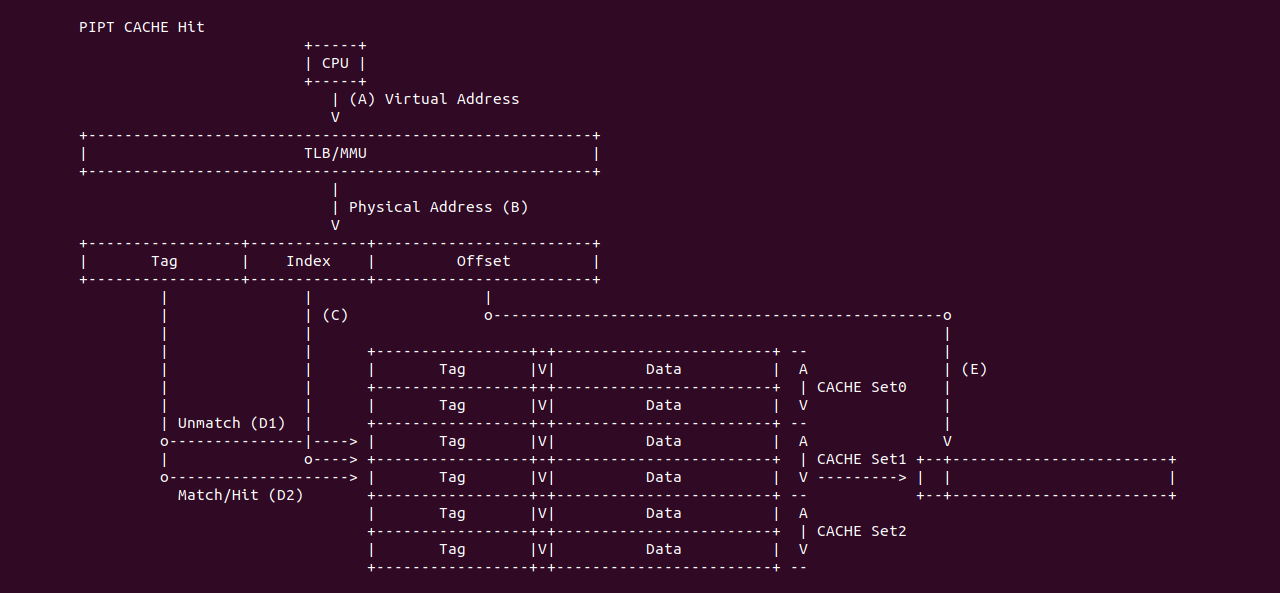

PIPT CACHE Hit: 当 CACHE 控制器使用 PIPT 索引 CACHE Line 发生 CACHE Hit:

- (A) CPU 产生的虚拟地址首先传递给 TLB/MMU 进行地址转换

- (B) TLB/MMU 将虚拟地址转换成物理地址, 并传递给 CACHE 控制器

- (C) CACHE 控制器从物理地址中提取 Index 字段,然后找到对应的 CACHE Set1,组内包含了两个 CACHE Line

- (D1) CACHE 控制器从物理地址中提取 Tag 字段,然后与 CACHE Set1 组内第一个 CACHE Line 的 Tag 字段进行比较,此时两个 Tag 字段并不匹配.

- (D2) CACHE 控制器继续与 CACHE Set1 组内最后一个 CACHE Line 的 Tag 字段进行比较,此时两个 Tag 匹配,并检查到 Valid 字段有效,那么 CACHE Hit

- (E) CACHE 控制器从匹配 CACHE Line 中提取其 Data 域,并从物理地址中提取 Offset 字段,最后从 Data 域中获得所需的数据.

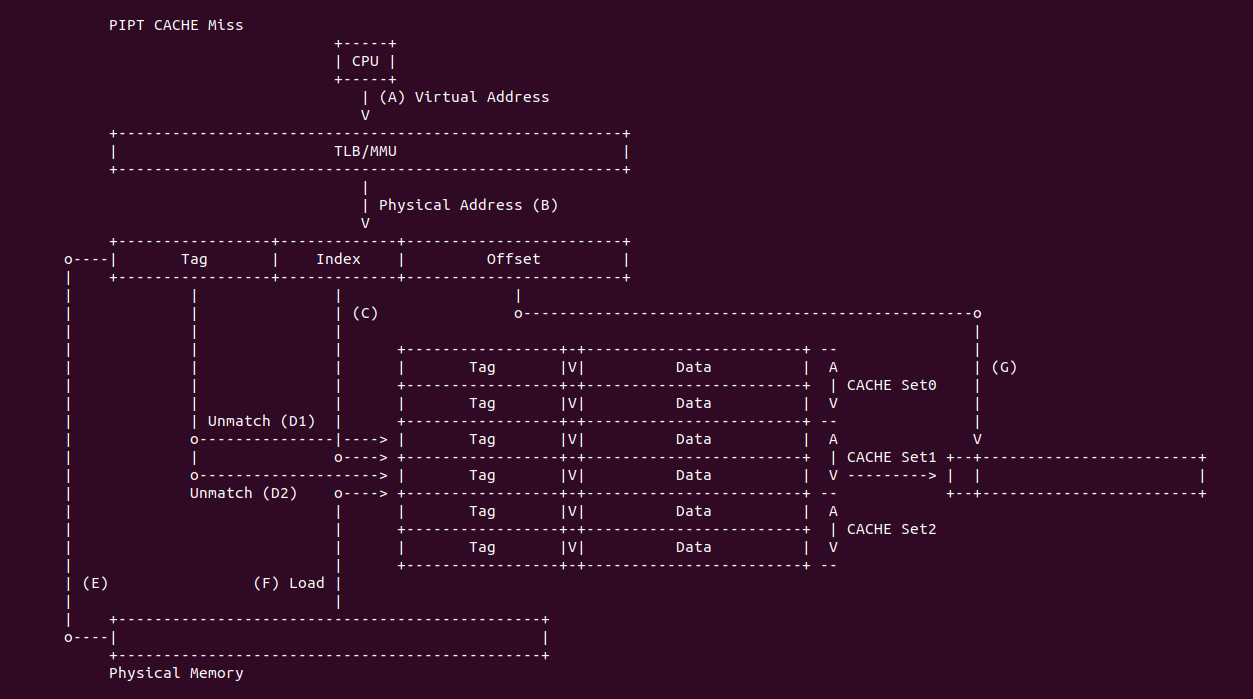

PIPT CACHE Miss: 当 CACHE 控制器使用 PIPT 索引 CACHE Line 发生 CACHE Miss:

- (A) CPU 产生的虚拟地址首先传递给 TLB/MMU 进行地址转换

- (B) TLB/MMU 将虚拟地址转换成物理地址,并传递给 CACHE 控制器

- (C) CACHE 控制器从物理地址中提取 Index 字段,然后找到对应的 CACHE Set1,组内包含了两个 CACHE Line

- (D1) CACHE 控制器从物理地址中提取 Tag 字段,然后与 CACHE Set1 组内第一个 CACHE Line 的 Tag 字段进行比较,此时两个 Tag 字段并不匹配.

- (D2) CACHE 控制器继续与 CACHE Set1 组内最后一个 CACHE Line 的 Tag 字段进行比较,此时两个 Tag 还是不匹配(或者就算 Tag 匹配但 Valid 域无效),那么 CACHE Miss

- (E) CACHE 根据物理地址在主内存中找打对应的 Data Block

- (F) CACHE 根据一定的替换算法在 CACHE Set1 中指定的 CACHE Line 刷出,然后将主内存 Data Block 加载到 CACHE Line,并更新 Tag 和 Valid 字段

- (G) CACHE 控制器从新更新的 CACHE Line 中提取其 Data 域,并从物理地址中提取 Offset 字段,最后从 Data 域中获得所需的数据.

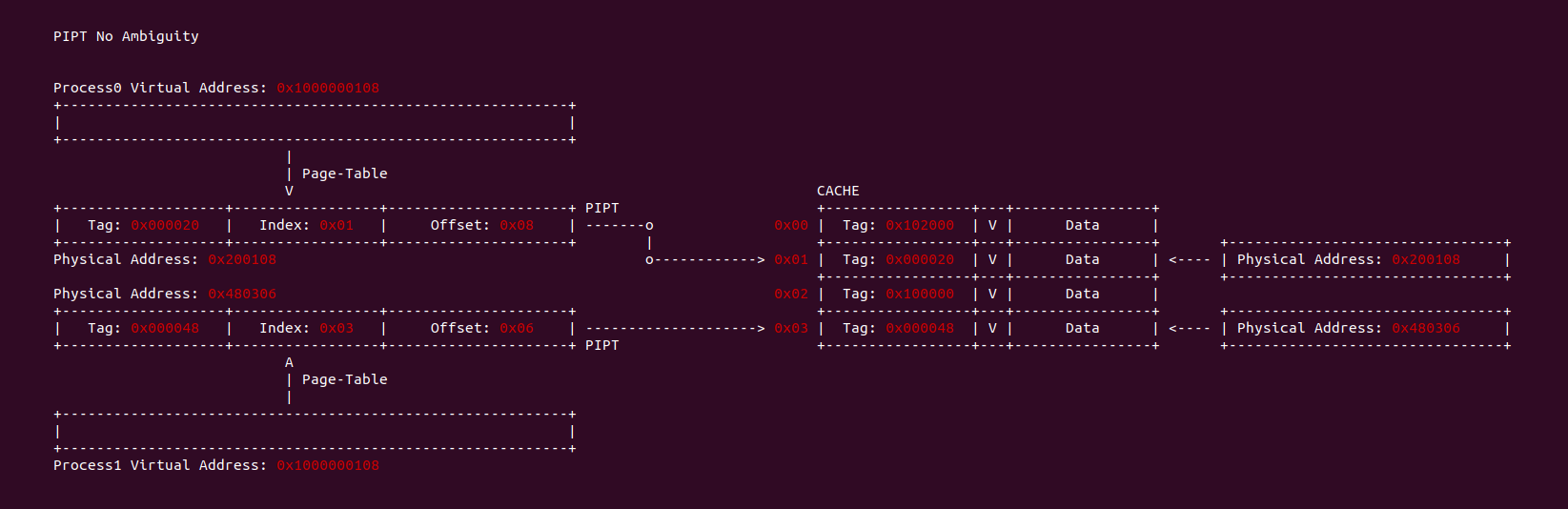

在不同的进程地址空间里,虚拟地址相同,但映射到不同的物理内存上,如果 CACHE 控制器使用物理地址的 Index 和 Tag 查找 CACHE Line,那么不会出现歧义问题. 由于物理地址的唯一性,就算虚拟地址相同,但物理地址是不同的,因此可以保证 Index 和 Tag 索引到的 CACHE Line 只映射一个的物理地址, 从而避免了 CACHE 歧义问题.

同样是不同进程不同的进程的空间虚拟地址映射到同一个物理地址,如果 CACHE 控制器使用物理地址的 Index 和 Tag 查找 CACHE Line,那么不会出现别名问题. 由于物理地址的唯一性,就算不同的虚拟地址映射到同一个物理地址,因此可以保证物理地址只被加载到一个 CACHE Line 中,从而避免了 CACHE 别名问题.

PIPT 优缺点: PIPT 带来的好处是很明显的,软件层面基本不需要任何维护就可以避免歧义和别名问题,但硬件设计上比 VIVT 复杂很多,因此硬件成本更高。最后对一个架构来说,CPU、TLB/MMU 和 CACHE 是三个不同的硬件模块,如果采用 PIPT 的话,CPU 发出虚拟地址经过 TLB/MMU 地址转译获得物理地址之后,CACHE 才能进行查询,这个串行操作直接损害性能, 因此没有 VIVT 高效.

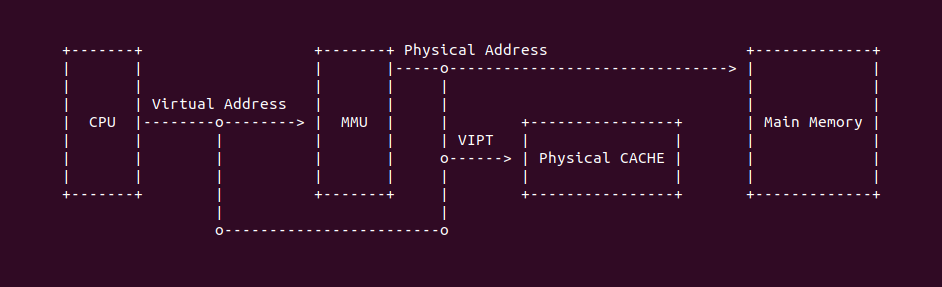

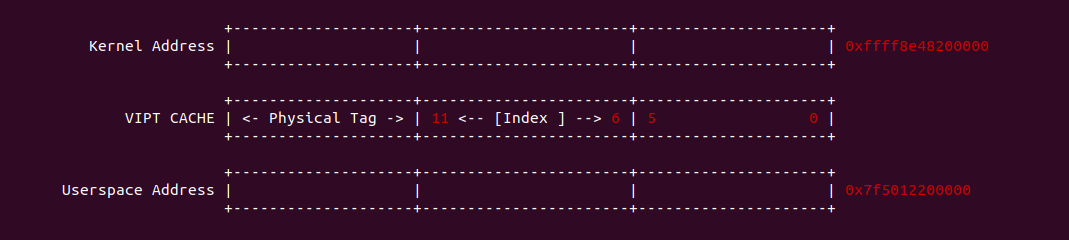

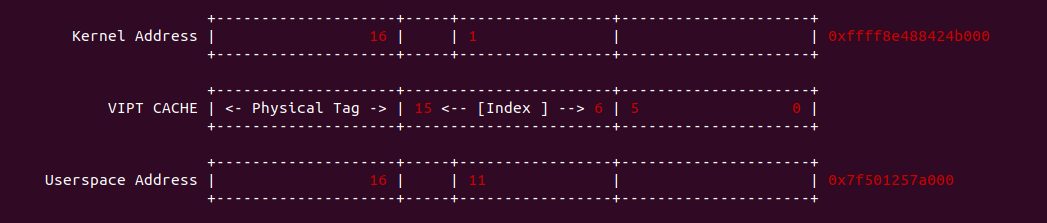

VIPT

VIPT(Virtual Index Physical Tag) 指的是物理 CACHE 控制器通过虚拟地址提供的 Index 和物理地址提供的 Tag 索引 CACHE Line. CPU 产生虚拟地址之后,可以同时将虚拟地址传递给 CACHE 控制器和 TLB/MMU 并发处理,这样索引 CACHE Set 和地址转译在时间上并发。歧义问题和别名问题在 VIPT 中是不存在的。

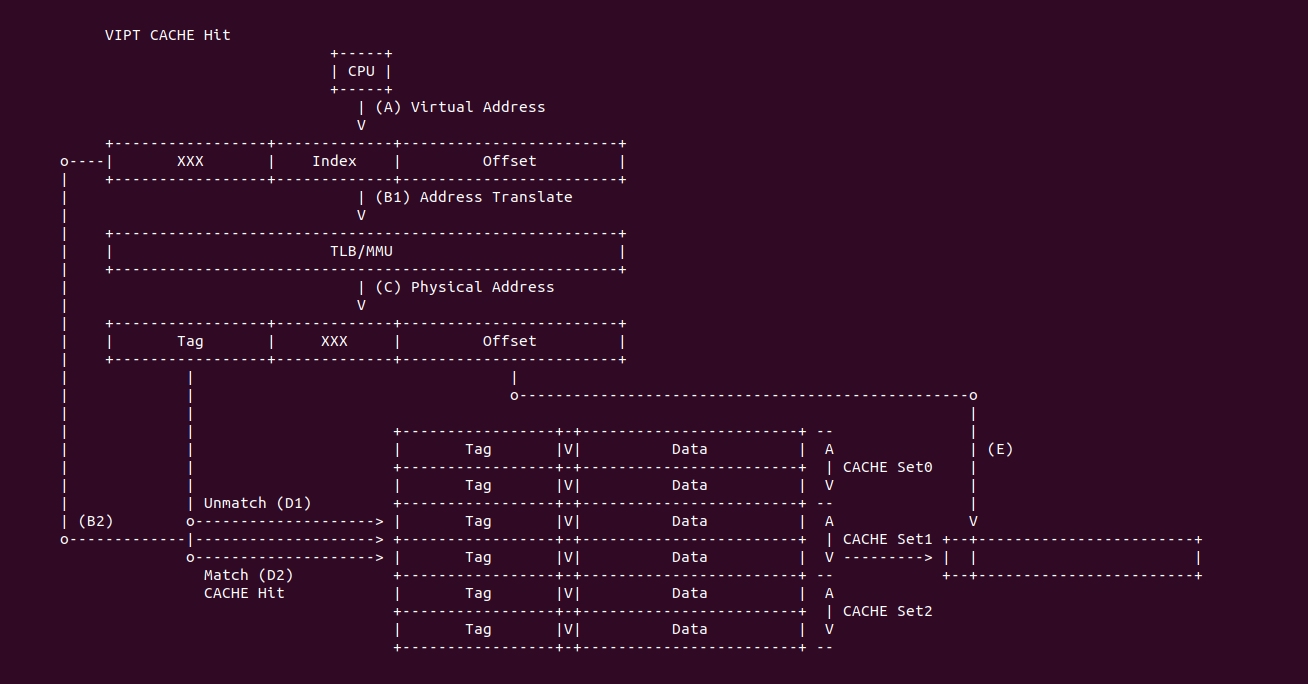

VIPT CACHE Hit: 当 CACHE 控制器使用 VIPT 索引 CACHE Line 发生 CACHE Hit:

- (A) CPU 产生的虚拟地址同时传递给 CACHE 控制器和 TLB/MMU 组件

- (B1) 虚拟地址传送给 TLB/MMU 进行地址转译,以此获得物理地址

- (B2) 虚拟地址传送给 CACHE 控制器之后,提取虚拟地址的 Index 字段在 CACHE 中找到 CACHE Set1,组内包含两个 CACHE Line

- (C) TLB/MMU 地址转译完毕获得物理地址

- (D1) CACHE 控制器从物理地址中提取 Tag 字段与 CACHE Set1 第一个 CACHE Line 的 Tag 字段进行比对,结果不匹配

- (D2) CACHE 继续将物理地址提取的 Tag 字段与 CACHE Set1 的最后一个 CACHE Line 的 Tag 字段进行比对,匹配成功,并且此时 CACHE Line 的 Valid 字段有效,CACHE Hit.

- (E) CACHE 将匹配到的 CACHE Line Data 域取出,然后从物理地址或虚拟地址中获得 Offset 字段,最终从 Data 域中获得所需的数据.

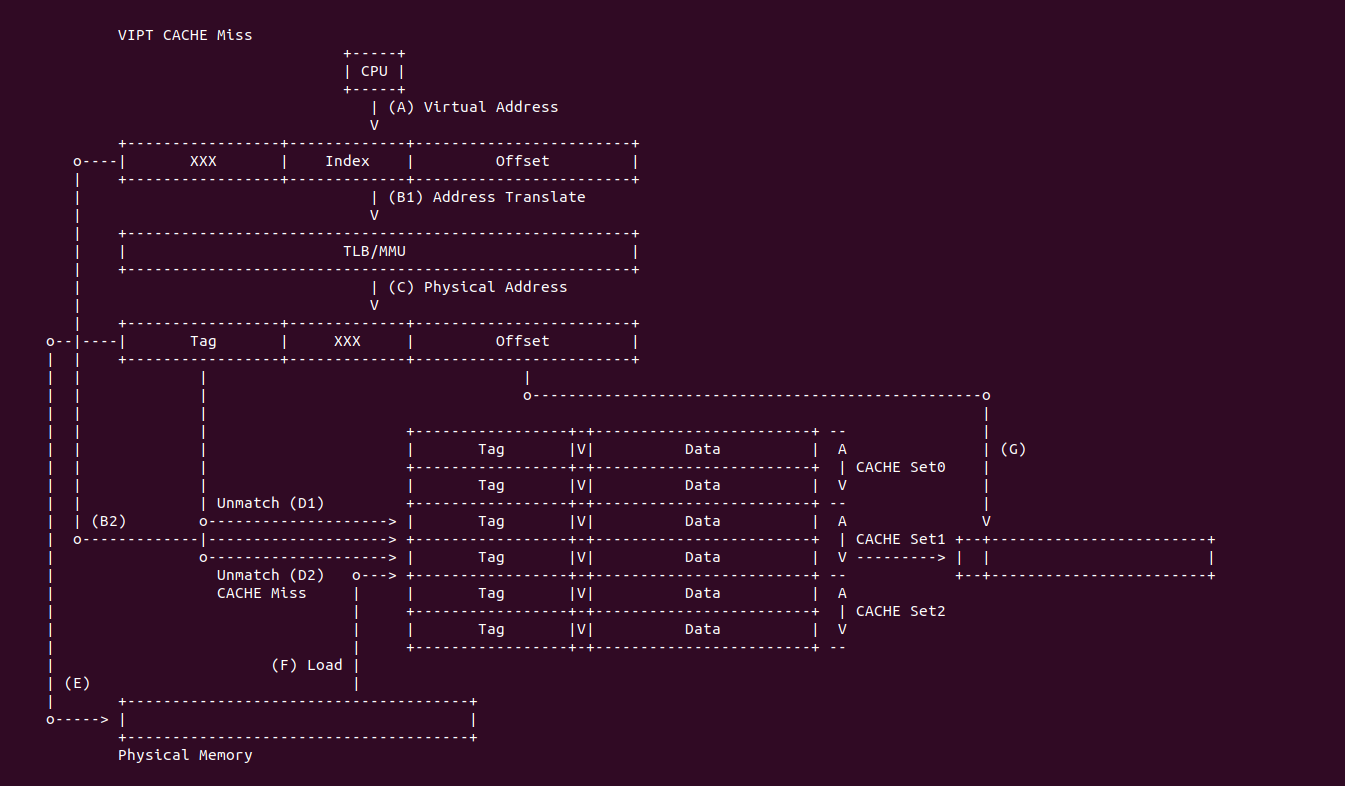

VIPT CACHE Miss: 当 CACHE 控制器使用 VIPT 索引 CACHE Line 发生 CACHE Miss:

- (A) CPU 产生的虚拟地址同时传递给 CACHE 控制器和 TLB/MMU 组件

- (B1) 虚拟地址传送给 TLB/MMU 进行地址转译,以此获得物理地址

- (B2) 虚拟地址传送给 CACHE 控制器之后,提取虚拟地址的 Index 字段在 CACHE 中找到 CACHE Set1,组内包含两个 CACHE Line

- (C) TLB/MMU 地址转译完毕获得物理地址

- (D1) CACHE 控制器从物理地址中提取 Tag 字段与 CACHE Set1 第一个 CACHE Line 的 Tag 字段进行比对,结果不匹配

- (D2) CACHE 继续将物理地址提取的 Tag 字段与 CACHE Set1 的最后一个 CACHE Line 的 Tag 字段进行比对,结果不匹配(或者匹配当 Valid 无效),那么 CACHE Miss.

- (E) CACHE 控制器根据物理地址在主存中找到对应的 Data Block

- (F) CACHE 控制器在 CACHE Set1 根据替换算法将指定的 CACHE Line 刷出,然后将 Data Block 加载到 CACHE Line,并更新 Tag 和 valid 字段

- (G) CACHE 将新更新的 CACHE Line Data 域取出,然后从物理地址或虚拟地址中获得 Offset 字段,最终从 Data 域中获得所需的数据.

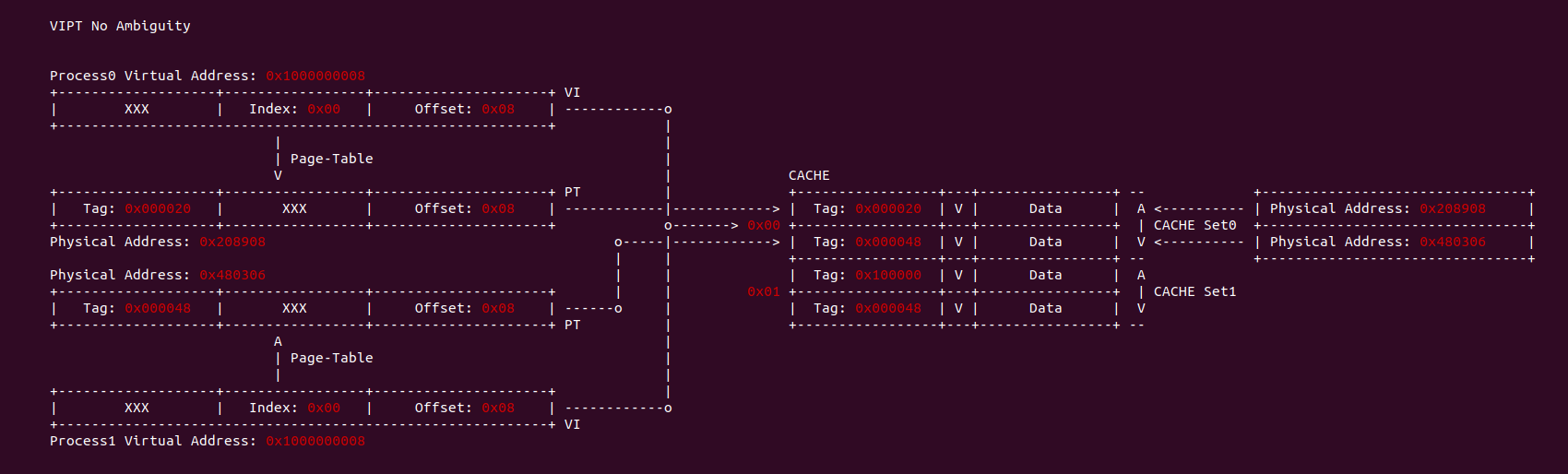

在 VIPT 场景下,当两个进程的地址空间相同的虚拟地址映射到不同的物理地址,那么两个虚拟地址的 Index 是相同的,因此 CACHE 会定位到相同的 CACHE Set,但由于 CACHE Set 内包含多个 CACHE Line,由于物理地址的唯一性,不同的物理地址的 Tag 是不相同的,因此该场景下会对应两个不同的 CACHE Line,因此 VIPT 不存在歧义问题.

在 VIPT 场景下,当不同进程的地址空间不相同的虚拟地址映射到同一个物理地址,那么两个虚拟地址的 Index 不相同,因此物理内存 Data block 可以加载到任意多个 CACHE Set。该场景下假设 CACHE 控制器通过虚拟地址 Index 找到 CACHE Set 之后,根据物理 Tag 发现该 CACHE Set 的所有 CACHE Line Tag 都不匹配,但物理内存的 Data block 已经加载到另外的 CACHE Set,CACHE 控制器现在无法获得其他 CACHE Set 的信息,因此引起了别名问题.

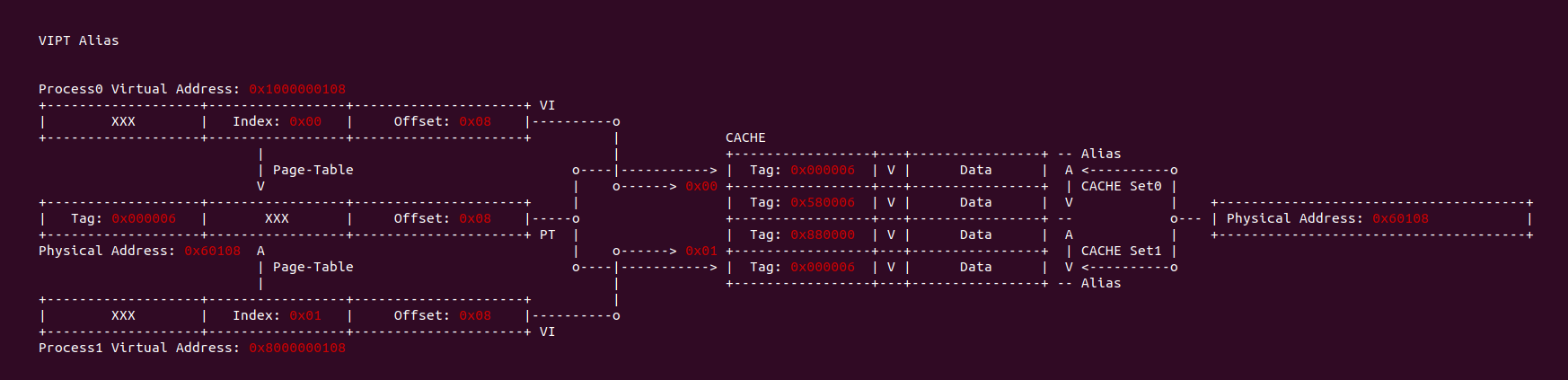

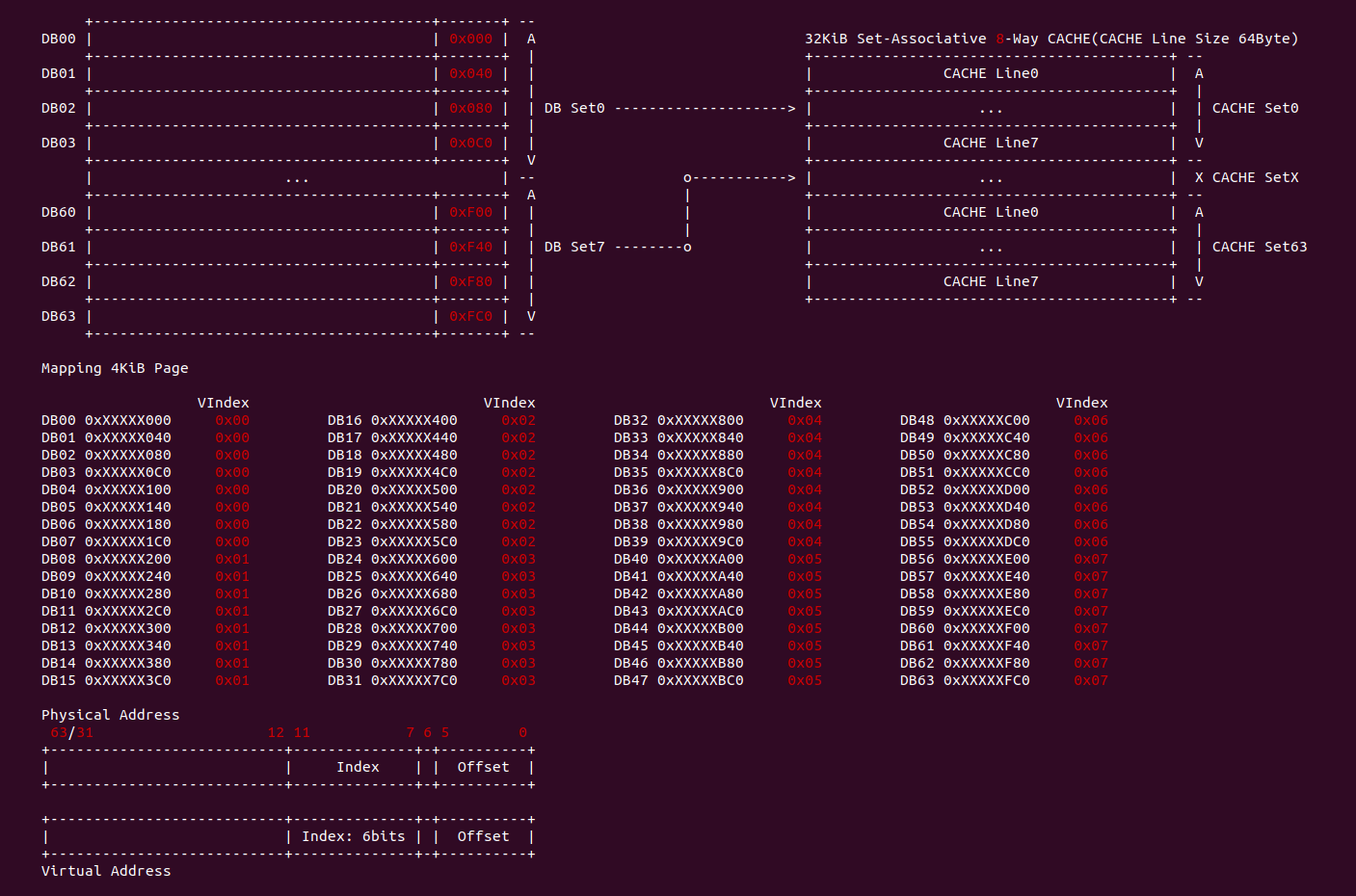

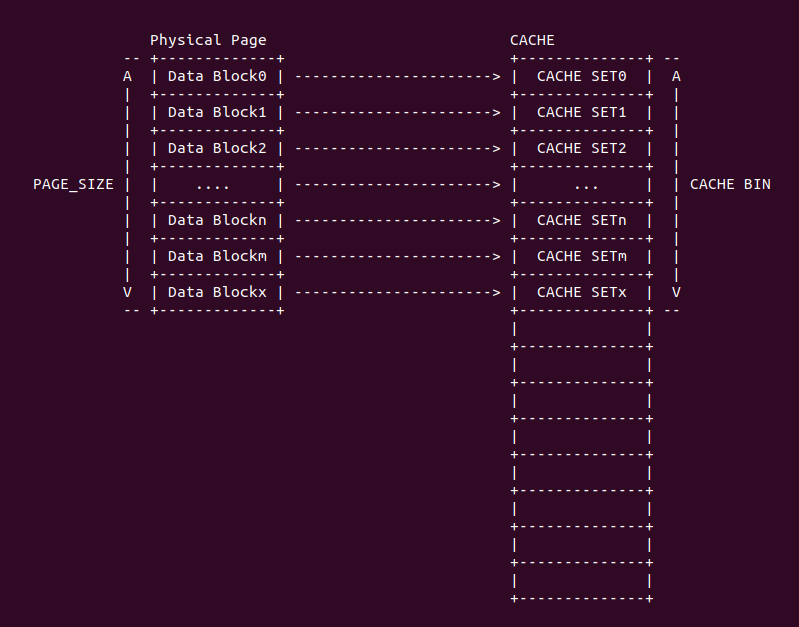

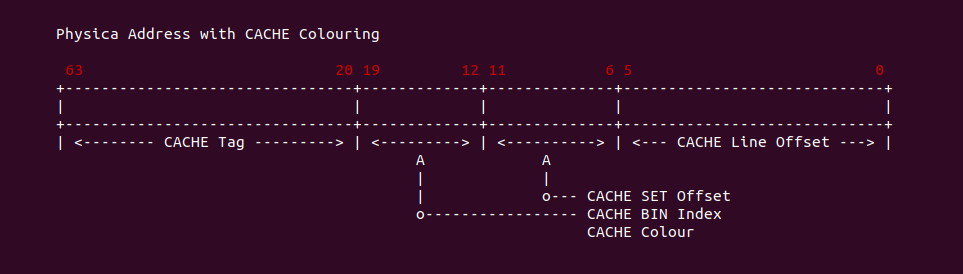

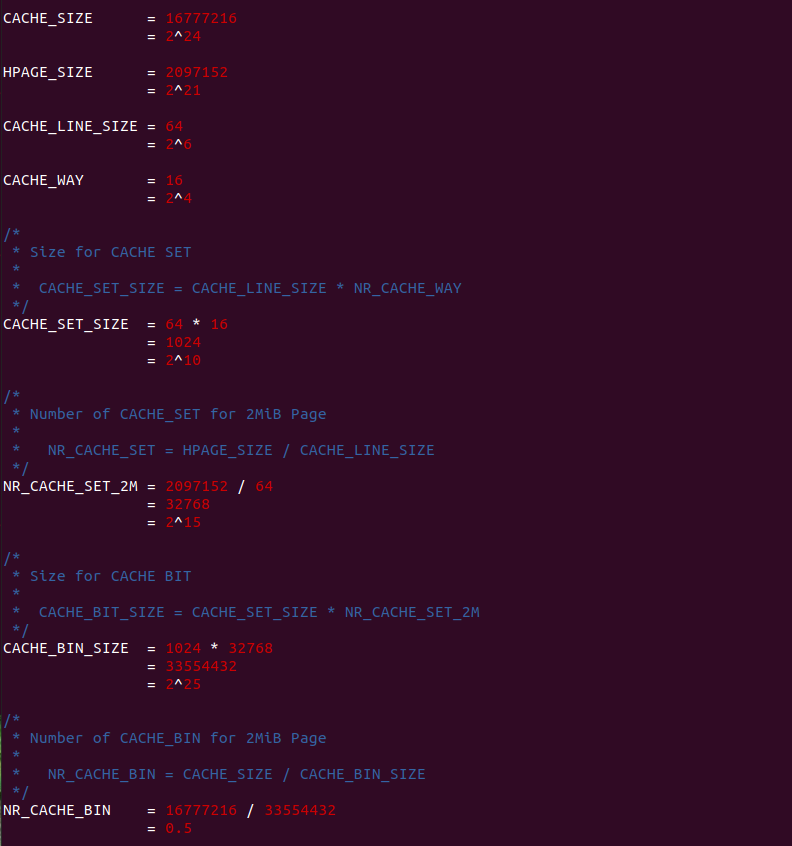

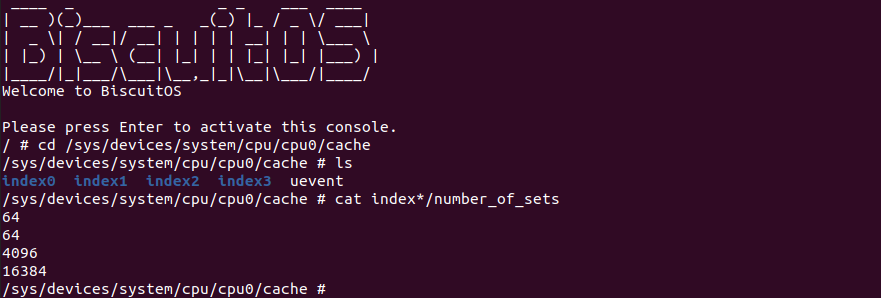

4KiB 别名问题: 对于 VIPT 的别名问题,在 Linux 上是有解法的,例如在 8-Way 32KiB 组相联映射 CACHE 中 CACHE Line Size 为 64Bytes,一共包含 64 个 CACHE Set,因此需要虚拟地址提供 6bits 作为 Index。当映射 4KiB 物理页时,其包含 64 个 Data Block,将 8 个 Data Block 作为一组,其中物理地址 [0:5] 作为 Offset 字段,物理地址 [6:11] 寻址所有的 CACHE Set,实际只需要 3bit 就可以寻址所有 Data Block 组。由于映射 4KiB 页的低 12 位虚拟地址的内容和物理地址一致,那么虚拟地址 Index 6bit 与物理地址 [6:11] 字段内容是一致的,此时虚拟地址 Index 等效于物理地址 Index, 因此可以解决 VIPT 别名问题.

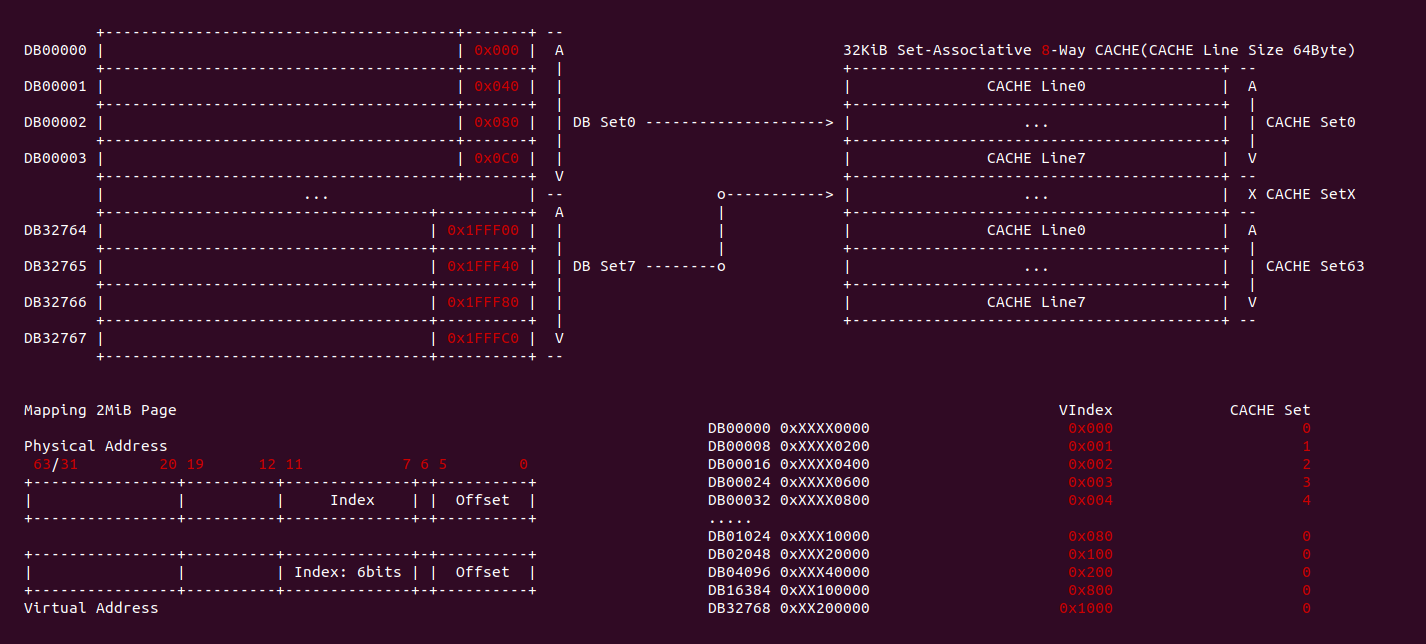

2MiB 别名问题: 在 8-Way 32KiB 组相联映射 CACHE 中 CACHE Line Size 为 64Bytes,一共包含 64 个 CACHE Set,因此需要虚拟地址提供 6bits 作为 Index。当映射 2MiB 物理页时,其包含 32768 个 Data Block,将 8 个 Data Block 作为一组,一共 4096 Data block 组。其中物理地址 [0:5] 作为 Offset 字段,物理地址 [7: 11] 可以寻址所有的 CACHE Set, 实际需要 12bit 才能寻址所有的 Data Block 组,由于映射 2MiB 页的低 20 位虚拟地址的内容和物理地址一致,因此只要虚拟地址 6Bit 位于低 20 bit,那么虚拟地址 Index 就和物理 Index 一致,可以做到 2MiB 页内的物理地址只会加载到唯一的 CACHE Set 中,也可以解决 VIPT 的别名问题.

直接映射别名问题: 在 8KiB 采用直接映射的 CACHE 中,CACHE Line Size 为 256 字节,其一共包含 32 个 CACHE Line,因此虚拟地址需要提供 5bit 寻址 CACHE Line,9 bit 用于 Offset 字段。在映射 4KiB 物理页的场景中,由于虚拟地址 [0:8] 区域用于 Offset 字段,虚拟地址 [9:14] 区域用于 Index 字段,由于 4KiB 映射物理页只有低 12 位虚拟地址和物理地址内容相同,因此此时虚拟地址 Index 不等效于物理地址 Index,因此会出现别名问题; 但同样的环境映射 2MiB 的物理页,由于低 20 位虚拟地址和物理地址内容一致,因此此时虚拟地址 Index 等效物理地址 Index, 此时不存在别名问题.

VIPT 别名问题总结: 通过上面的案例分析,VIPT 要避免别名问题与 CACHE 的映射方式有关: 当使用组相联映射时,CACHE Set 的数量会影响别名问题,具体来说 CACHE Set 越大越容易引发别名问题; 当使用直接映射时,CACHE Line Size 会影响别名问题,当 CACHE Line Size 越大,Index 字段就会超过 4KiB/2MiB 低一致位,那么更容易引发一致性问题. 目前主流解决 VIPT 问题就是是 CACHE 采用组相联映射方式,CACHE 规模为 32KiB 8-Way(CACHE Line Size: 64B). 对于目前处理器 L1 CACHE 都是 VIPT,可以和 TLB/MMU 并发 CACHE 查询过程,但 VIPT 不是所有级 CACHE 的最佳选择,CACHE 越大需要的 Index 字段越大,那么越容易引发别名问题,因此 L2/L3 采用物理地址 Index 是最佳选择.

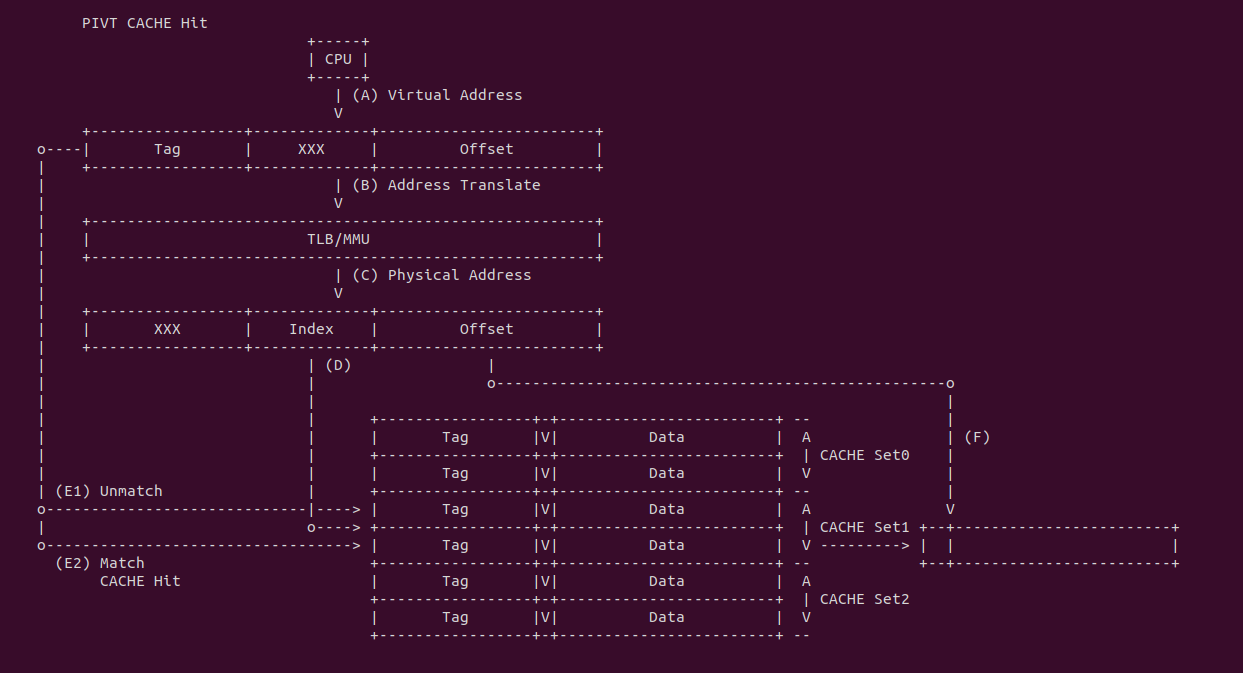

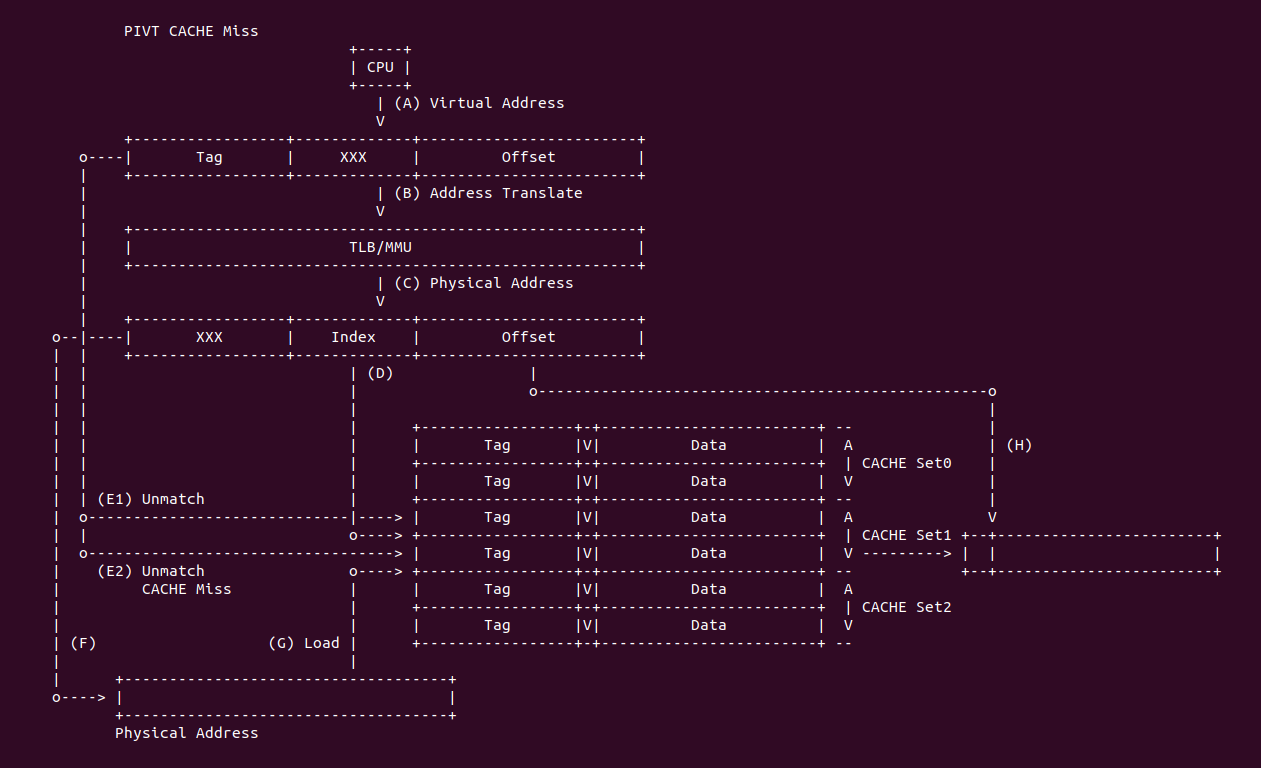

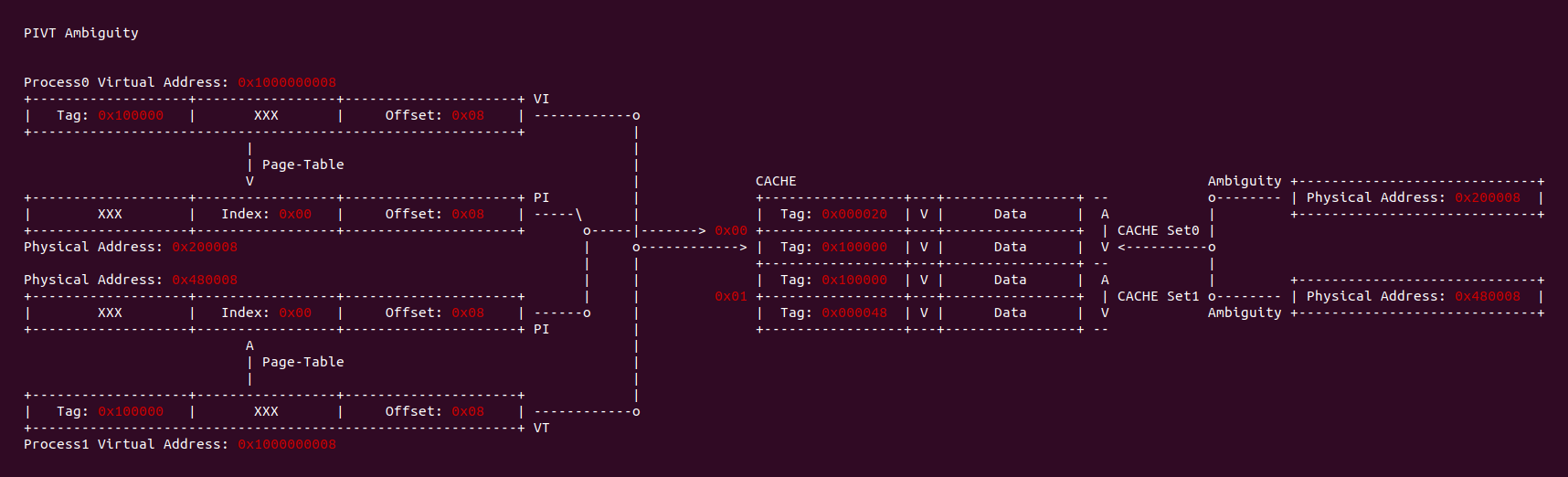

PIVT

PIVT(Physical Index Virtual Tag) 指的是物理 CACHE 控制器通过物理地址提供的 Index 和虚拟地址提供的 Tag 索引 CACHE Line. CPU 产生虚拟地址之后,PIVT 并不能像 VIPT 那样并发的在 CACHE 和 TLB/MMU 中工作,因为 CACHE 在查找 CACHE Line 时需要先定位 CACHE Set,再结合 Tag 字段才能定位 CACHE Line,但 PIVT 首先需要将虚拟地址传递给 TLB/MMU 进行地址转译,获得物理地址 Index 字段之后传递给 CACHE 才能定位 CACHE Set,最后根据虚拟地址的 Tag 定位 CACHE Line. PIVT 既包含了别名和歧义问题,而且性能也比 VIVT 或者 VIPT 方式慢很多.

PIVT CACHE Hit: 当 CACHE 控制器使用 PIVT 索引 CACHE Line 发生 CACHE Hit:

- (A) CPU 产生虚拟地址

- (B) CPU 将虚拟地址传递给 TLB/MMU 进行地址转译

- (C) TLB/MMU 地址转译完毕,获得物理地址

- (D) 将物理地址的 Index 传递给 CACHE 控制器,匹配到 CACHE Set1,组内包含了两个 CACHE Line

- (E1) CACHE 控制器从虚拟地址提取 Tag 字段与 CACHE Set1 第一个 CACHE Line 的 Tag 字段进行比对,结果发现不匹配

- (E2) CACHE 控制器继续与 CACHE Set1 的最后一个 CACHE Line 的 Tag 字段进行比对,发现匹配且 CACHE Line 的 Valid 位有效,那么 CACHE Hit.

- (F) CACHE 将匹配到的 CACHE Line Data 域取出,然后从物理地址或虚拟地址中获得 Offset 字段,最终从 Data 域中获得所需的数 据.

PIVT CACHE Miss: 当 CACHE 控制器使用 PIVT 索引 CACHE Line 发生 CACHE Miss:

- (A) CPU 产生虚拟地址

- (B) CPU 将虚拟地址传递给 TLB/MMU 进行地址转译

- (C) TLB/MMU 地址转译完毕,获得物理地址

- (D) 将物理地址的 Index 传递给 CACHE 控制器,匹配到 CACHE Set1,组内包含了两个 CACHE Line

- (E1) CACHE 控制器从虚拟地址提取 Tag 字段与 CACHE Set1 第一个 CACHE Line 的 Tag 字段进行比对,结果发现不匹配

- (E2) CACHE 控制器继续与 CACHE Set1 的最后一个 CACHE Line 的 Tag 字段进行比对,结果发现不匹配或者就算匹配,当 CACHE Line 的 Valid 标志位无效,因此 CACHE Miss.

- (F) CACHE 控制器利用物理地址在主存中找到对应的 Data Block

- (G) CACHE 控制器根据一定的替换算法将 CACHE Set1 中的某个 CACHE Line 刷出去,然后将找到的 Data Block 加载到该 CACHE Line 里

- (H) CACHE 将匹配到的 CACHE Line Data 域取出,然后从物理地址或虚拟地址中获得 Offset 字段,最终从 Data 域中获得所需的数 据.

在不同的进程地址空间,虚拟地址虽然相同,但映射到不同的物理内存,如果 CACHE 控制器使用物理地址 Index 和虚拟地址 Tag 查找 CACHE Line,那么会出现同一个 CACHE Line 映射不同的物理地址,这就是 PIVT 的歧义问题. 为了保证系统的正确工作,操作系统需要负责避免歧义出现,可以通过按需清除 CACHE Line,或者为每一个进程的地址空间添加标记(PCID/ASID),当进程切换时刷掉指定的 CACHE Line, 不过这样做会导致进程调度回来时出现大量的 CACHE Miss,影响程序的性能.

同样是不同进程的地址空间不同的虚拟地址映射到同一个物理地址上,如果 CACHE 控制器使用物理地址的 Index 和虚拟地址 Tag 查找 CACHE Line,那么由于同一个物理地址,因此会定位到同一个 CACHE Set,但由于 Tag 不同,那么不同的虚拟地址 Tag 会定位到不同的 CACHE Line,此时出现了同一个物理地址被映射到不同 CACHE Line, 这就是 PIVT 的别名问题. 该问题会引起 CACHE 的一致性问题,例如更新了存在别名 CACHE Line 的数据,那么同别名的 CACHE Line 的数据没有被更新,导致 CACHE 数据一致性问题. 同歧义问题一样,可以通过 Flush CACHE 的方式避免别名问题,也可以针对共享的数据映射相同物理地址时采用 NOCACHE 的方式,但这样会损失 CACHE 带来的性能提升.

PIVT 优缺点: 通过上面对 PIVT 进行分析,发现 PIVT 具有 VIVT 的别名和歧义缺点,另外还没有 VIPT 并行特点,因此 PIVT 并没有任何优势可言.

VIVT/VIPT/PIPT/PIVT 总结

CACHE 对 CPU 的性能至关重要,目前主流处理器 L1 CACHE 采用 VIPT,CACHE 控制器通过虚拟地址 Index 取出一组 CACHE Line,同时并行进行 TLB/MMU 地址转译获得物理地址 Tag,最后从 CACHE Line 组中找到目标 CACHE Line,另外 Index 字段所需的位数在页表页偏移之内,那么虚拟地址 Index 是等效于物理地址 Index,那么这个时候不存在歧义和别名问题。但 VIPT 并不是所有级 CACHE 的首选,随着 CACHE 体积变大,Index 字段的长度会不断变大,当超过虚拟内存映射物理内存页内偏移区域之后,虚拟地址 Index 不再等效于物理地址 Index,便会增加歧义和别名问题的概率,因此 L2/L3 CACHE 选择 PIPT 的索引方式,这样可以避免歧义和别名问题. VIVT 软件维护成本太高,并会引入歧义和别名问题,需要在进程切换时 Flush 指定的 CACHE Line,软件管理难度大。现在主流使用 VIPT 和 PIPT。在多路组相联的 CACHE 中,CACHE Way 的大小等于 4KiB,一般硬件采用 VIPT 方式可以有效避免歧义和别名问题,等效于 PIPT; 当 CACHE Way 的大小大于 4KiB,一般采用 PIPT 方式,可以减轻操作系统的压力.

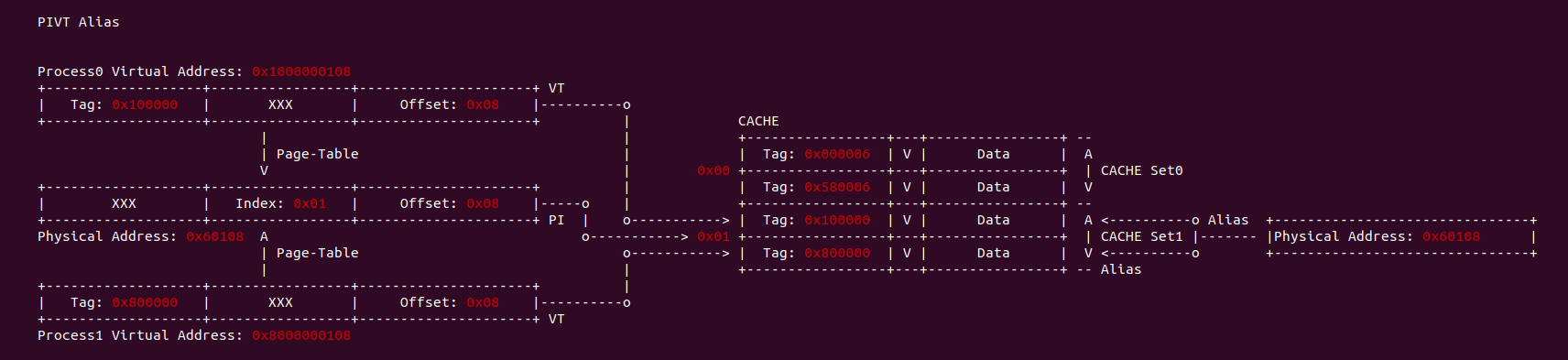

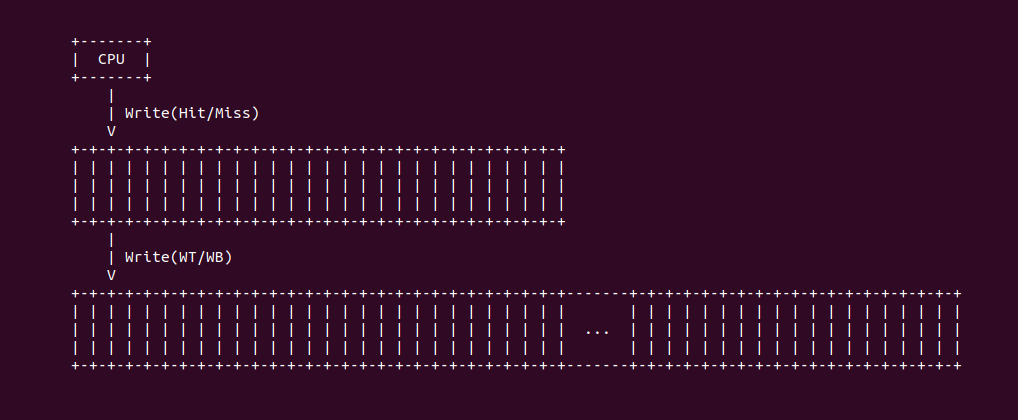

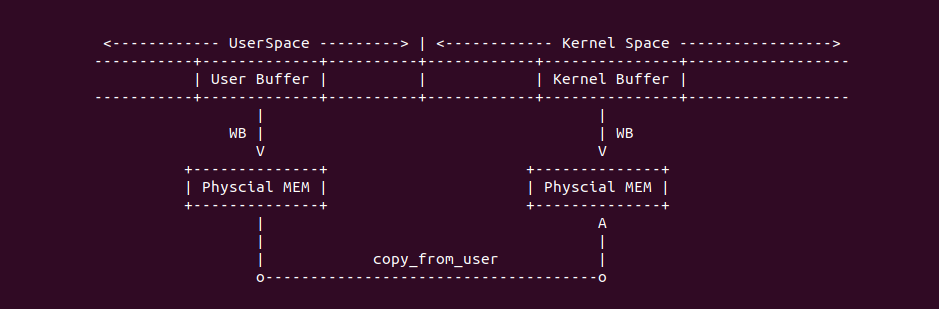

CACHE 回写/通写

CACHE 写数据分为两种情况: 1. 将被改写的数据在 CACHE 中. 2. 被改写的数据不在 CACHE 中. 针对情况 1,CACHE 有两种策略来写数据:

- 回写(Write Back): 只改写 CACHE 中的 CACHE Line,不更新主存 Data Block. 优点是速度快,因为不用访问速度较慢的主存,缺点是只改写了 CACHE Line,CACHE Line 和主存 Data Block 数据不再一致,如果有别的核来访问主存中的 Data Block,那么它将读到错误的数据。另外在 CACHE Line 被替换出去的时候,数据应该被写入主存 Data Block,这就需要系统判断哪些 CACHE Line 被更新过,反应在电路上就需要增加一个 Dirty 位,当一个被标记为 Dirty 的 CACHE Line 被替换出去,其内容要被更新到主存.

- 通写(Write Through): 改写 CACHE 中的 CACHE Line 和主存 Data Block. 优点是时刻保持存储器数据一致,缺点是每次 store 指令都需要更新主存中的 Data Block,这个延时代价特别高.

针对第二种情况, 被改写的数据不在 CACHE 中,也有两种策略,一般情况下,回写和写分配组合,通写和写不分配组合:

- 写不分配: 直接把数据写入主存 Data Block.

- 写分配: 先把 Data block 放到 CACHE Line,然后回写或通写.

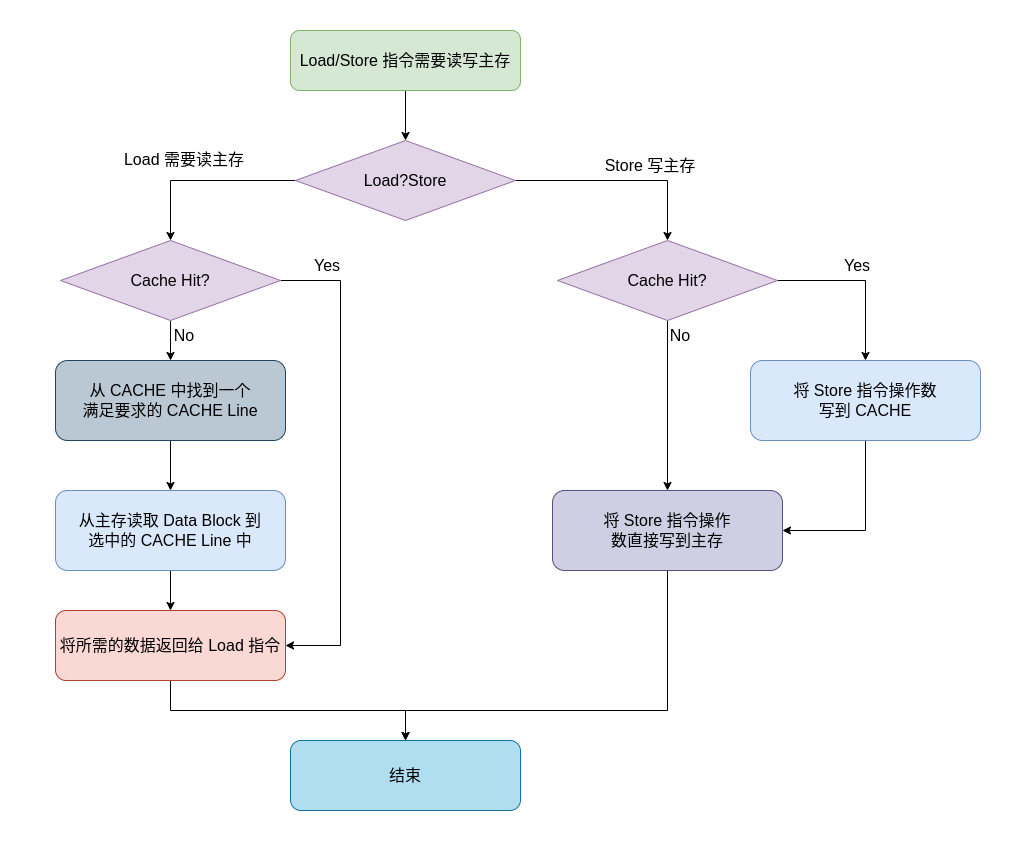

通写和写不分配

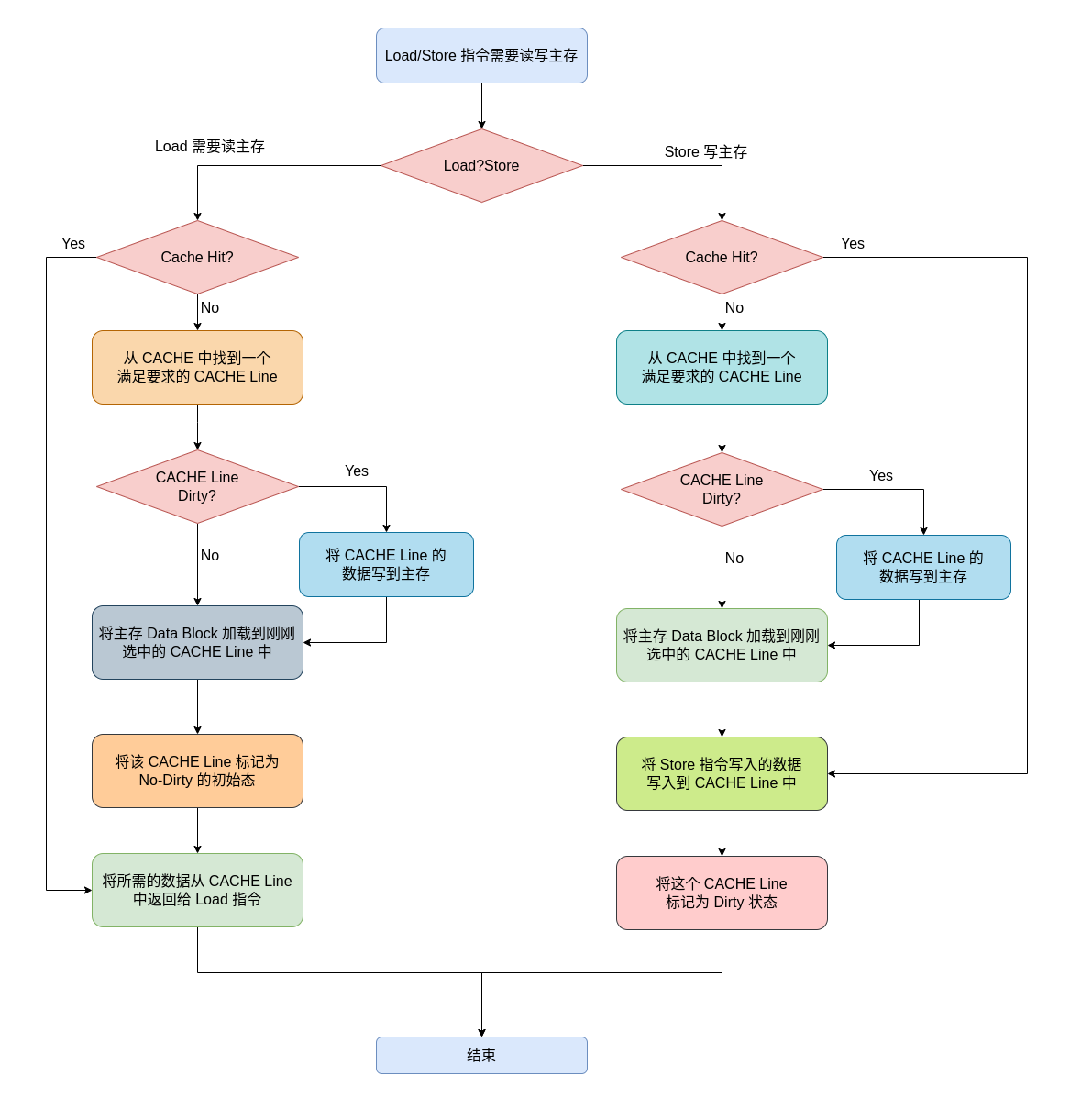

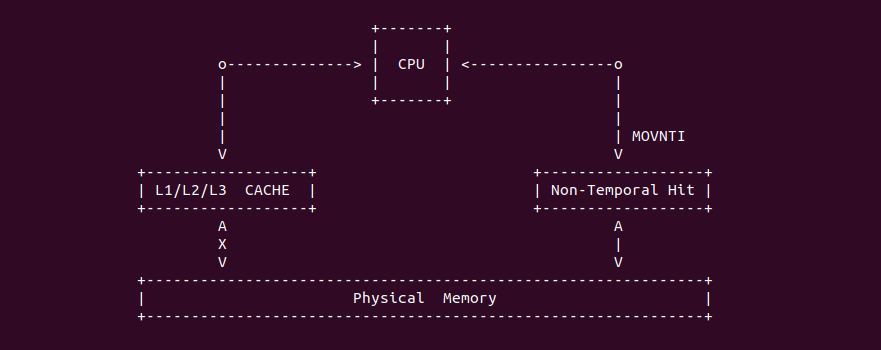

上图是通写和写不分配的处理逻辑,当 CPU 执行了 Load/Store 指令需要读写数据(Load 读请求、Store 写请求),可能出现一下几种情况:

- Load CACHE Hit: 此时 Load 需要读取的数据在 CACHE 中,那么直接从 CACHE Line 中读取 Load 所需的数据.

- Load CACHE Miss: 此时 Load 需要读取的数据不在 CACHE 中,那么首先从 CACHE 中找到一块 CACHE Line,然后从主存中将 Data Block 加载到 CACHE Line 中,最后从 CACHE Line 中读取 Load 所需的数据.

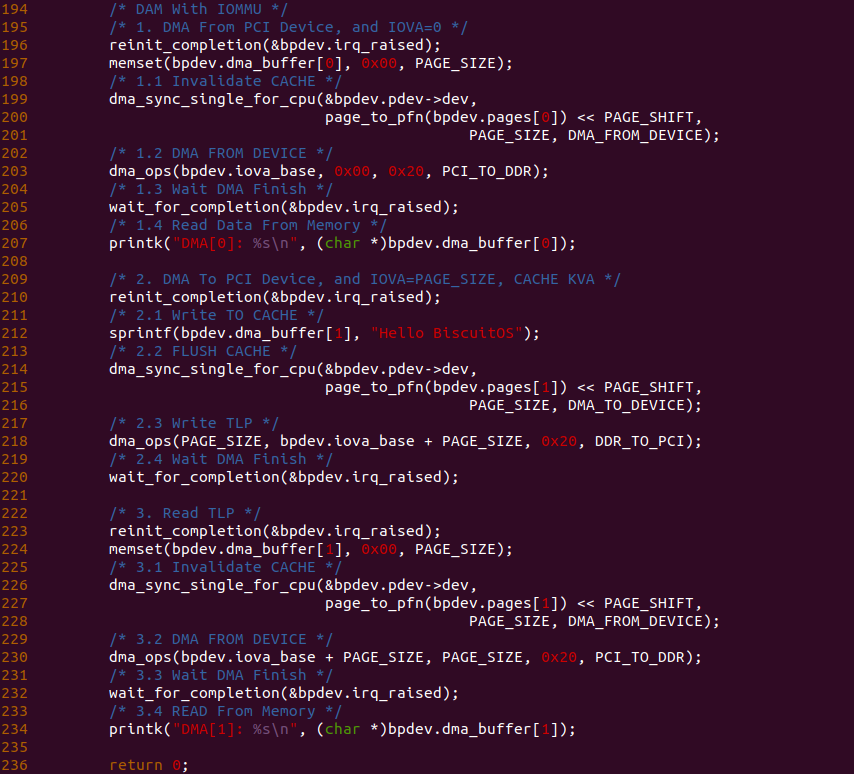

- Store CACHE Hit: 此时 Store 需要写入的数据在 CACHE 中,那么先将 Store 指令写入的数据写入到 CACHE Line 中,然后写入到主存的 Data Block.

- Store CACHE Miss: 此时 Store 需要写入的数据不在 CACHE 中,那么直接将 Store 指令写入的数据写入到主存的 Data Block 里.

回写与写分配

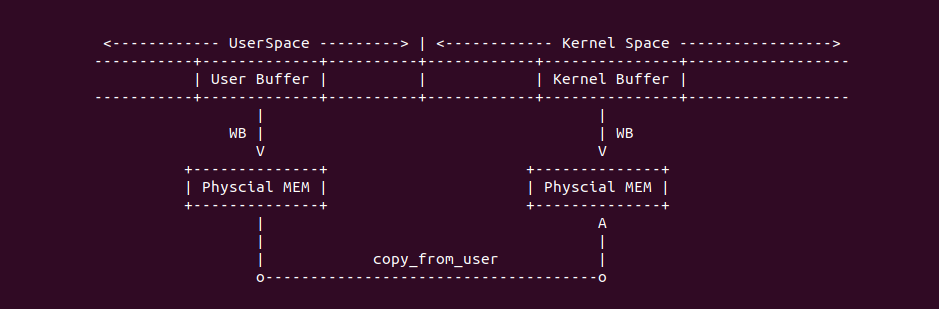

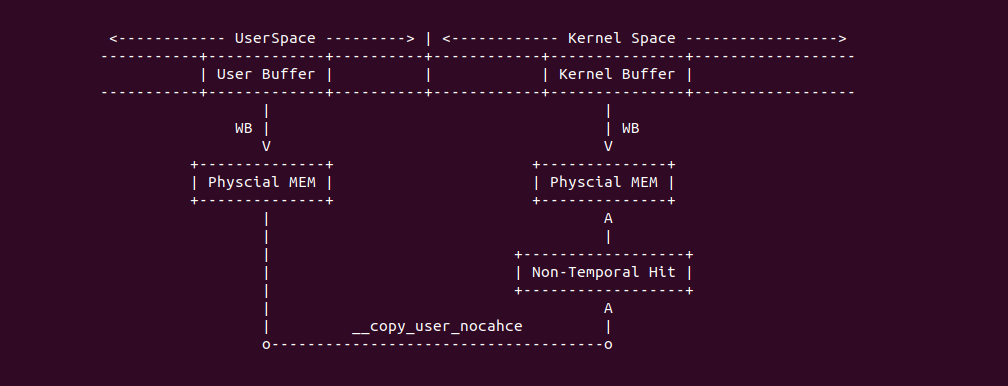

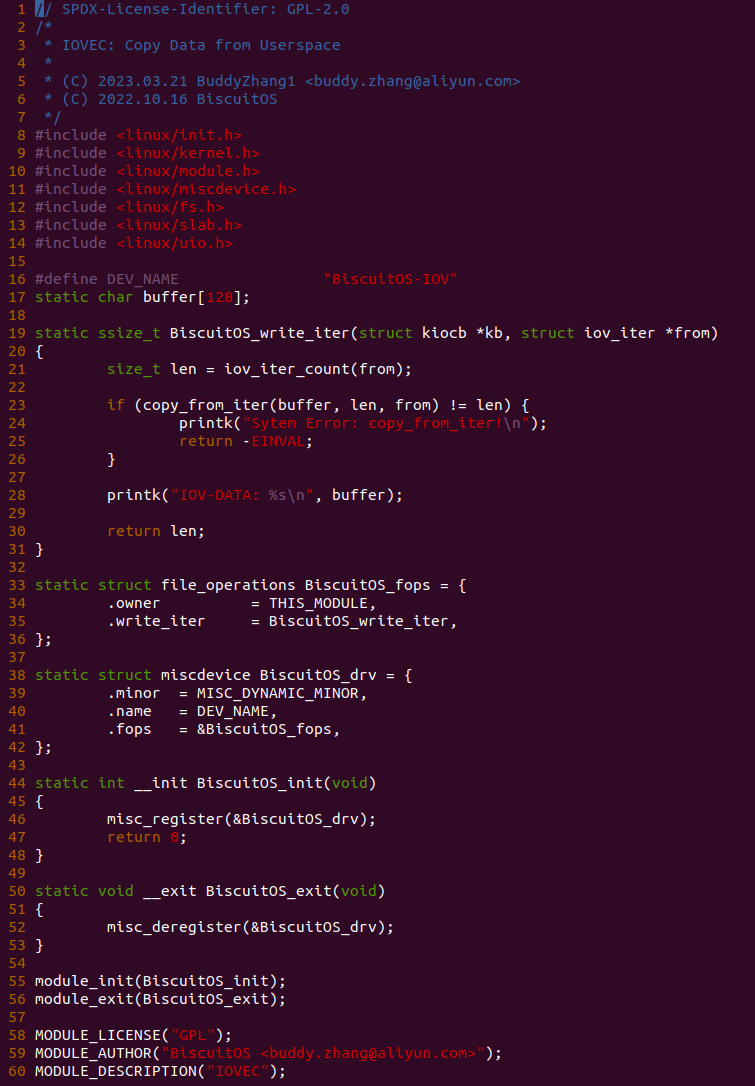

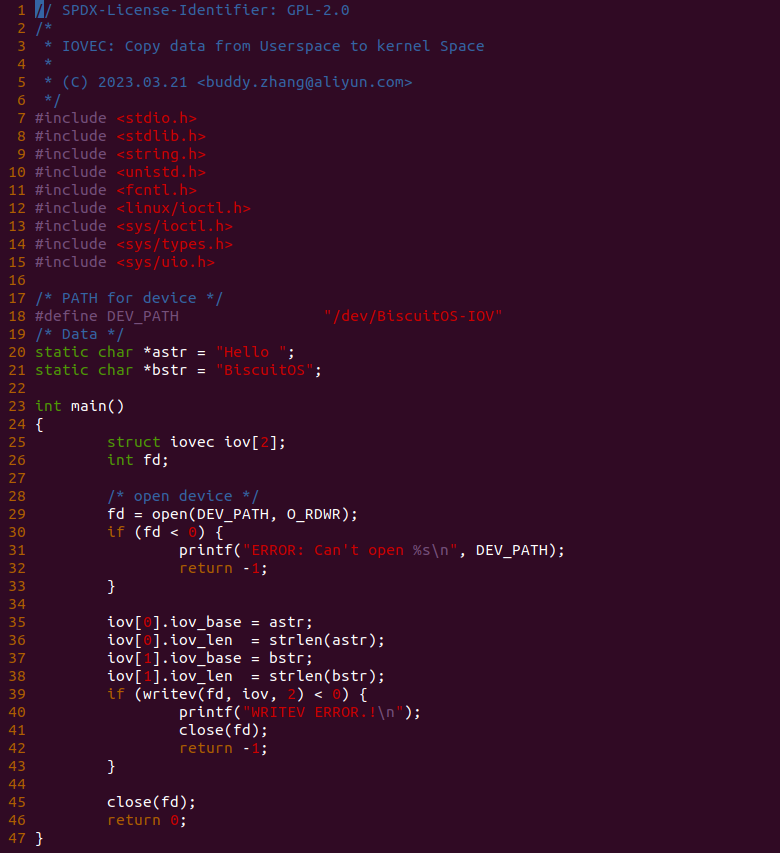

上图是回写和写分配的处理逻辑,当 CPU 执行 Load 指令需要读数据,可能出现以下几种情况:

- Load CACHE Hit: 此时 Load 需要读取的数据在 CACHE 中,那么直接将对应 CACHE Line 的数据返回给 Load 指令.

- Load CACHE Miss 且 CACHE Line No Dirty: 此时 Load 需要读取的数据不在 CACHE 中,CACHE 找了一块 No-Dirty 的 CACHE Line 加载主存中的 Data Block,并将 CACHE Line 标记为 No-Dirty, 最后将 CACHE Line 的数据返回给 Load 指令.

- Load CACHE Miss 且 CACHE Line Dirty: 此时 Load 需要读取的数据不在 CACHE 中,CACHE 找到一块 Dirty 的 CACHE Line,先将 CACHE Line 更新到主存,然后将主存中的 Data Block 加载到 CACHE Line 中,并标记 CACHE Line 为 No-Dirty,最后将 CACHE Line 的数据返回给 Load 指令.

当 CPU 执行 Store 指令需要写数据时,可能会出现一下几种情况:

- Store CACHE Hit: 此时 Store 需要写入的 Data Block 已经在 CACHE 中,那么直接将 Store 指令写如的数据更新到 CACHE Line 中,然后将 CACHE Line 标记为 Dirty.

- Store CACHE Miss 且 CACHE Line No Dirty: 此时 Store 需要写入的 Data Block 不在 CACHE 中,那么 CACHE 首先找到了一块 No-Dirty 的 CACHE Line,然后将主存中的 Data Block 加载到 CACHE Line,接着将 Store 指令需要的数据写入到 CACHE Line,最后将 CACHE Line 标记为 Dirty.

- Store CACHE Miss 且 CACHE Line Dirty: 此时 Store 需要写入的 Data Block 不在 CACHE 中,那么 CACHE 首先找到了一块 Dirty 的 CACHE Line,然后将 CACHE Line 的内容刷新到主存中,接着将主存中的 Data Block 加载到 CACHE Line 中,并将 Store 指令的数据写入到 CACHE Line 中,最后将 CACHE Line 标记为 Dirty.

CACHE 替换策略

无论 CPU 执行 Store/Load 读或写数据时,一旦 CACHE 发生 CACHE Miss,那么需要替换某个 CACHE Line,然后将所需的 Data Block 加载到 CACHE Line。Load 读数据 CACHE Miss 时需要从主存中将 Data Block 加载到 CACHE 中,这个 Data Block 需要替换某个 CACHE Line,这时需要替换算法决定顶替谁; Store 写数据 CACHE Miss 时如果是写分配,那么需要将主存中的 Data Block 加载到 CACHE 中,因此 CACHE 也需要决定 Data Block 替换哪个 CACHE Line. CACHE 支持多种替换算法,包括 FIFO(先进先出)、LRU(最近最少使用) 和随机替换策略等.

LRU(最近最少使用) 策略

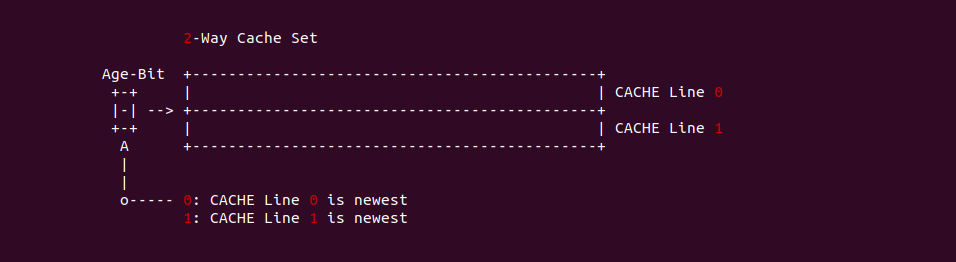

LRU 策略的基本思想就是选择最近一段实践使用次数最少的 CACHE Line 进行替换. CACHE 控制器需要对一个 CACHE Set 中的每个 CACHE Line 的使用情况进行跟踪,可以通过每一个 CACHE Line 都设置年龄位, 但起始状态所有 CACHE Line 都没有使用过,因此只需记录已经被使用的 CACHE Line 的年龄,例如 2-Way 的 CACHE,其每个 CACHE Set 有两个 CACHE Line,但只需一个年龄位,其通过如下逻辑进行判断:

- 当两个 CACHE Line 一直没有使用,那么年龄位一直为 0,那么替换时直接选择 CACHE Line0 替换出去

- 当 CACHE Line1 被使用,年龄位依旧保持 0,那么替换时选择 CACHE Line0 替换出去

- 当 CACHE Line0 被使用,年龄位设置为 1,那么替换的时候选择 CACHE Line1 替换出去

通过案例可以知道,在 2-Way 的 CACHE Set 一个年龄位置位或者清零已经表示有一个 CACHE Line 年龄已经变大. 如果 CACHE Set 里包含的 CACHE Line 越来越多,那么N-Way CACHE Set 需要 Log2(N)

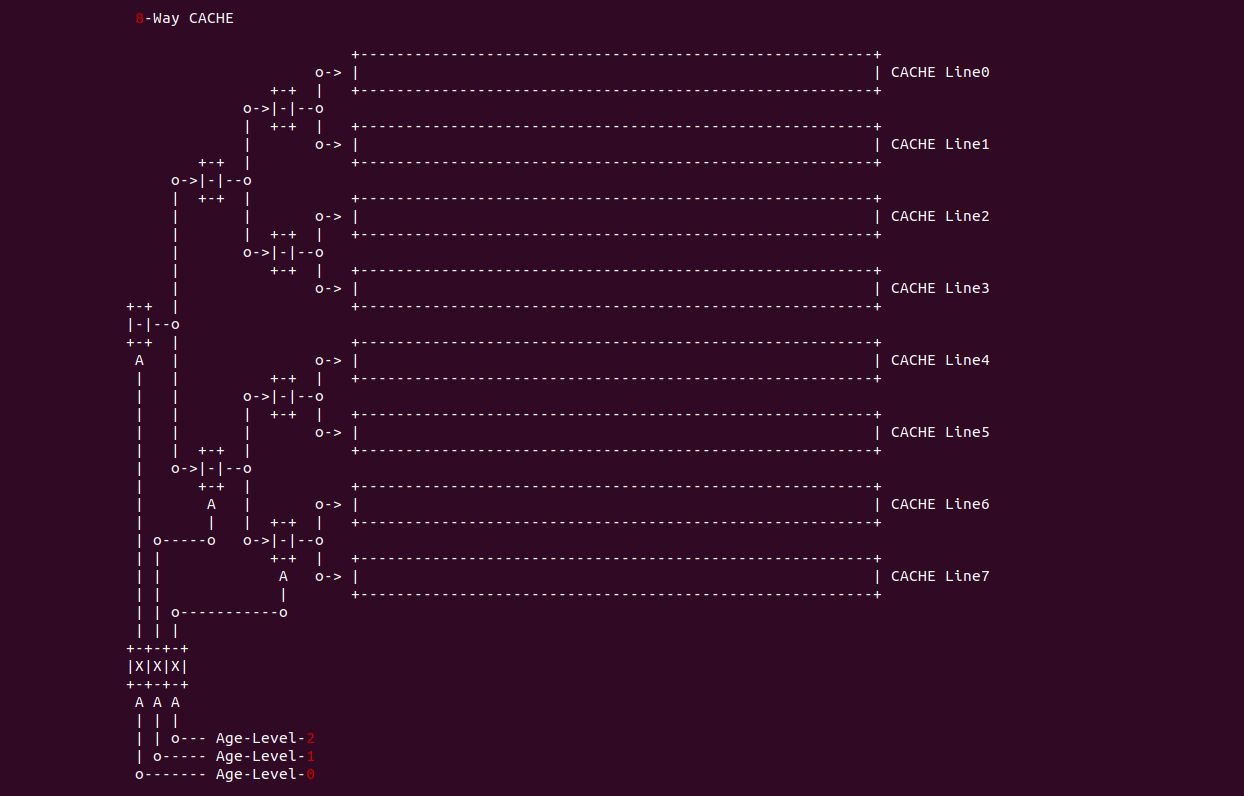

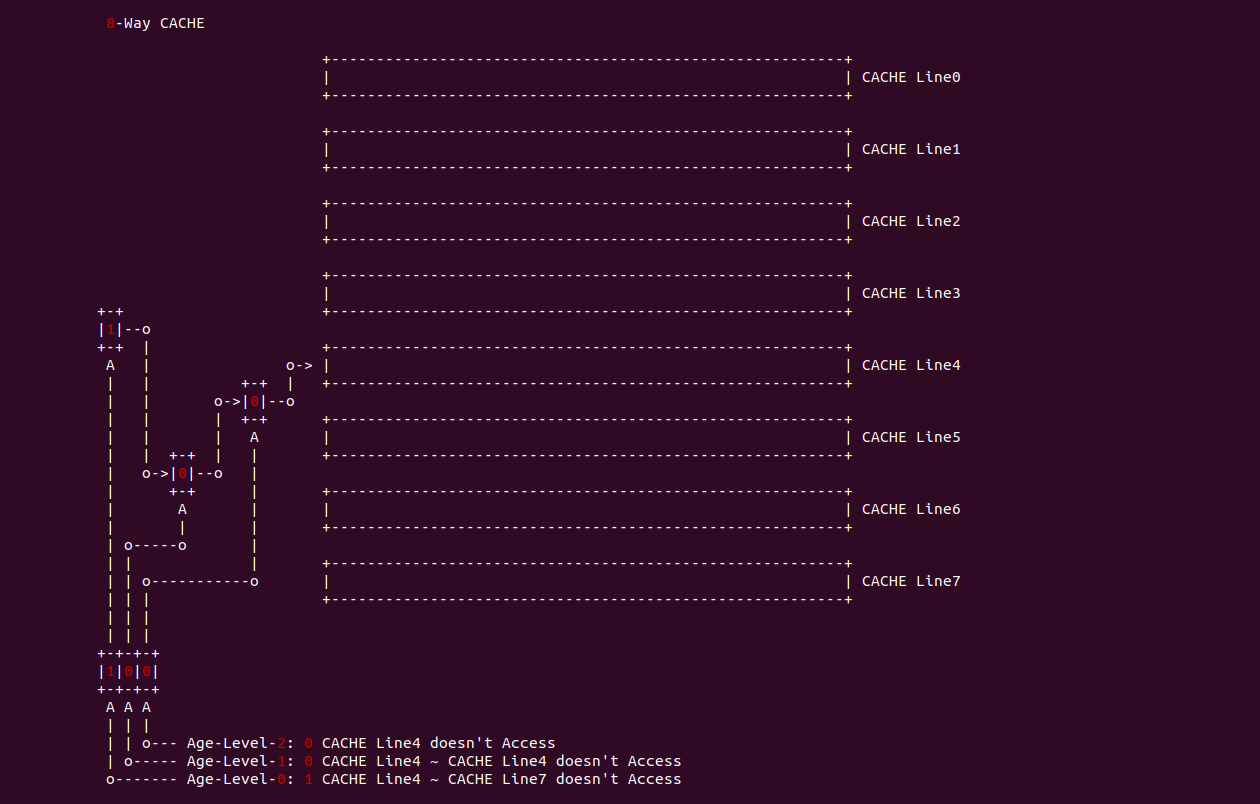

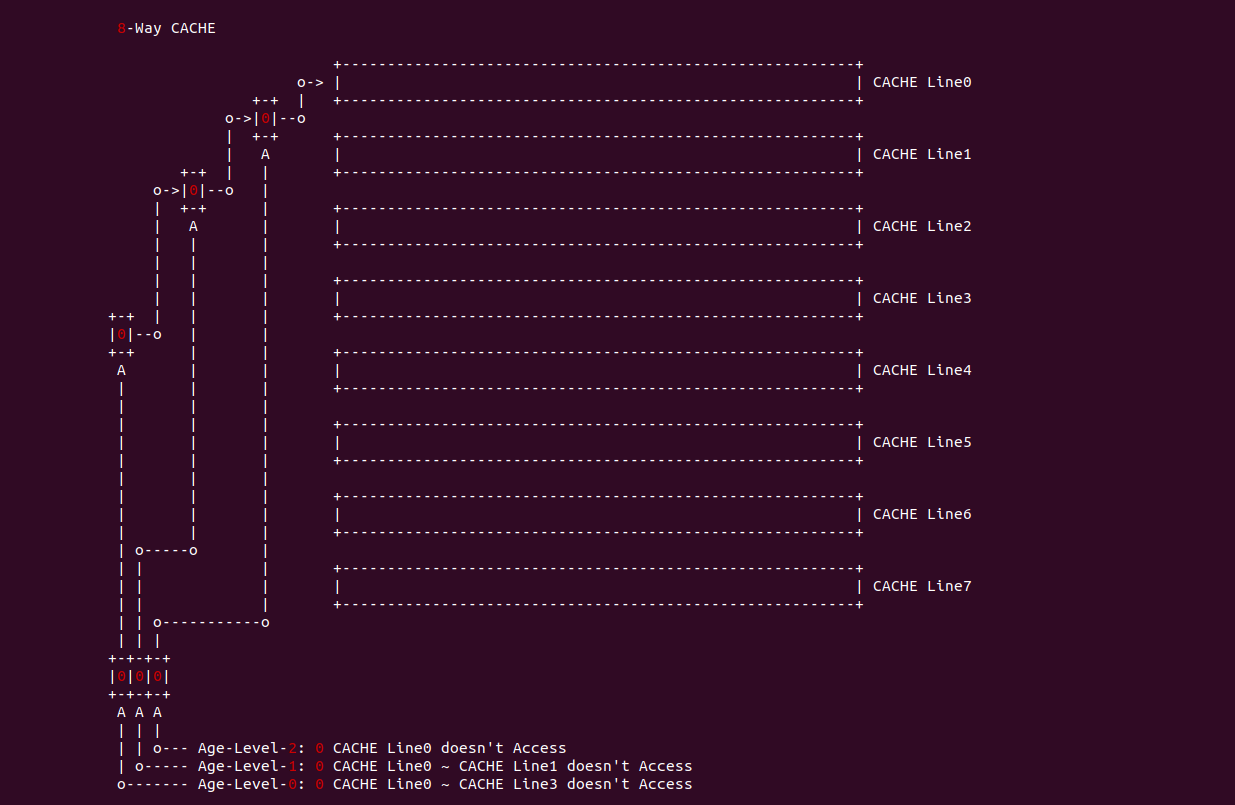

在 8-Way CACHE 中,CACHE Set 采用了 3 个年龄位,每个年龄位被分成不同的年龄级层,Age-level-0 用于将 CACHE Set 中的 CACHE Line 分作两半,当 Age-level-0 置位,那么表示 CACHE Line0 到 CACHE Line3 没有被访问过,反之 Age-level-0 清零,那么 CACHE Line4 到 CACHE Line7 没有被访问过; Age-level-1 则描述 Age-level-0 识别出没有被访问过的 CACHE Line,当 Age-level-1 位清零,那么表示前半部分 CACHE Line 没有被访问过,反之 Age-level-1 位置位,那么表示后半部分的 CACHE Line 被访问过,Age-level-2 依次类推,最终会定位到最近最少被访问的 CACHE Line, 接下来以 CACHE Line4 为例子进行讲解:

当 Age-level-0 置位,那么表示 CACHE Line4 到 CACHE Line7 没有被访问过,那么 Age-level-1 清零表示 CACHE Line4 到 CACHE Line 5 没有被访问过,最后 Age-level-2 清零表示 CACHE Line4 没有被访问过. 再如 CACHE Line0 为例进行讲解:

当 Age-level-0 清零,那么表示 CACHE Line0 到 CACHE Line3 没有被访问过,那么 Age-level-1 清零表示 CACHE Line0 到 CACHE Line1 没有被访问过,最后 Age-level-0 清零,那么表示 CACHE Line0 没有被访问过.

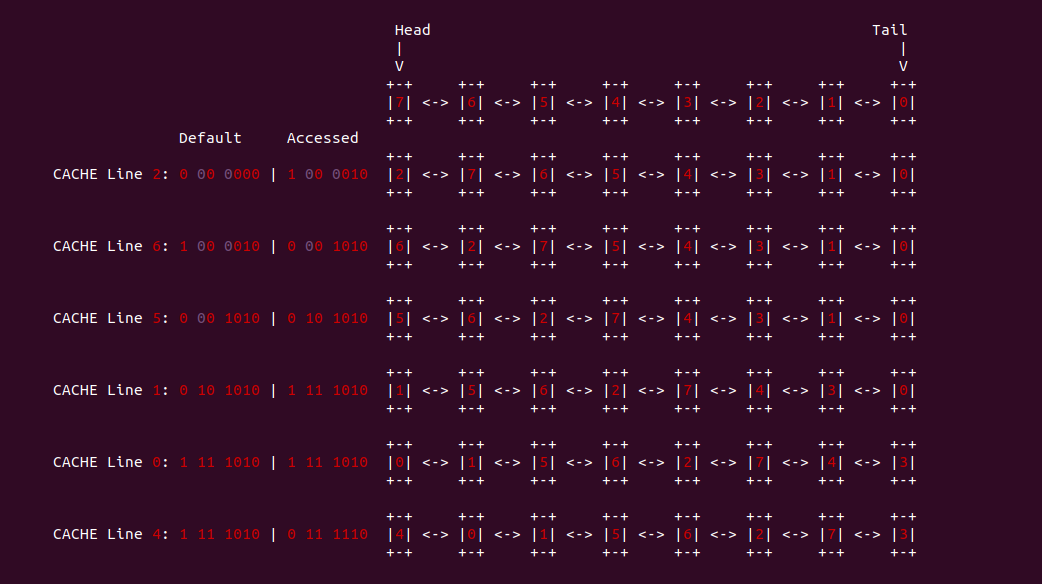

在多路 CACHE 中,需要多个年龄位进行维护,当一个 CACHE Line 被使用,那么它对应的年龄应该被设置为最大,其他 CACHE Line 的年龄按照之前的顺序排在它之后,这个过程类似于把单链表中的某个节点放到了链表表头,其余节点按之前的顺序连接在节点头之后。替换的时候总是替换年龄最小的那个 CACHE Line,也就是单链表表尾替换掉.

LFU(最不经常使用) 策略

LFU(Least Frequently Used) 策略将一段时间内被访问次数最少的 CACHE Line 替换出去,其原理是为每个 CACHE Line 设置一个计数器,从 0 开始计数,每访问以此对应的 CACHE Line 计数器加一。当需要替换时,将计数值最小的 CACHE Line 替换出去,同时将所有的计数器清零. 这种策略将计数周期限定在两次替换之间的时间间隔内,不能严格反应近期访问情况,新调入的块很容易被替换出去.

随机替换策略

随机替换算法完全不管 CACHE 的情况,简单地根据一个随机数选择一块替换出去,随机替换算法在硬件上容易实现,且速度也比前面两种策略块。缺点就是降低了 CACHE 的命中率和 CACHE 工作效率.

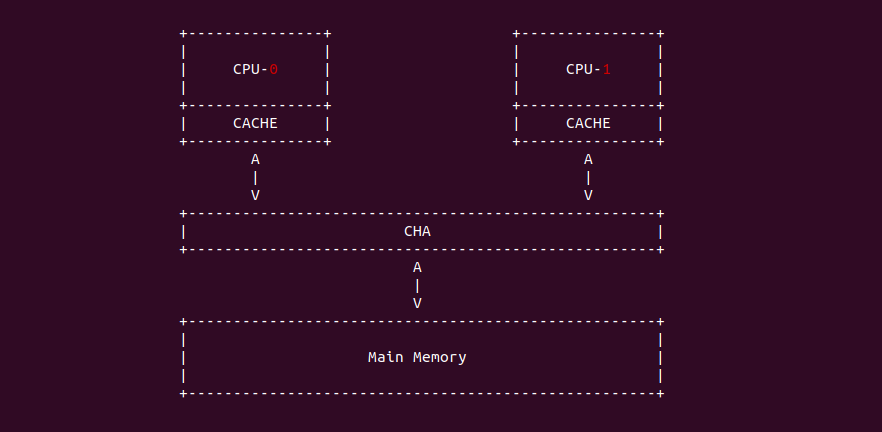

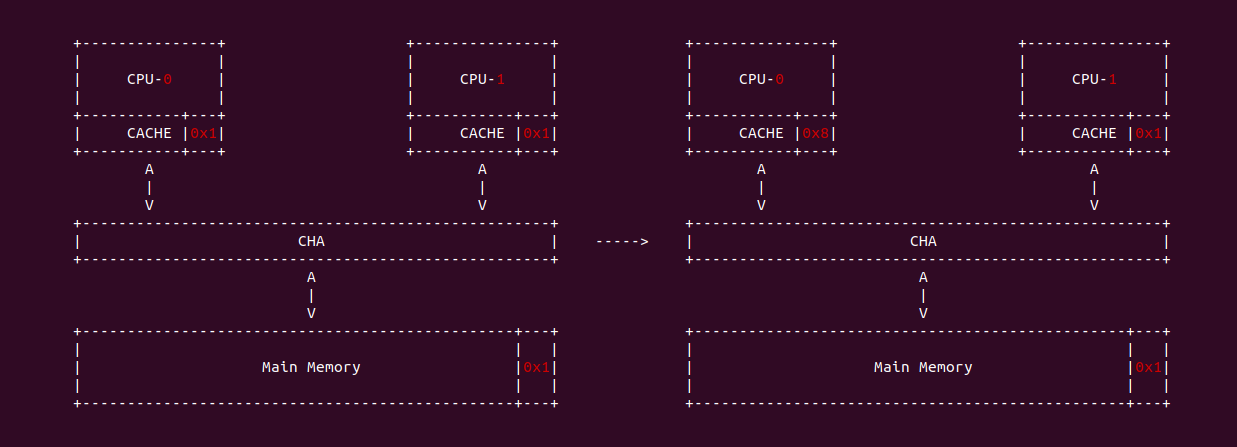

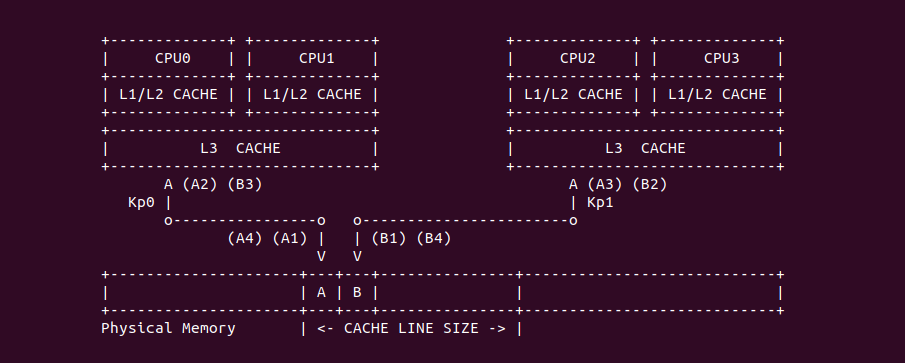

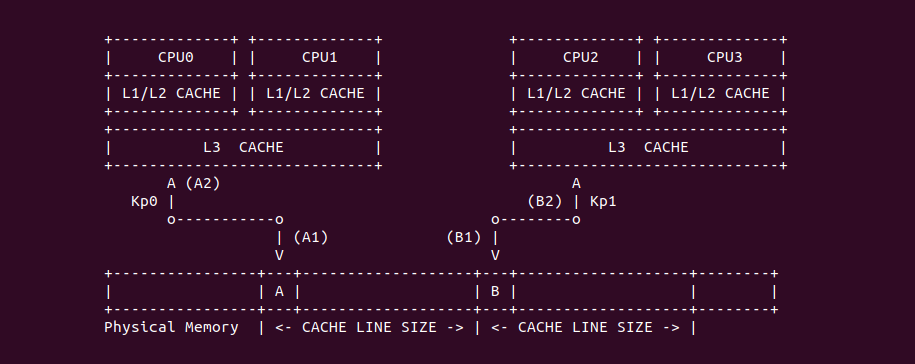

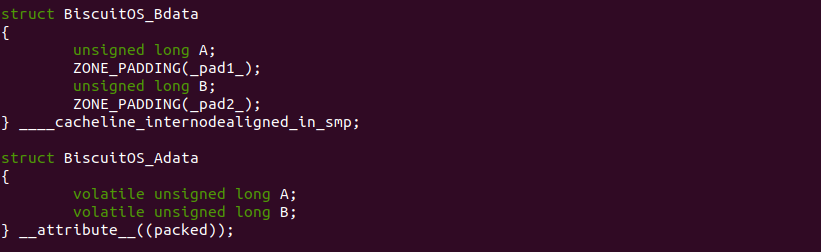

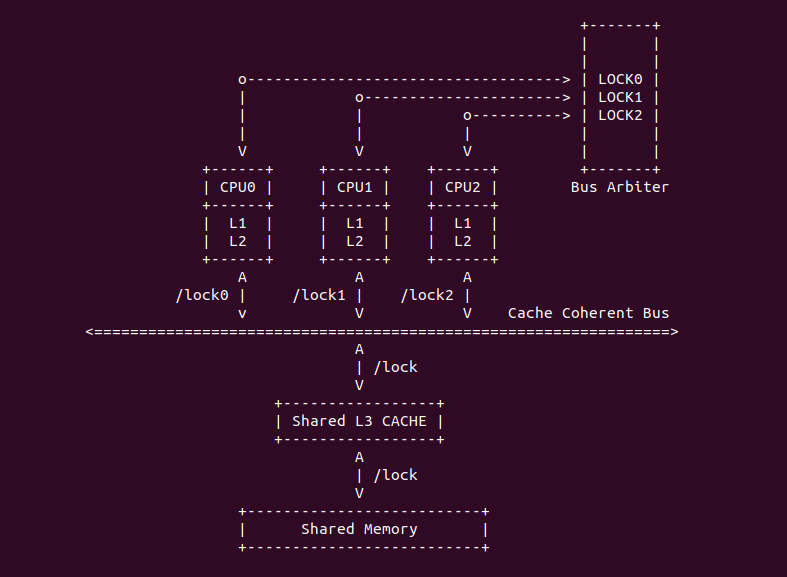

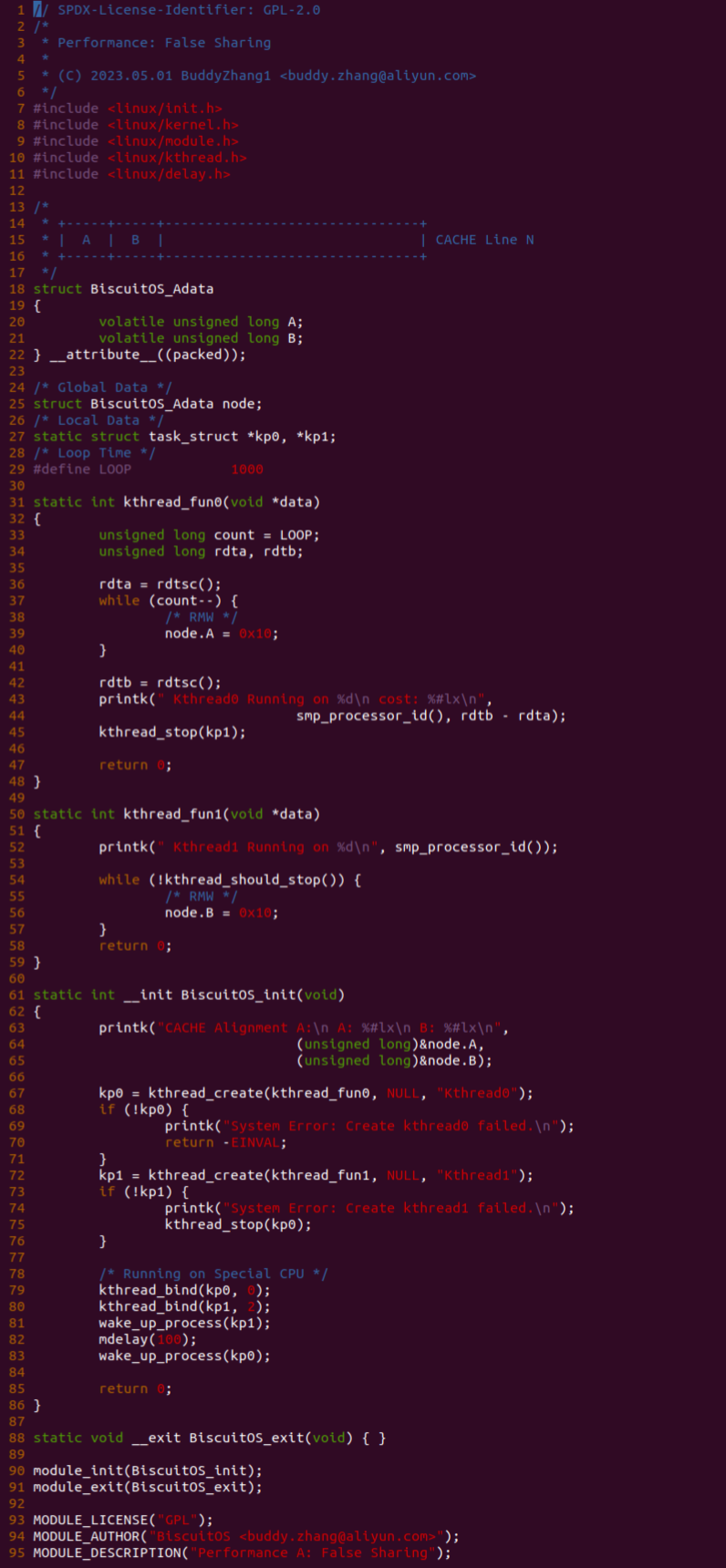

CACHE 一致性

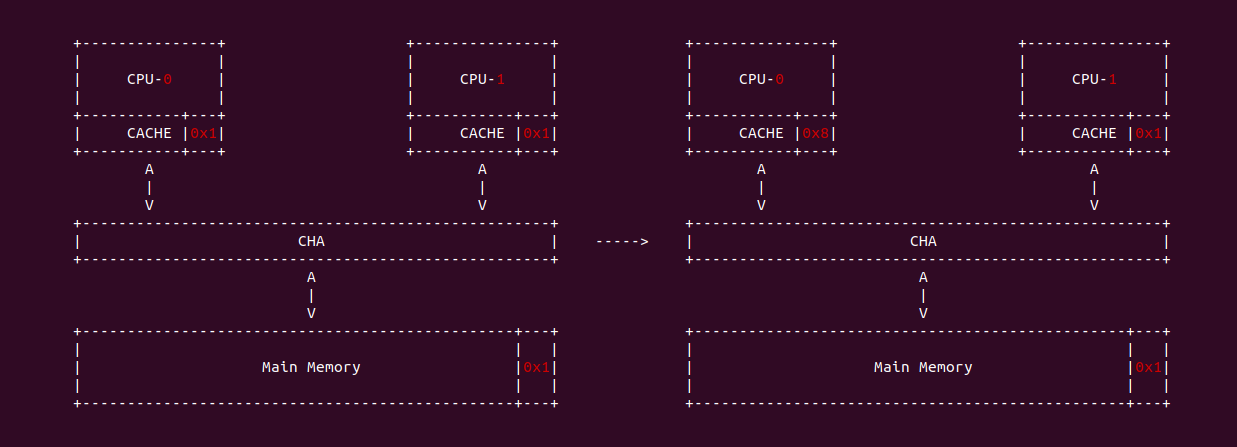

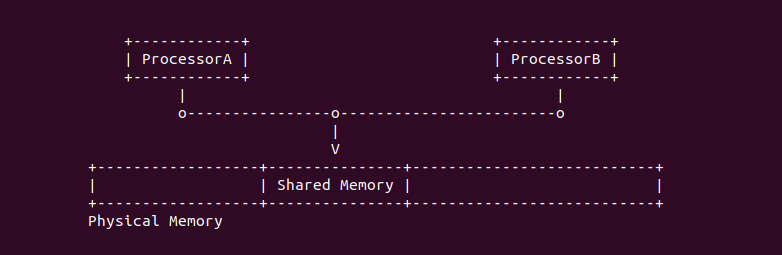

什么是 CACHE 一致性? 先看一个案例,之前的学习中可以知道 CPU-0 访问 Main Memory Data Block X 之后,其会被加载到 CPU-0 CACHE 的某个 CACHE Line,然后 CPU-0 就可以在 CACHE 中访问而不用去主存中访问数据. 在单核年代,CPU 对该数据的修改可以直接在 CACHE Line 中进行,然后配合适合的硬件同步机制再将 CACHE Line 中的数据同步到主存中; 但到了多核年代,CPU-0 CACHE 中缓存了主存 Data Block X, 然而 CPU-0 CACHE 同样也缓存 Data Block X, 那么 CPU-0 修改了 CACHE 中 Data Block X 的数据,同时 CPU-1 读取了 CACHE 中 Data Block X, 此时 Data Block X 在两个 CPU CACHE 的缓存的数据不一致,这种情况称为 CACHE 一致性问题.

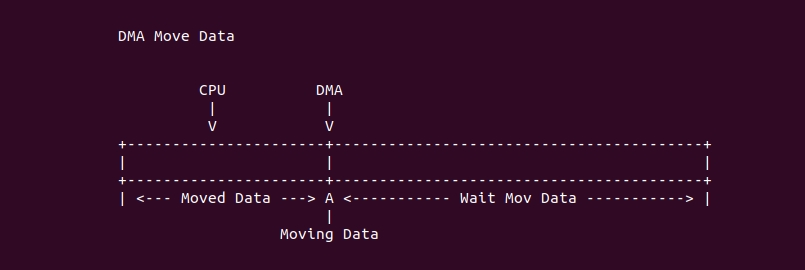

那么如何解决 CACHE 一致性问题呢? 这里通过一个例子进行讲解,当 CPU0 和 CPU1 的 CACHE Line 都缓存了主内存的 Data Block 的数据,且都为 0x1. 当 CPU0 对 Data block 执行写操作并写入 0x8, CPU0 更新了私有 CACHE Line 中的值,同时 CPU1 读取 Data Block 的值,此时 CPU1 发现 CACHE Line 命中,然后直接从私有的 CACHE Line 中读取 0x1. 从这里例子看到造成了 CPU0 和 CPU1 CACHE Line 数据不一致现象, 这样就会导致数据的观察者 (CPU/CPU/DMA) 看到数据不一致,因此维护 CACHE 一致性非常必要。维护 CACHE 一致性的关键就是需要跟踪每个 CACHE Line 的状态,并且根据读写操作和总线上相应的传输内容来更新 CACHE Line 在不同 CPU 上的 CACHE Hit 状态.

维护 CACHE 一致性有软件和硬件两种方式,现在主流架构采用硬件维护. 在处理器中通过 CACHE 一致性协议实现,这些协议维护一个有限状态机, 根据存储器读写指令或总线上的传输内容,进行状态迁移或相应 CACHE Line 操作来维护 CACHE 一致性。CACHE 一致性协议主要分为两大类:

- 监听协议: 每个 CACHE Line 被监听或者监听其他 CACHE Line 的总线活动

- 目录协议: 全局统一管理 CACHE Line 状态

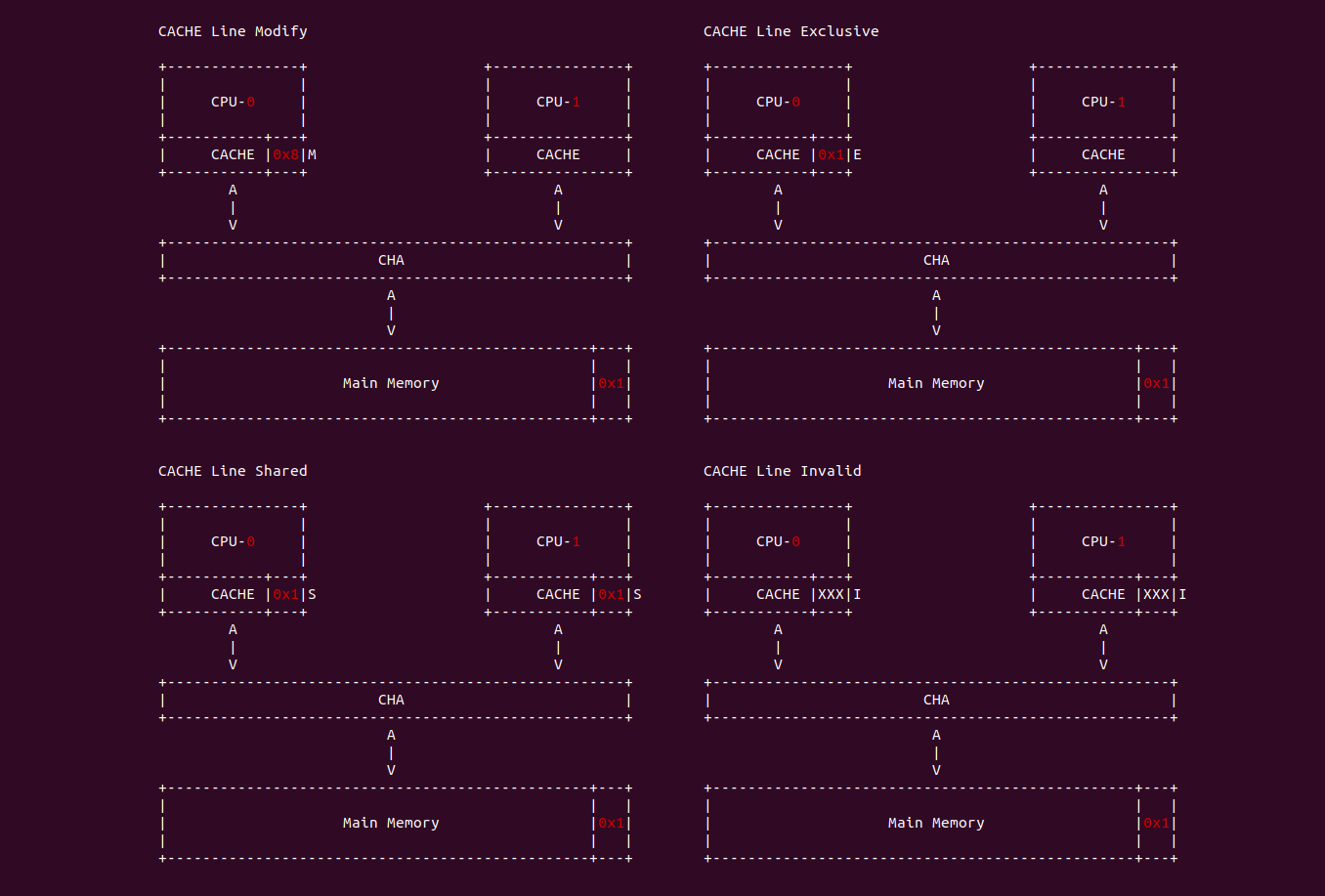

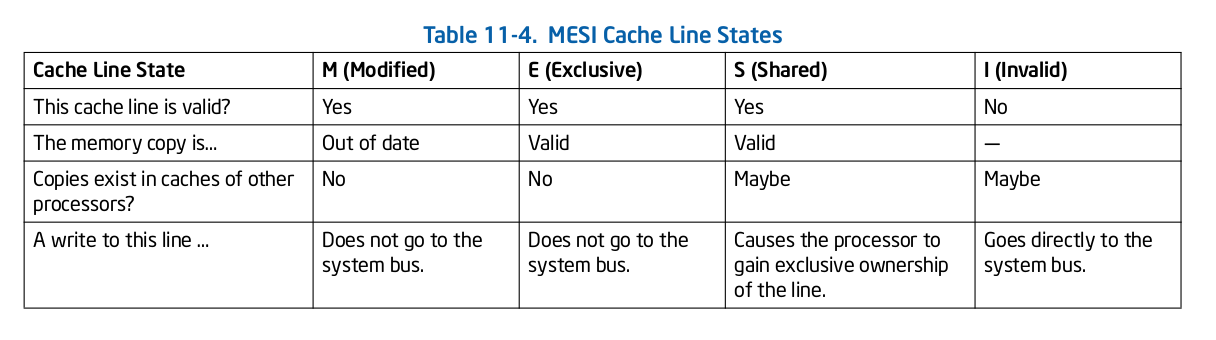

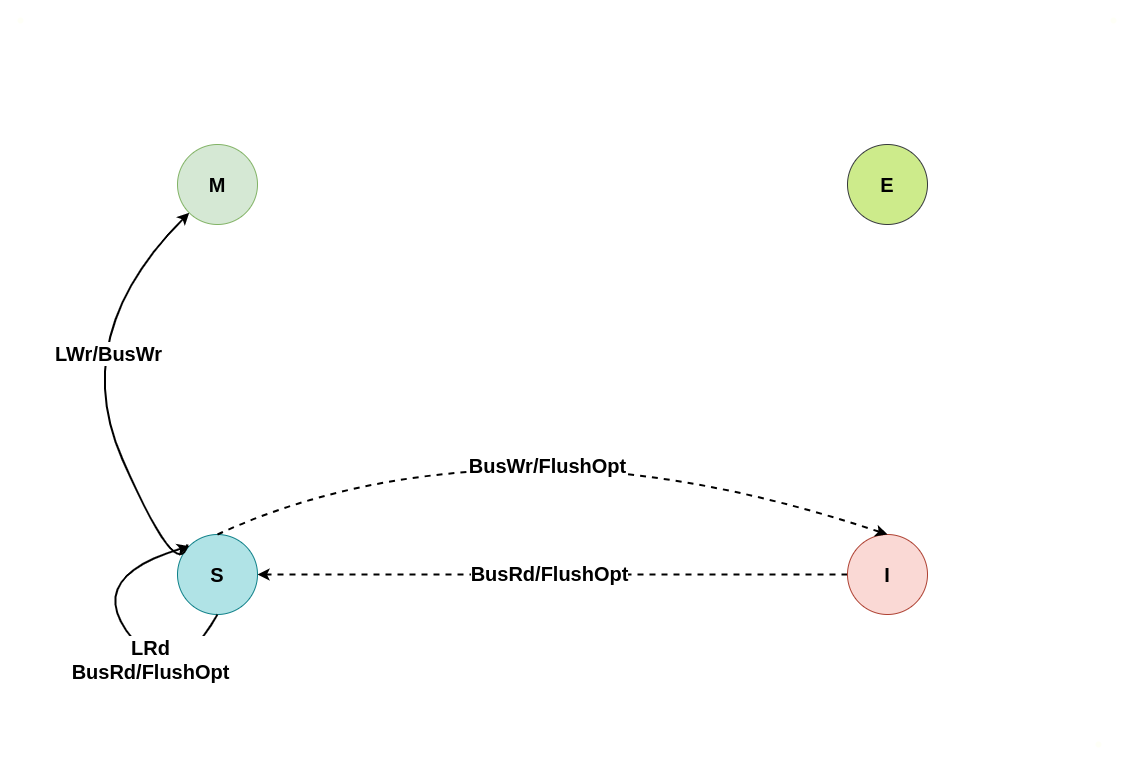

这里介绍主流的 MESI 协议(Write-Once 总线监听协议), MESI 分别代表 Modify、Exclusive、Shared 和 Invalid. CACHE Line 的状态必须是其中的一种。前三种状态均是数据有效下的状态, CACHE Line 的 Flags 域包含了两个标志: Dirty 和 Valid,Dirty 置位代表该 CACHE Line 与主存 Data Block 内容不一致,Valid 置位则代表 CACHE Line 是有效的.

MESI

- M(Modify): CACHE Line 数据已经被修改,与主存中数据不一致,该数据只缓存在本地 CACHE Line 中,其他 CPU 没有缓存该副本.

- E(Exclusive): CACHE Line 中的数据与主存一致,且该数据只在本地 CACHE Line 中,其他 CPU 没有缓存该副本.

- S(Shared): CACHE Line 中的数据与主存一致,且多个 CACHE Line 都缓存该数据.

- I(Invalid): 该 CACHE Line 没有缓存该数据.

MESI 在总线上的操作分为本地读写和总线操作. 当操作类型为本地读写时, CACHE Line 的状态指的是本地 CPU(Local CPU); 而当操作类型为总线读写时,CACHE Line 的状态指的是远端 CPU(Remote CPU):

- 本地读: 本地 CPU 读取 CACHE Line.

- 本地写: 本地 CPU 更新 CACHE Line.

- 总线读/远端读: 总线监听一个来自远端 CPU 的读 CACHE 信号. 收到信号的 CPU 先检查 CACHE 是否存在该数据,然后广播应答

- 总线写/远端写: 总线监听一个来自远端 CPU 的写 CACHE 信号. 收到信号的 CPU 先检查 CACHE 是否存在该数据,然后广播应答

- 总线更新: 总线收到更新请求,请求其他 CPU 干活. 其他 CPU 收到请求后,若 CPU 有 CACHE 副本,则使其 CACHE Line 无效.

- 刷新: 总线监听到刷新请求,收到请求的 CPU 将本地 CACHE Line 内容写入主内存

- 刷新到总线: 收到该请求的 CPU 将本地 CACHE Line 发送到总线上,发起请求的 CPU 会获取该 CACHE Line 的内容.

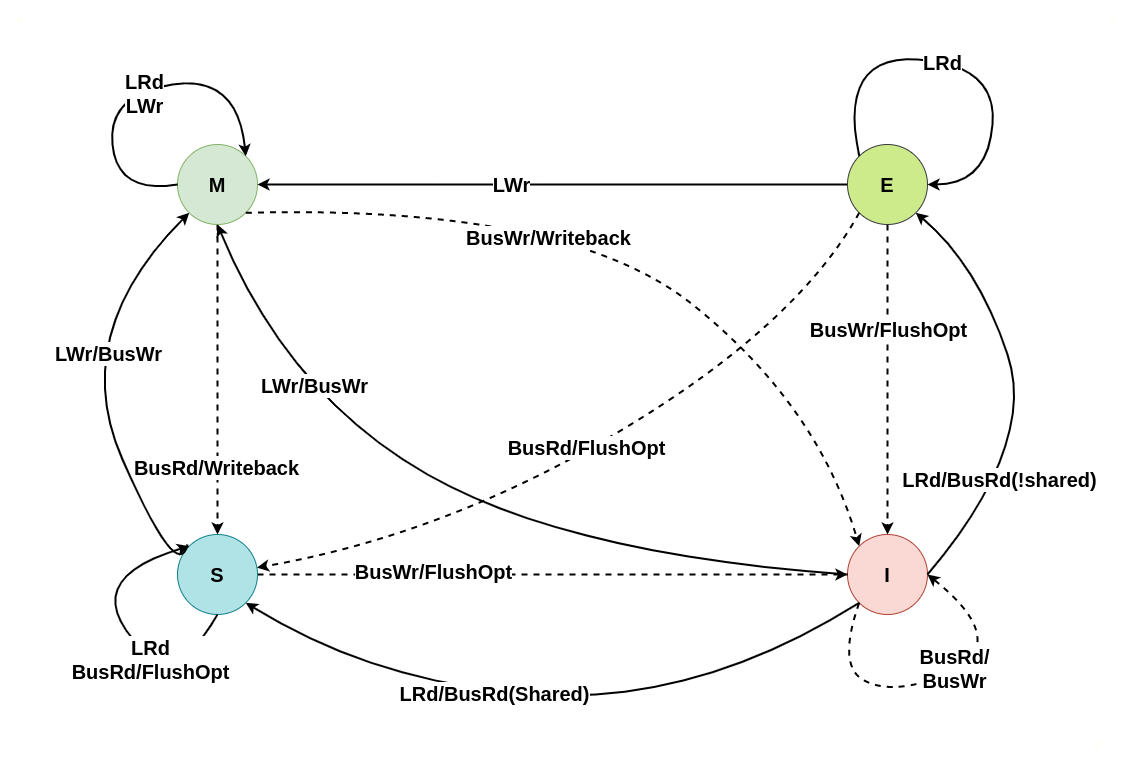

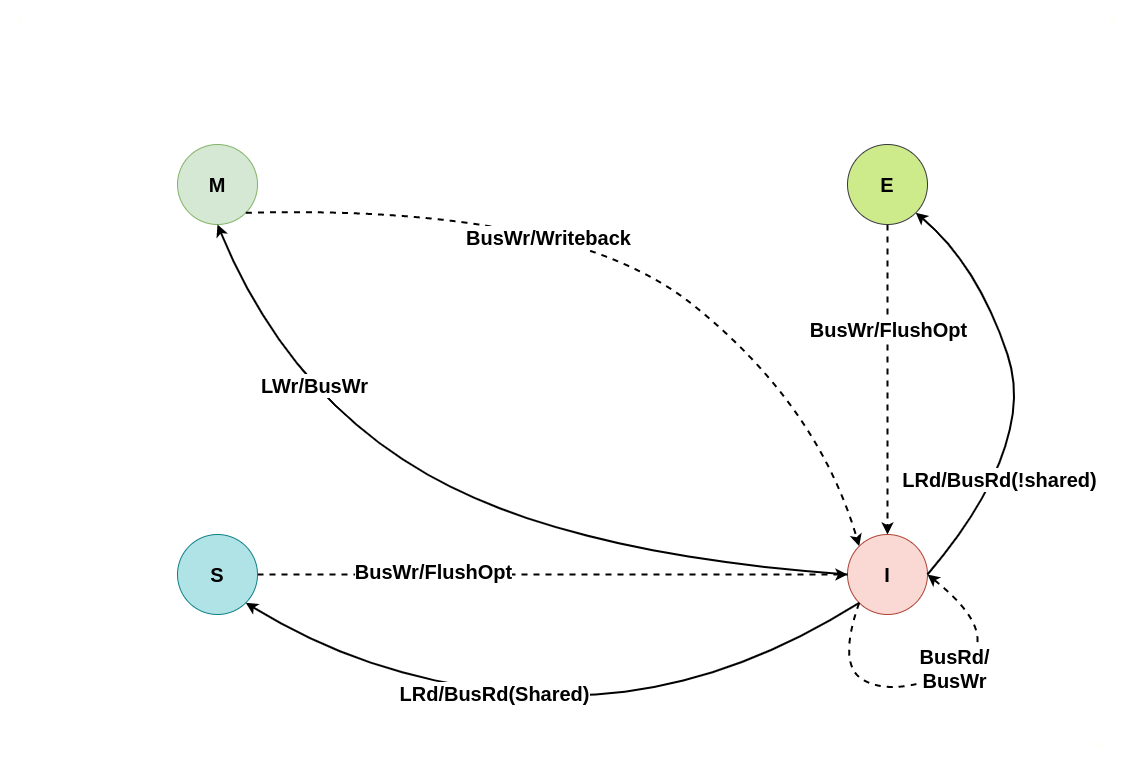

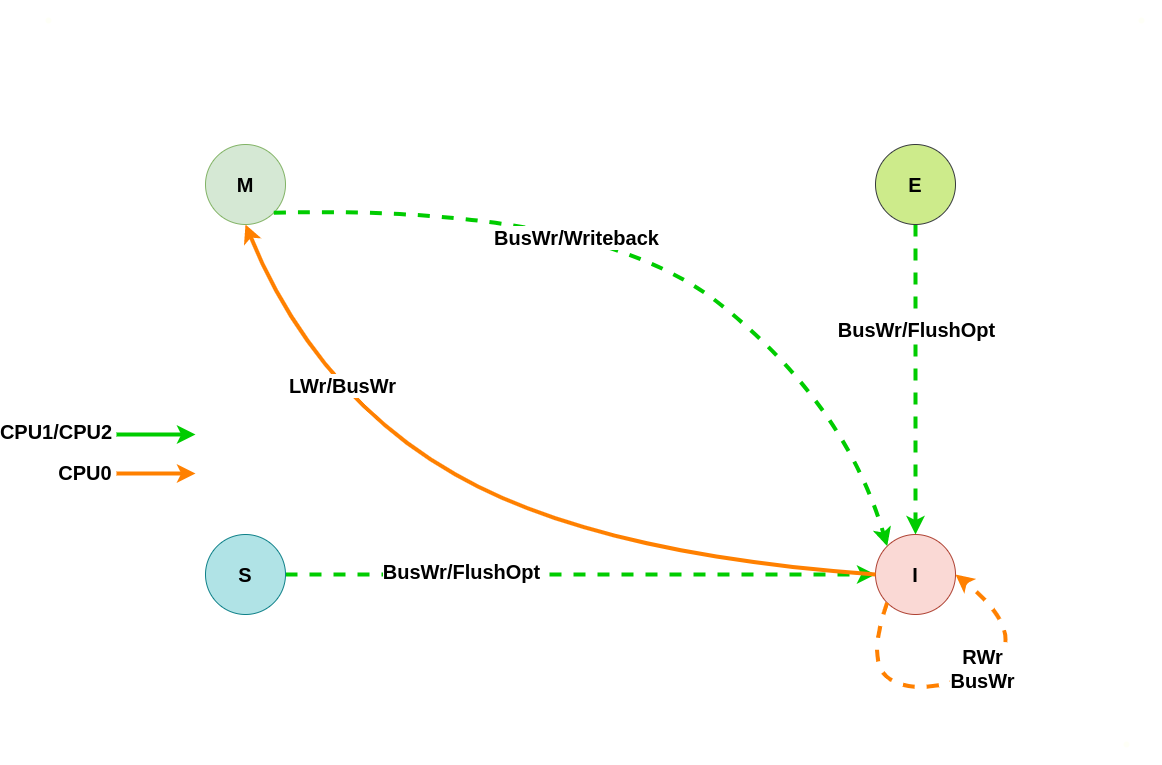

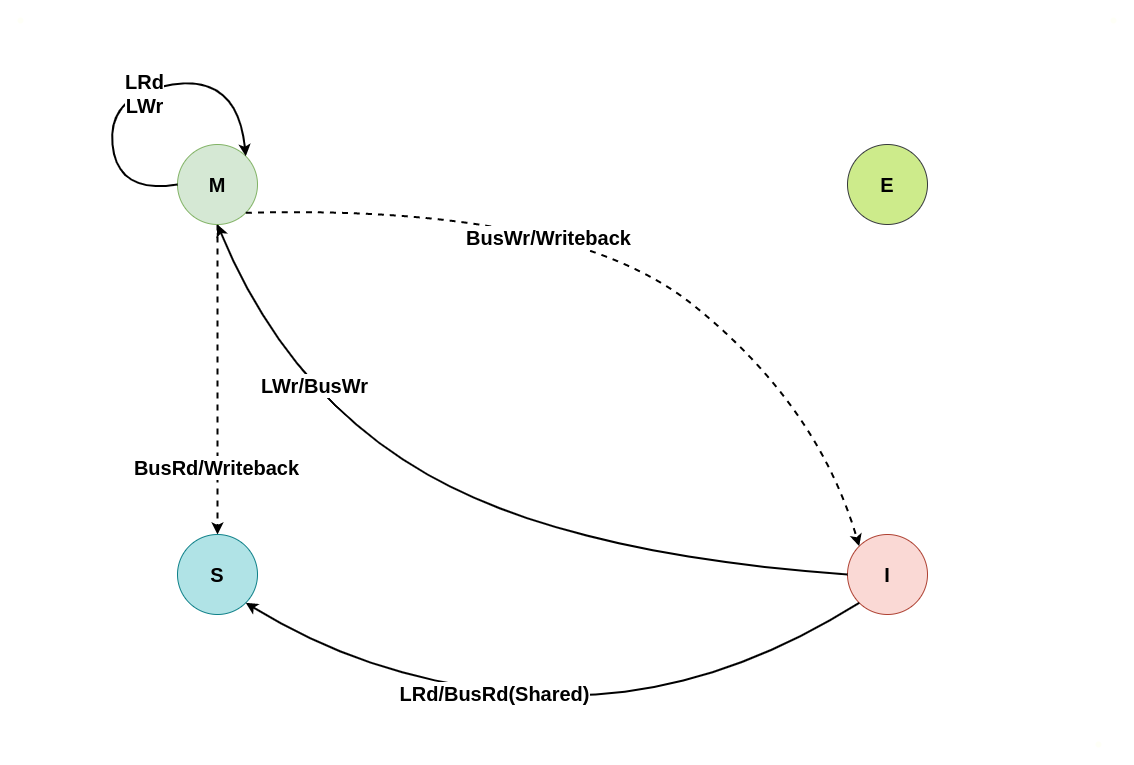

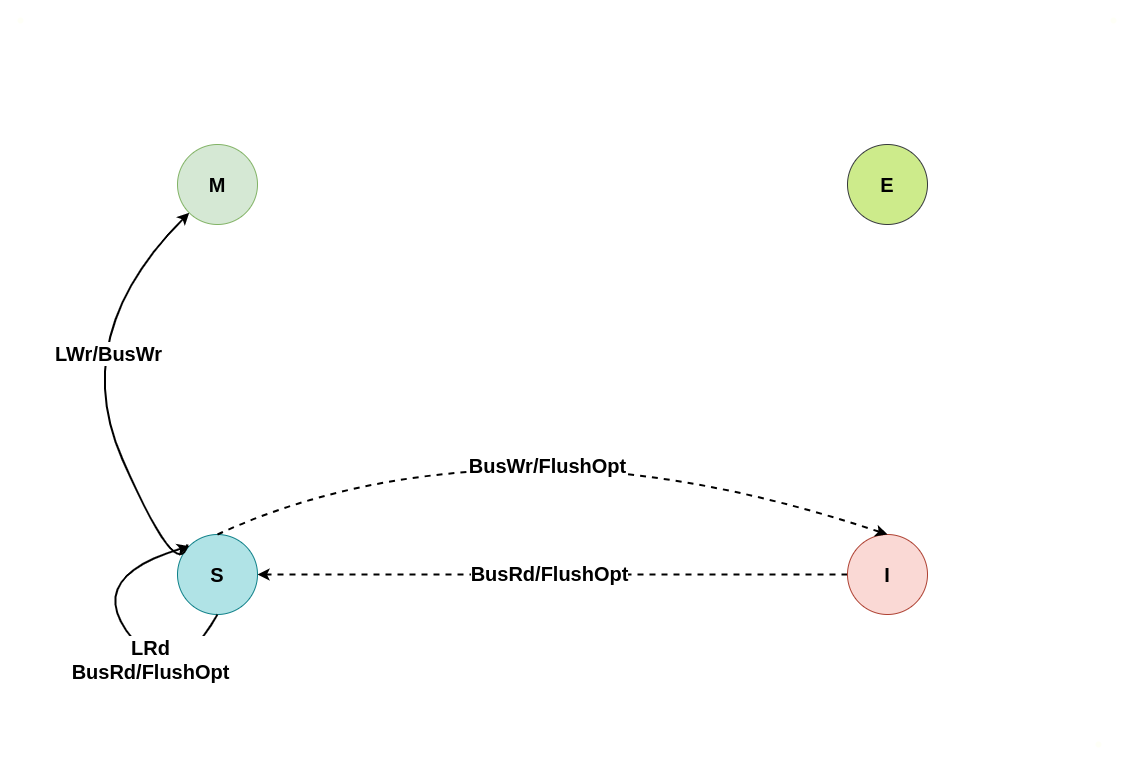

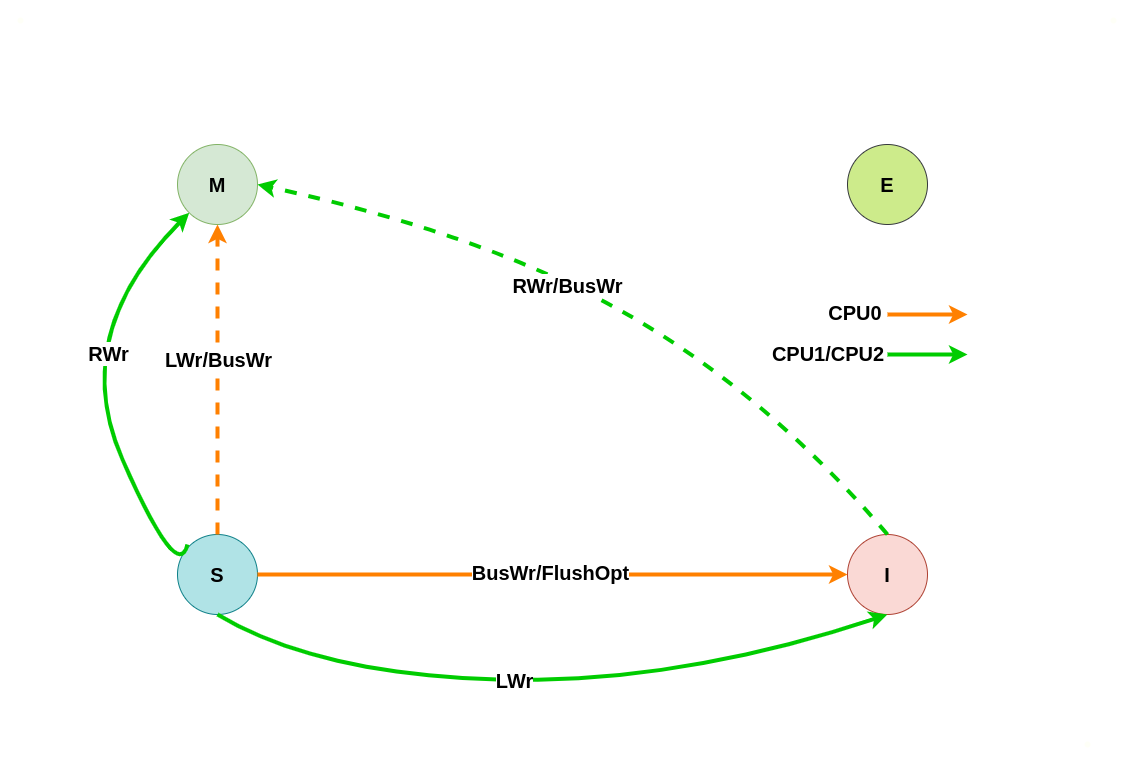

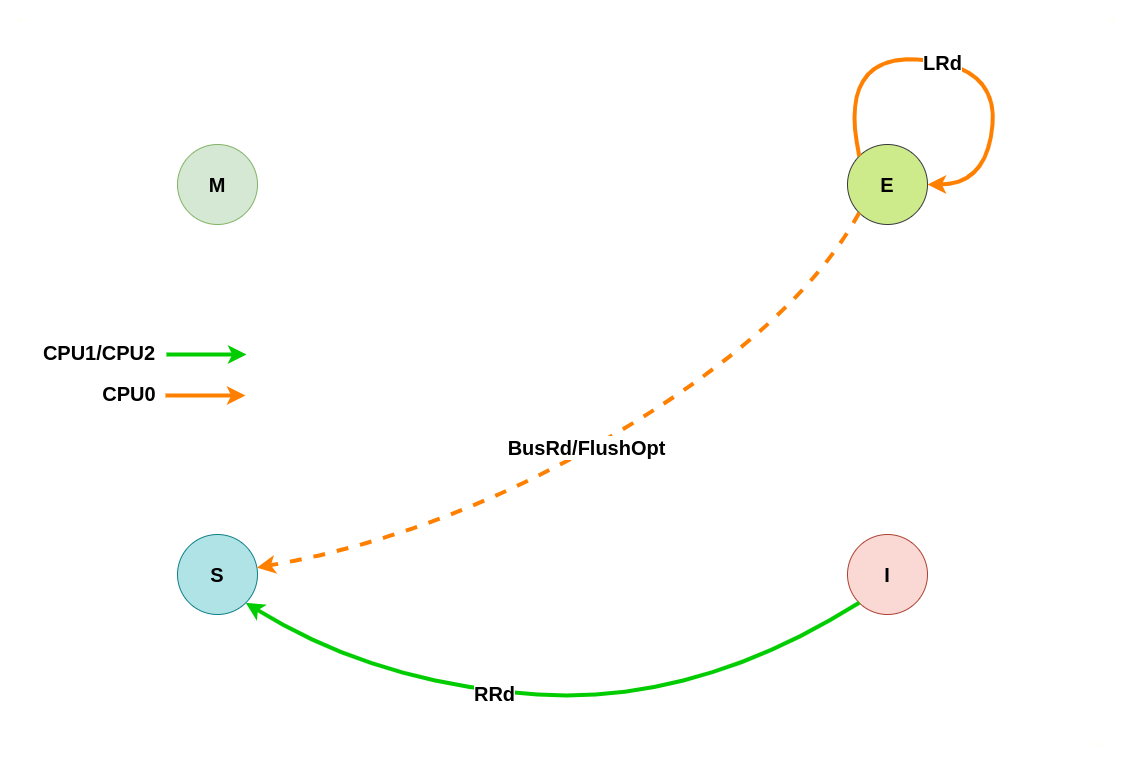

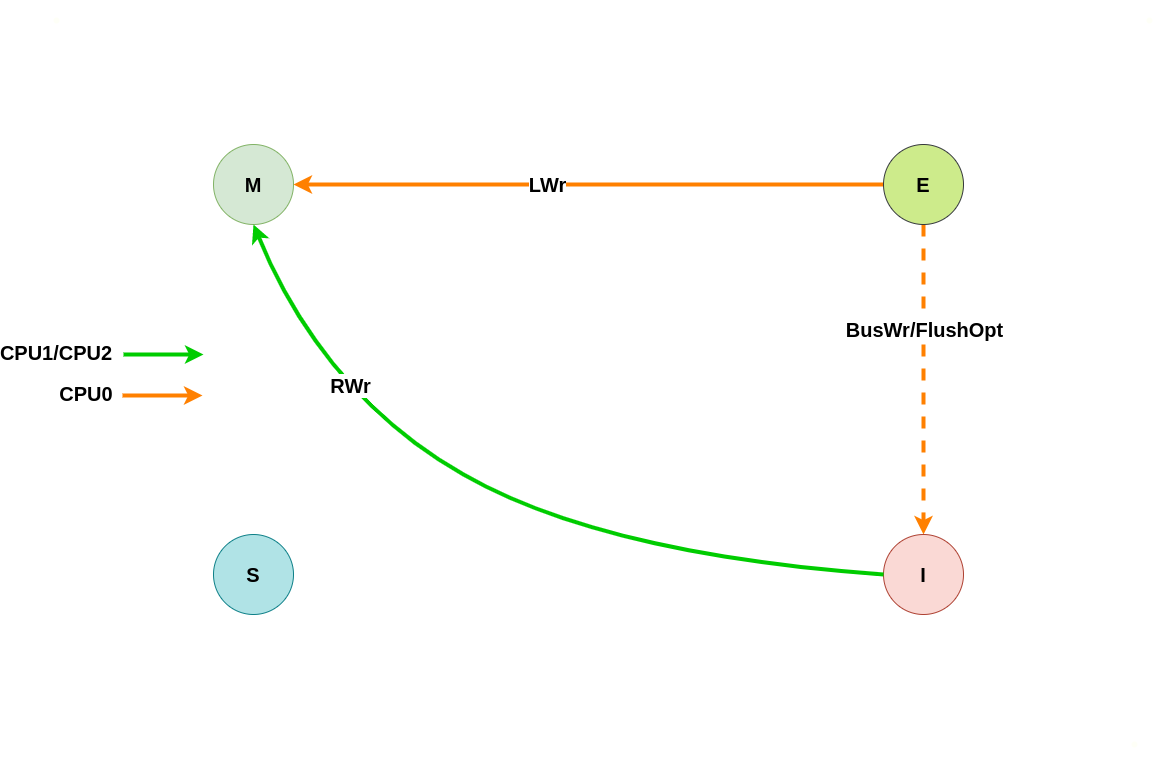

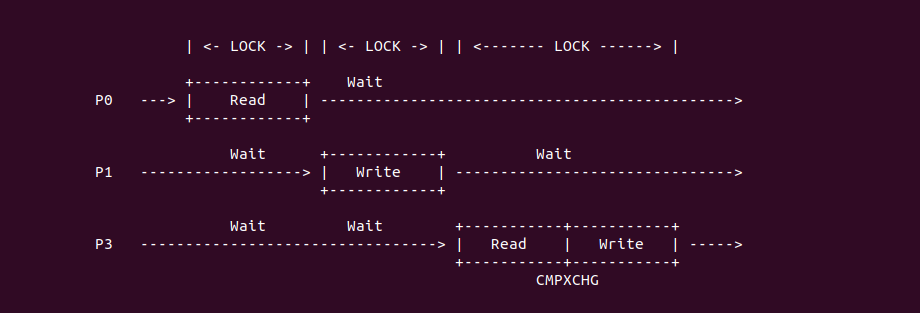

上图为 MESI 之间变换的状态图,LRd 表示本地读、LWr 表示本地写、BusRd 表示远端读或者监听到总线读请求、BusWr 表示远端写或监听到总线写请求、FlushOpt 表示把当前 CACHE Line 内容发到总线上、Writeback 表示将 CACHE Line 内容更新到内存. 接下来通过具体理解讲解每种状态之间变化过程:

初始状态为 Invalid

当本地 CACHE Line 的状态为 Invalid 时,其会触发本地 CPU 访问时 CACHE Miss,此时无论是本地读还是本地写,都会转换成总线读或者总线写信号,远端 CPU 的 CACHE 监听到总线信号之后会将其缓存的 CACHE Line 状态进行改变,具体改变可以从读请求和写请求进行分析:

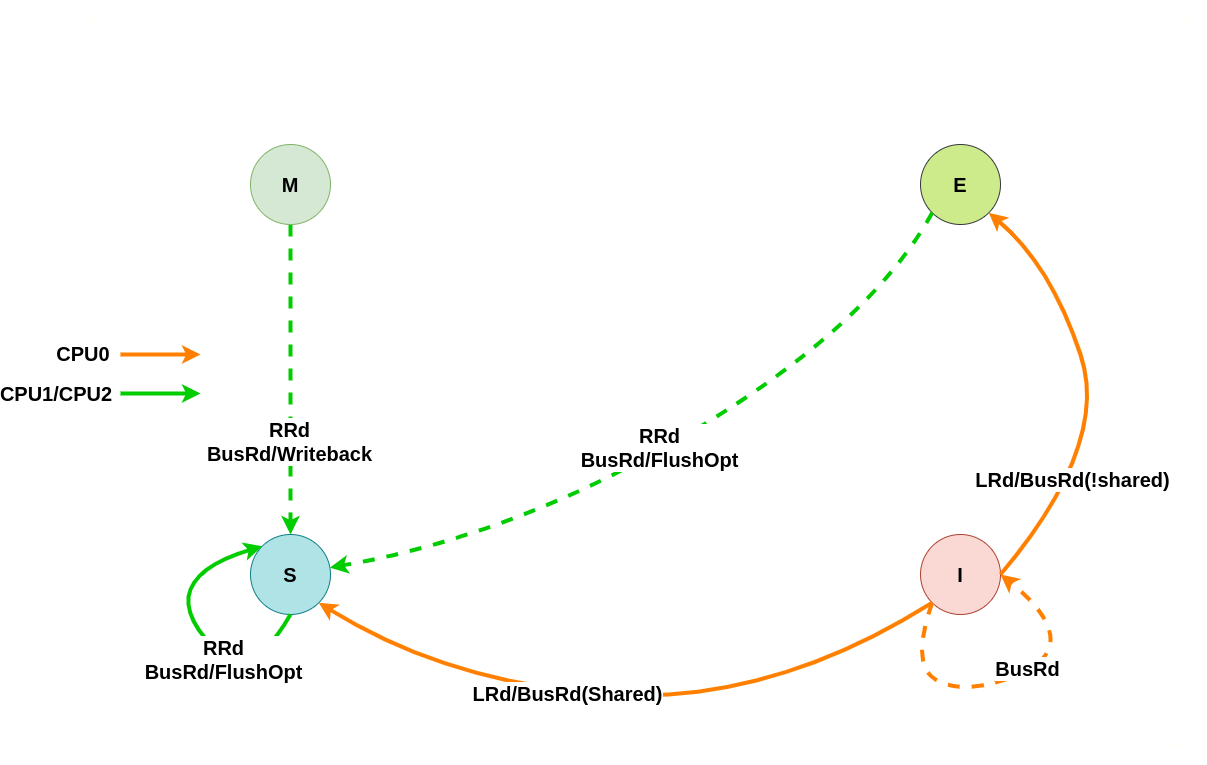

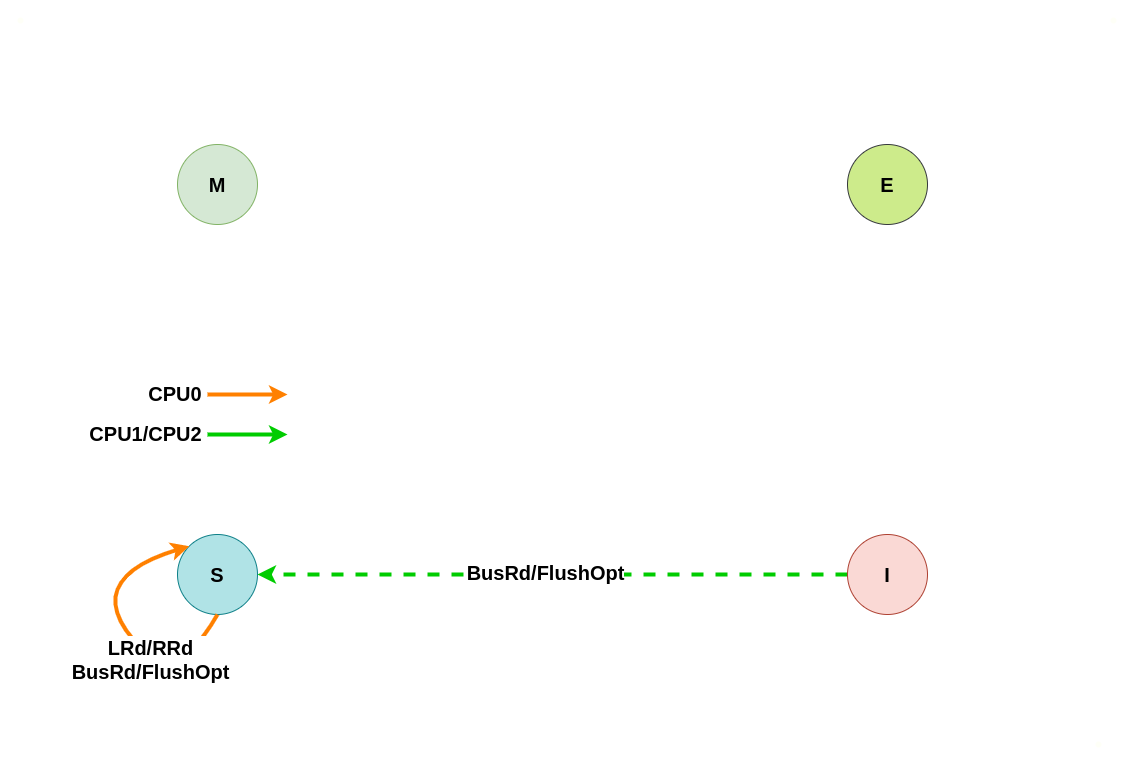

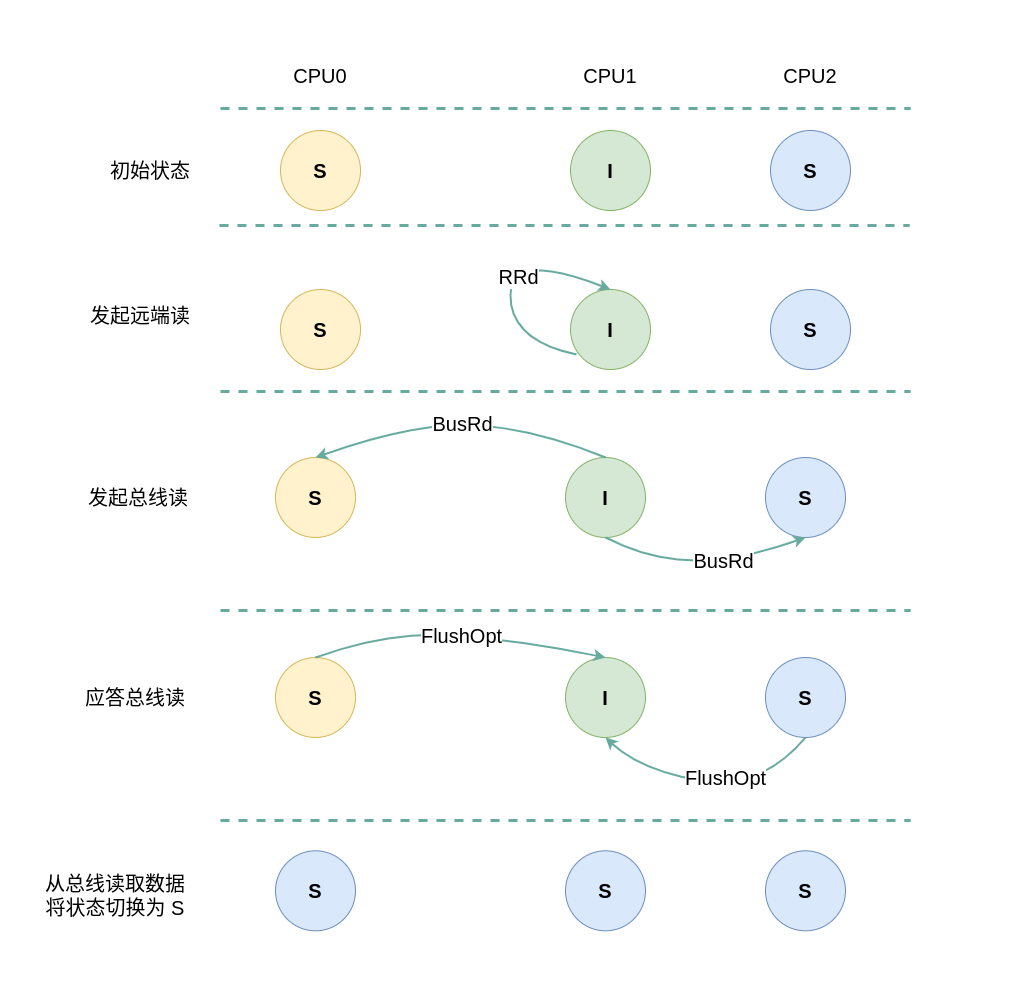

本地/远端读请求

假设系统有 3 个 CPU,分别是 CPU0、CPU1 和 CPU2,并且 CPU0 为本地视角,CPU1 和 CPU2 为远端视角. 当 CPU0 发起本地读请求 LRd 或者 CPU1/CPU2 发起远端读请求 RRd 时,此时 CPU0 对应的 CACHE Line 为 Invalid,CPU1、CPU2 对应的 CACHE Line 的状态可能是 Invalid、Shared 或者 Exclusive, 那么所有 CACHE Line 的变化包含如下几种情况:

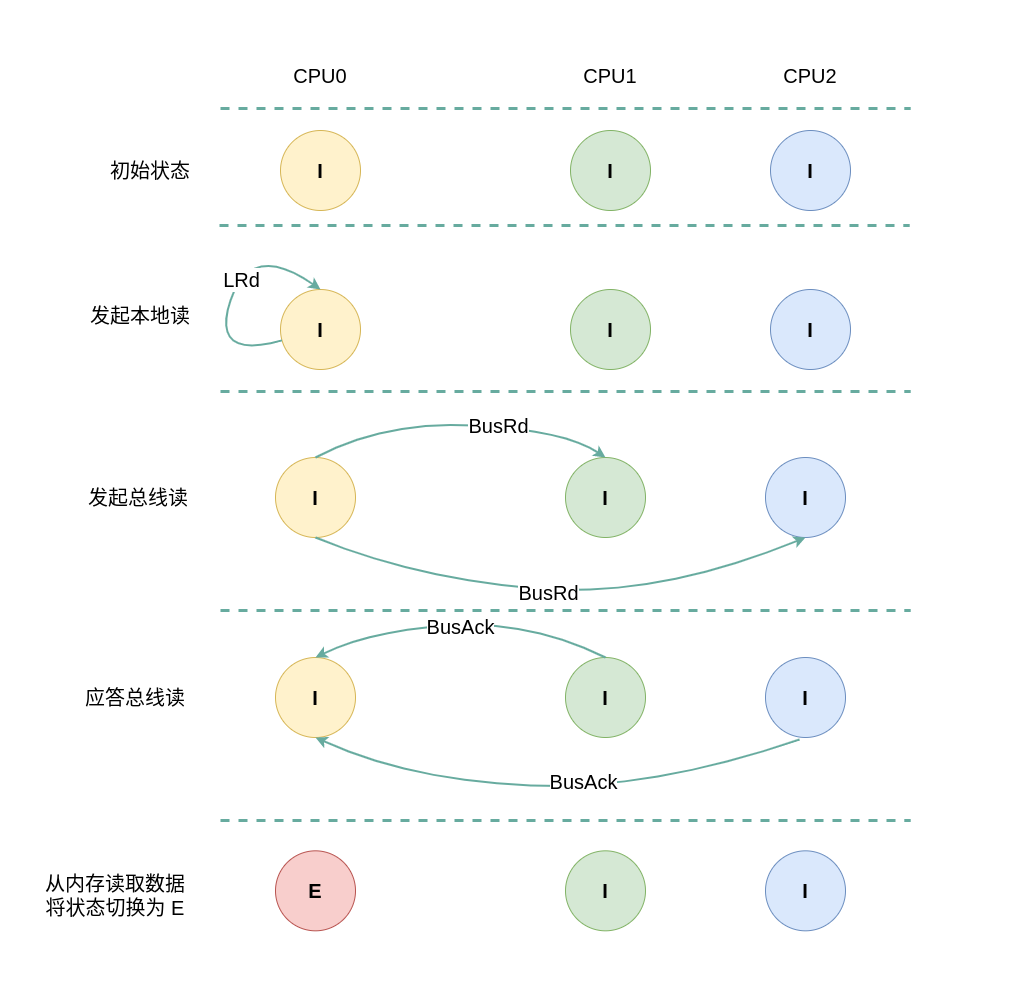

(1) 本地读全 Invalid: 当 CPU0 发起本地读请求 LRd 时,发现本地 CACHE Line 的状态为 Invalid,即 CACHE 中没有缓存对应的内容 CACHE Miss,那么在总线上产生一个 总线读 BusRd,CPU1 和 CPU2 监听到 BusRd 之后检查 CACHE 中是否包含副本,此时 CPU1 和 CPU2 的 CACHE Line 都为 Invalid,没有包含副本, 接着 CPU1 和 CPU2 向总线发送应答信号. CPU0 广播完所有的 CPU 之后发现总线上并没有数据,那么其从内存中读取数据到本地 CACHE Line,并将 CACHE Line 的状态切换到 Exclusive.

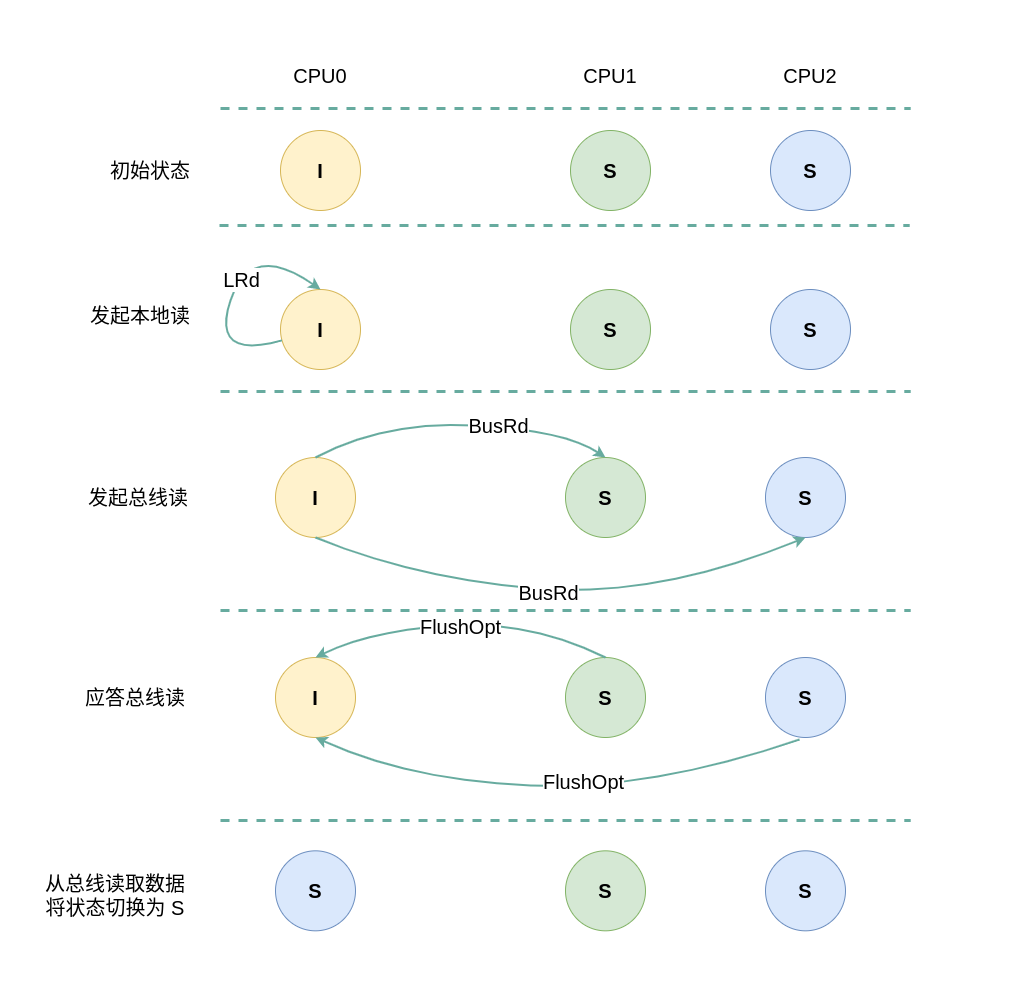

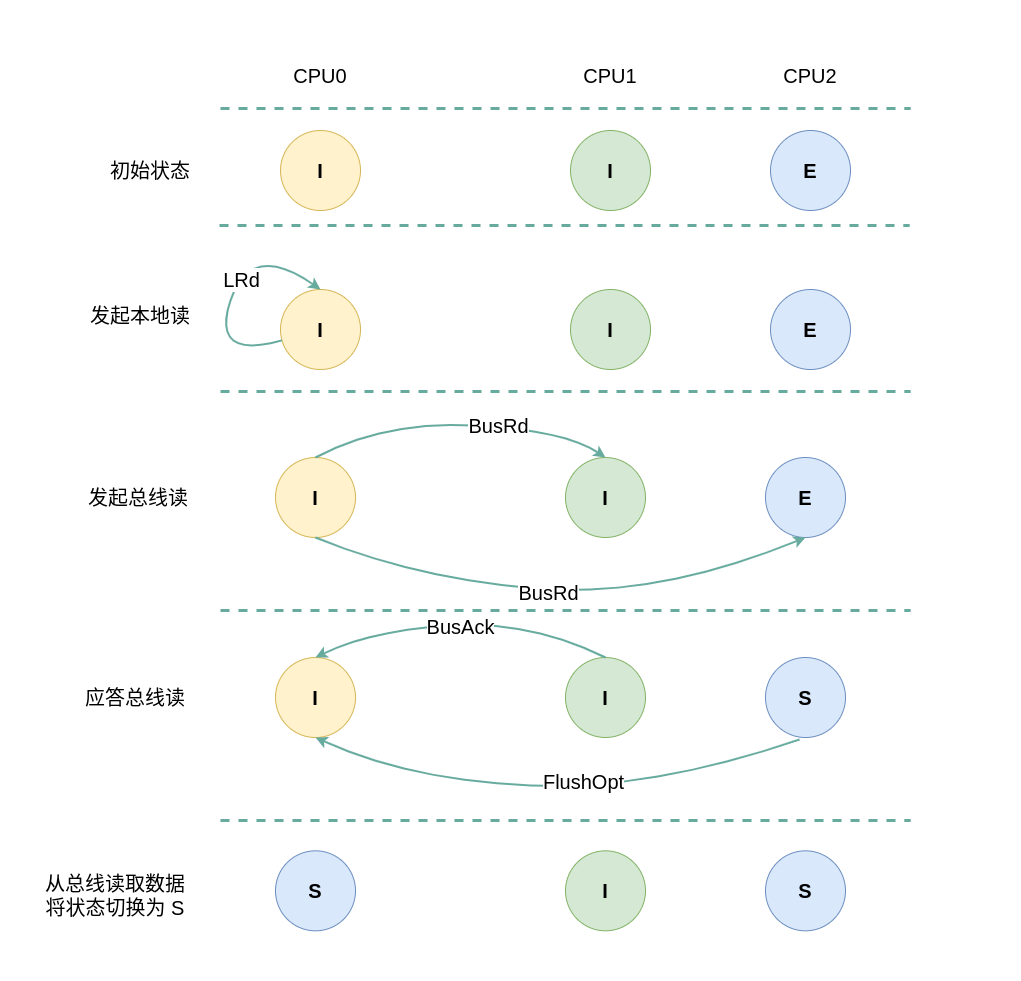

(2) 本地读远端 Shared: 当 CPU0 发起本地读请求 LRd 时,发现本地 CACHE Line 的状态为 Invalid,即 CACHE 中没有缓存对应的内容 CACHE Miss,那么在总线上产生一个 总线读 BusRd,CPU1 和 CPU2 监听到 BusRd 之后检查 CACHE 中是否包含副本,此时 CPU1 和 CPU2 检查到其缓存了副本,且 CACHE Line 的状态为 Shared,那么 CPU1/CPU2 向总线回复一个 FlushOpt 信号,并将 CACHE Line 的内容发送到总线上. CPU0 收到 FlushOpt 信号之后从总线上读取了数据并缓存到本地的 CACHE Line,并将 CACHE Line 的状态标记为 Shared.

(3) 本地读远端 Exclusive: 当 CPU0 发起本地读请求 LRd 时,发现本地 CACHE Line 的状态为 Invalid,即 CACHE 中没有缓存对应的内容 CACHE Miss,那么在总线上产生一个 总线读 BusRd,CPU1 和 CPU2 监听到 BusRd 之后检查 CACHE 中是否包含副本,此时 CPU1 的 CACHE Line 都为 Invalid,那么没有包含副本,那么 CPU1 直接向总线发送应答信号; CPU2 检查到其缓存了副本,且该 CACHE Line 的状态为 Exclusive,那么 CPU2 向总线回复一个 FlushOpt 信号,并将 CACHE Line 的内容发送到总线上, 并将 CACHE Line 的状态切换成 Shared. CPU0 收到 FlushOpt 信号之后从总线上读取了数据并缓存到本地的 CACHE Line,并将 CACHE Line 的状态标记为 Shared.

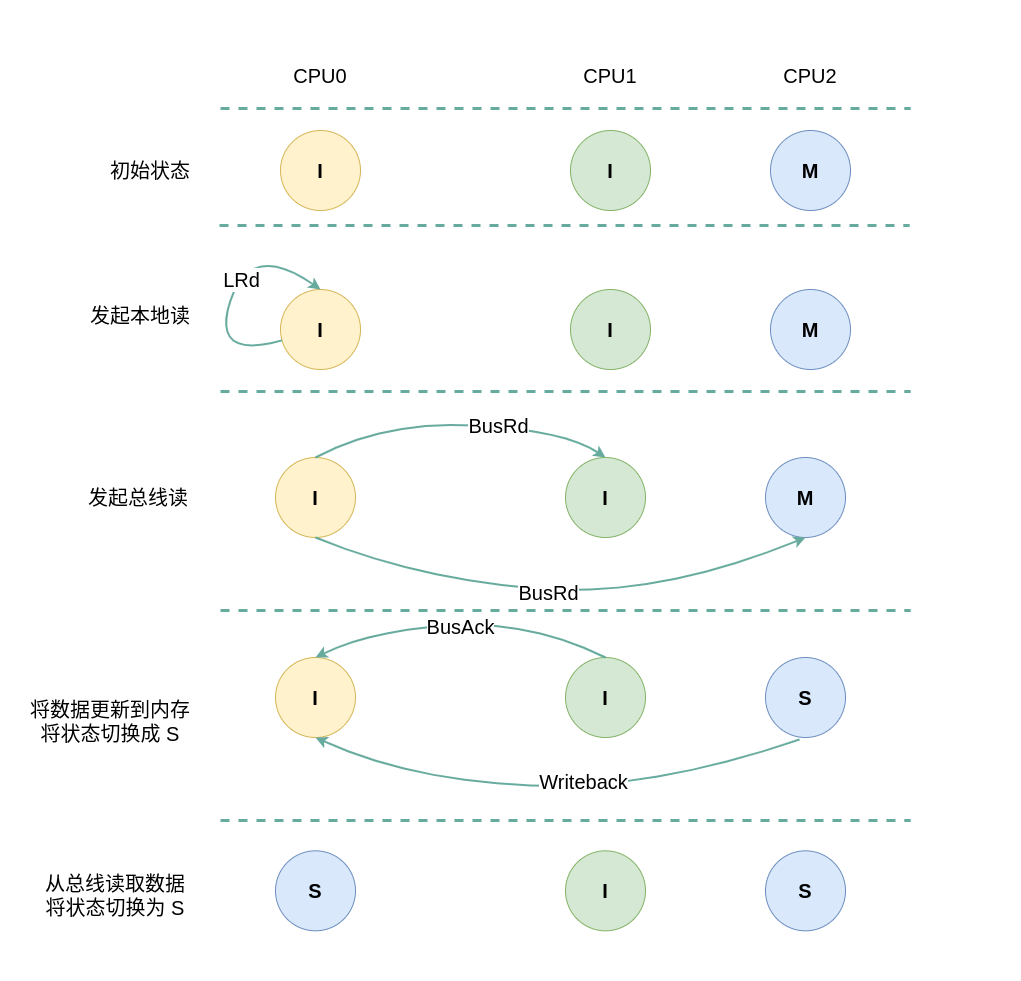

(4) 本地读远端 Modify: 当 CPU0 发起本地读请求 LRd 时,发现本地 CACHE Line 的状态为 Invalid,即 CACHE 中没有缓存对应的内容 CACHE Miss,那么在总线上产生一个 总线读 BusRd,CPU1 和 CPU2 监听到 BusRd 之后检查 CACHE 中是否包含副本,此时 CPU1 的 CACHE Line 都为 Invalid 没有包含副本,那么 CPU1 直接向总线发送应答信号; CPU2 检查到其缓存了副本,且该 CACHE Line 的状态为 Modify,那么 CPU2 向总线回复一个 Writeback 信号,并先将 CACHE Line 的内容更新到内存,然后发送到总线上, 并将 CACHE Line 的状态切换成 Shared. CPU0 收到 Writeback 信号之后从总线上读取了数据并缓存到本地的 CACHE Line,并将 CACHE Line 的状态标记为 Shared.

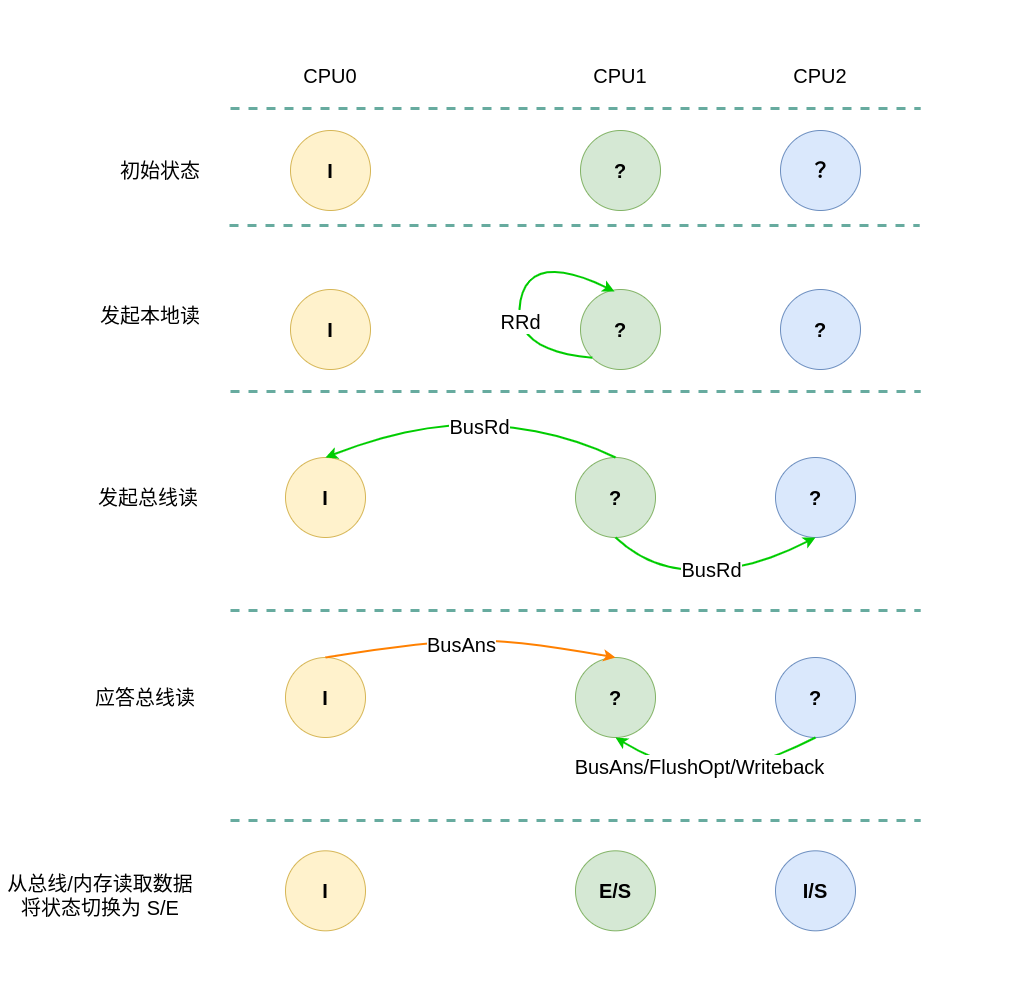

(5) 远端读本地 Invalid: 当 CPU1 发起远端读请求 RRd 时,无论远端 CACHE Line 的状态如何,也无论是否产生总线读请求 BusRd,CPU0 监听到 BusRd 信号之后,检查其 CACHE 中并没有副本,然后直接应答总线,然后继续保持 Invalid.

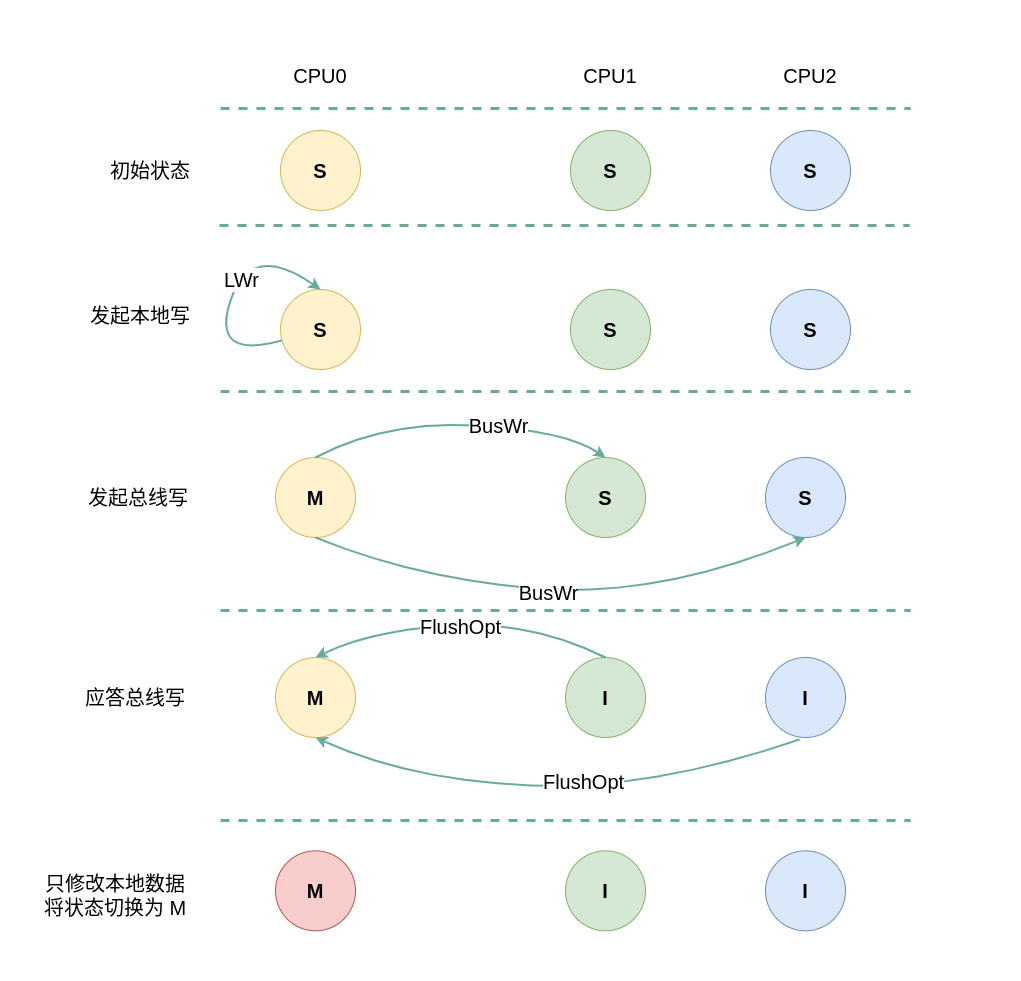

本地/远端写请求

假设系统有 3 个 CPU,分别是 CPU0、CPU1 和 CPU2,并且 CPU0 为本地视角,CPU1 和 CPU2 为远端视角, 当 CPU0 发起本地写请求 LRd 或者 CPU1/CPU2 发起远端写请求 RWr,当本地 CACHE Line 为 Invalid 状态,远端 CACHE Line 可能是 Invalid、Modify、Exclusive 和 Shared,那么 CACHE Line 的变化包含以下几种情况:

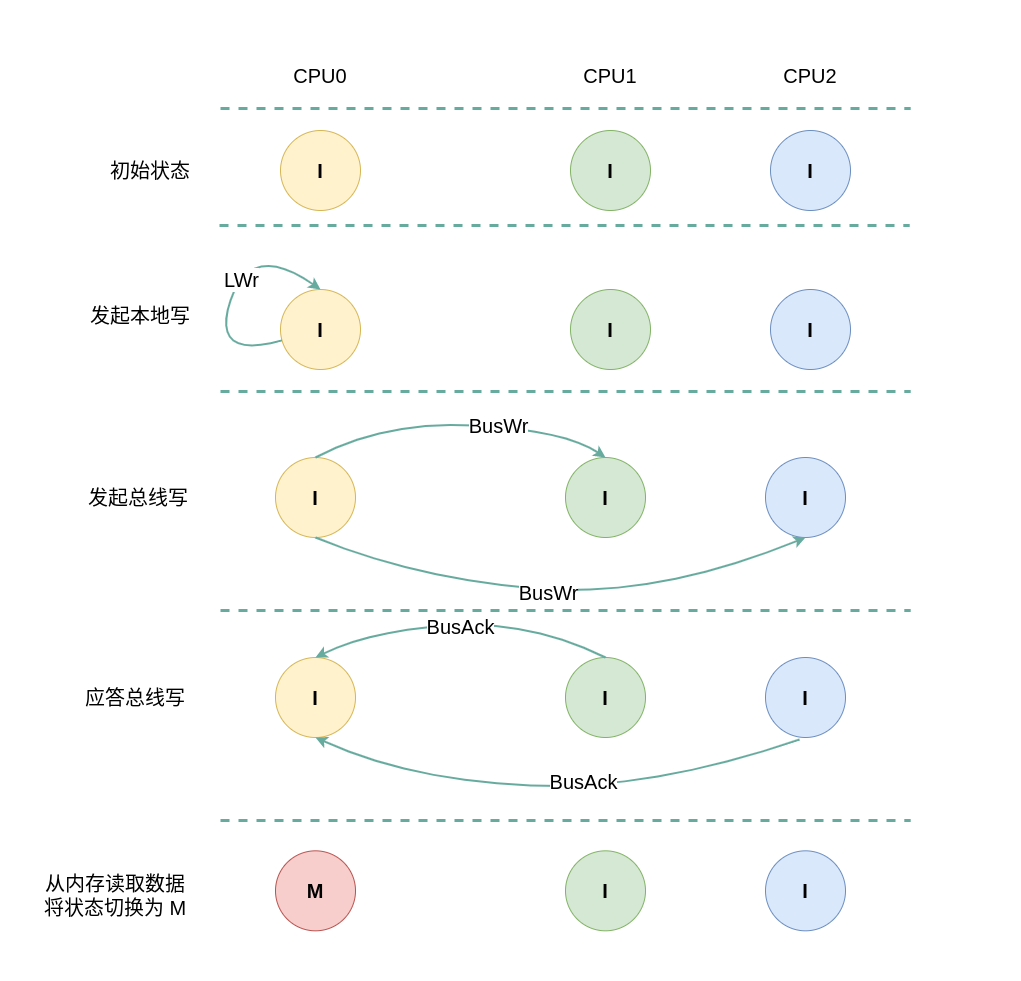

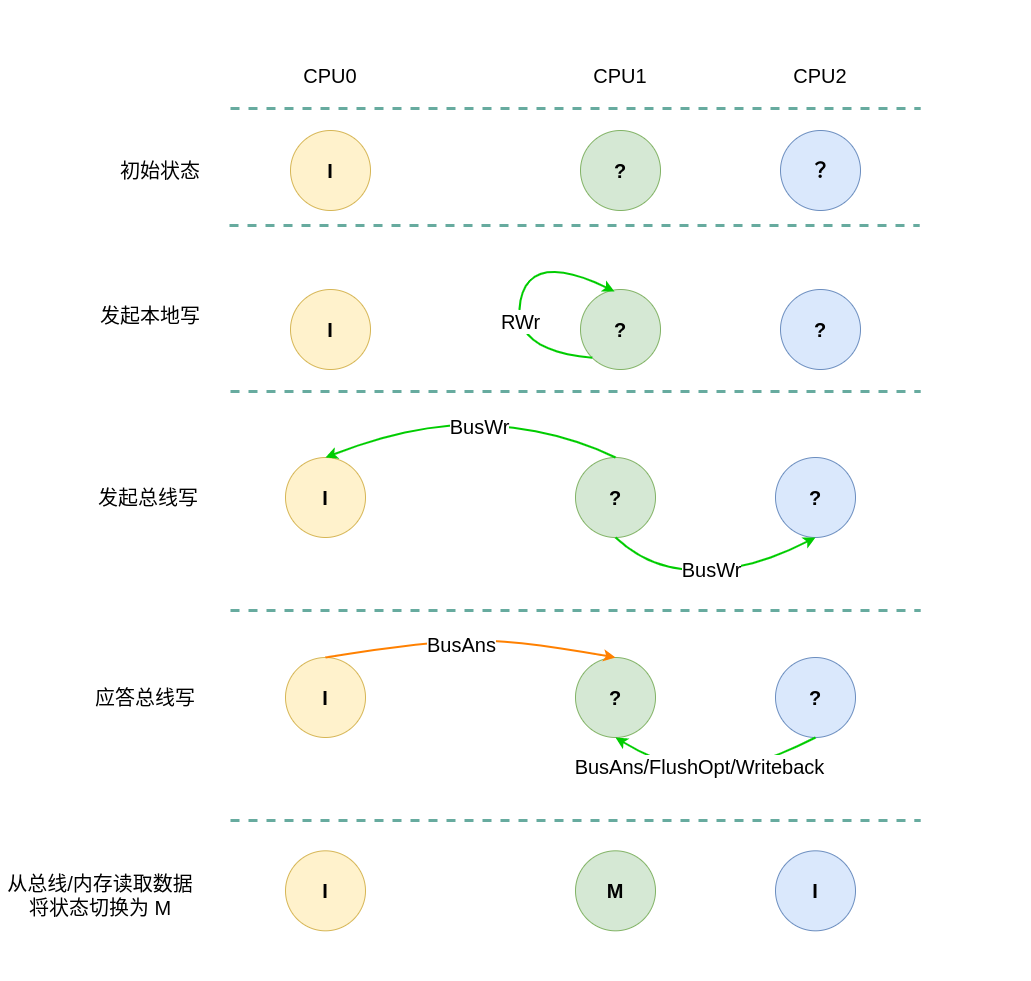

(1) 本地写全 Invalid: 当 CPU0 发起本地写请求 LWr 时,发现本地 CACHE Line 的状态为 Invalid,即 CACHE 中没有缓存对应的内容 CACHE Miss,那么在总线上产生一个 总线写 BusWr,CPU1 和 CPU2 监听到 BusWr 之后检查 CACHE 中是否包含副本,此时 CPU1 和 CPU2 的 CACHE Line 都为 Invalid,那么没有包含副本. 接着 CPU1 和 CPU2 向总线发送应答信号,并继续广播剩余的 CPU. CPU0 广播完所有的 CPU 之后发现总线上并没有数据,那么其从内存中读取数据到本地 CACHE Line,然后再修改 CACHE Line 中的数据,并将 CACHE Line 的状态切换到 Modify.

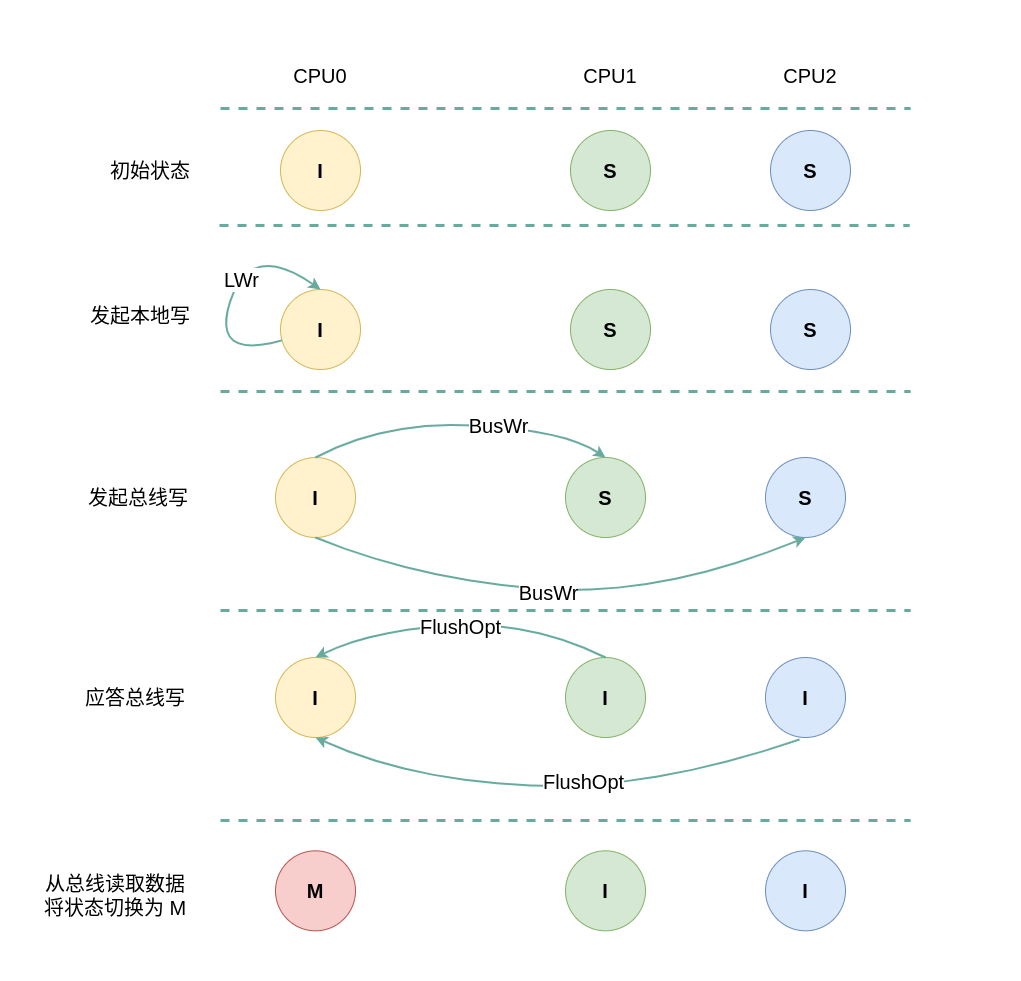

(2) 本地写远端 Shared: 当 CPU0 发起本地写请求 LWr 时,发现本地 CACHE Line 的状态为无效,即 CACHE 中没有缓存对应的内容 CACHE Miss,那么在总线上产生一个 总线写 BusWr,CPU1 和 CPU2 监听到 BusWr 之后检查 CACHE 中是否包含副本,此时 CPU1 和 CPU2 的 CACHE Line 都为 Shared,那么都有副本. 接着 CPU1 和 CPU2 向总线发送 FlushOpt 应答信号,并将副本的内容发送到总线,此时将 CACHE Line 状态都设置为 Invalid. CPU0 广播完所有的 CPU 之后发现总线上存在数据,那么其从总线上读取数据到本地 CACHE Line,然后修改 CACHE Line 中的数据,并将 CACHE Line 的状态切换到 Modify.

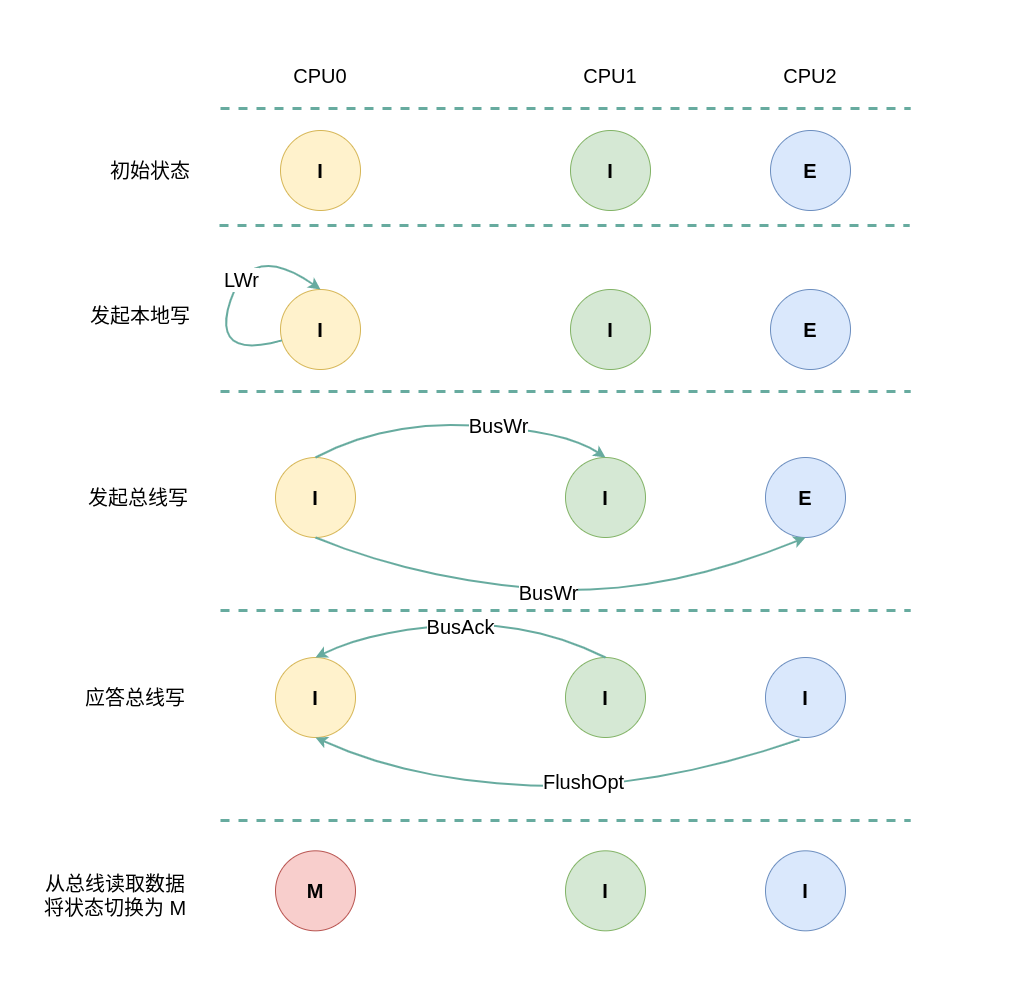

(3) 本地写远端 Exclusive: 当 CPU0 发起本地写请求 LWr 时,发现本地 CACHE Line 的状态为无效,即 CACHE 中没有缓存对应的内容 CACHE Miss,那么在总线上产生一个 总线写 BusWr,CPU1 和 CPU2 监听到 BusWr 之后检查 CACHE 中是否包含副本,此时 CPU1 没有包含对应的副本,那么直接应答总线. CPU2 中包含副本,且 CACHE Line 的状态为 Exclusive,接着 CPU2 向总线发送 FlushOpt 应答信号,并将副本的内容发送到总线,然后将 CACHE Line 状态都设置为 Invalid. CPU0 广播完所有的 CPU 之后发现总线上存在数据,那么其从总线上读取数据到本地 CACHE Line,然后修改 CACHE Line 中的数据,并将 CACHE Line 的状态切换到 Modify.

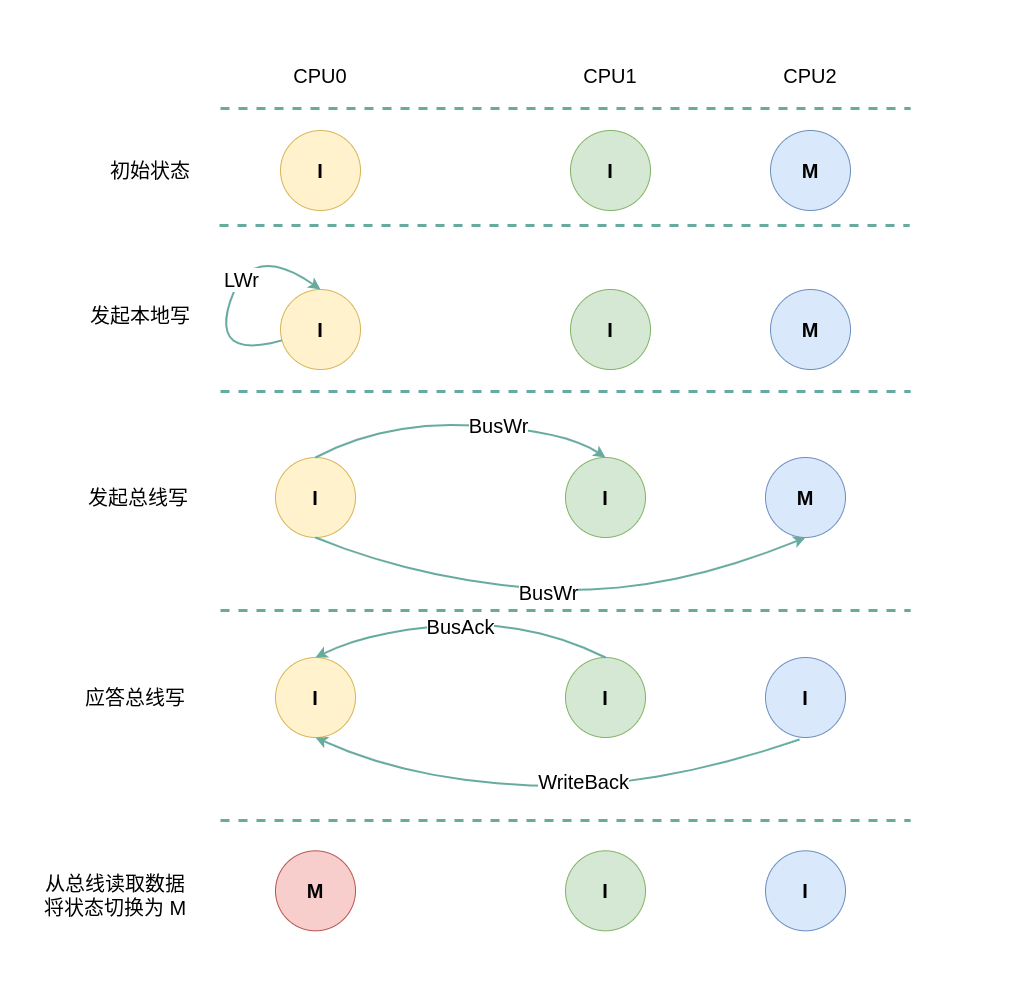

(4) 本地写远端 Modify: 当 CPU0 发起本地写请求 LWr 时,发现本地 CACHE Line 的状态为无效,即 CACHE 中没有缓存对应的内容 CACHE Miss,那么在总线上产生一个 总线写 BusWr,CPU1 和 CPU2 监听到 BusWr 之后检查 CACHE 中是否包含副本,此时 CPU1 没有包含对应的副本,那么直接应答总线. CPU2 中包含副本,且 CACHE Line 的状态为 Modify,接着 CPU2 向总线发送 WriteBack 信号,并将副本的内容写入内存,再将副本发送到总线,然后将 CACHE Line 状态都设置为 Invalid. CPU0 广播完所有的 CPU 之后发现总线上存在数据,那么其从总线上读取数据到本地 CACHE Line,然后修改 CACHE Line 中的数据,并将 CACHE Line 的状态切换到 Modify.

(5) 远端写本地 Invalid: 当 CPU1 发起远端写请求 RWr 时,无论远端 CACHE Line 的状态如何,也无论是否产生总线读请求 BusWr,CPU0 监听到 BusWr 信号之后,检查其 CACHE 中并没有副本,然后直接应答总线,然后继续保持 Invalid.

初始状态为 Modify

当本地 CACHE Line 的状态是 Modify,那么说明本地 CPU 修改了 CACHE Line 的值,但没有刷新到内存里,是一份脏数据, 并且其他 CPU 没有缓存副本。. 本地或远端发起的读写请求都会概念 CACHE Line 的状态,具体变化如下场景:

本地/远端读请求

假设系统有 3 个 CPU,分别是 CPU0、CPU1 和 CPU2,并且 CPU0 为本地视角,CPU1 和 CPU2 为远端视角,由于 CPU0 的 CACHE Line 状态为 Modify,那么其他 CPU 没有副本。读请求会引起 CACHE Line 状态在 Modify 和 Shared 之间转换, 具体如下:

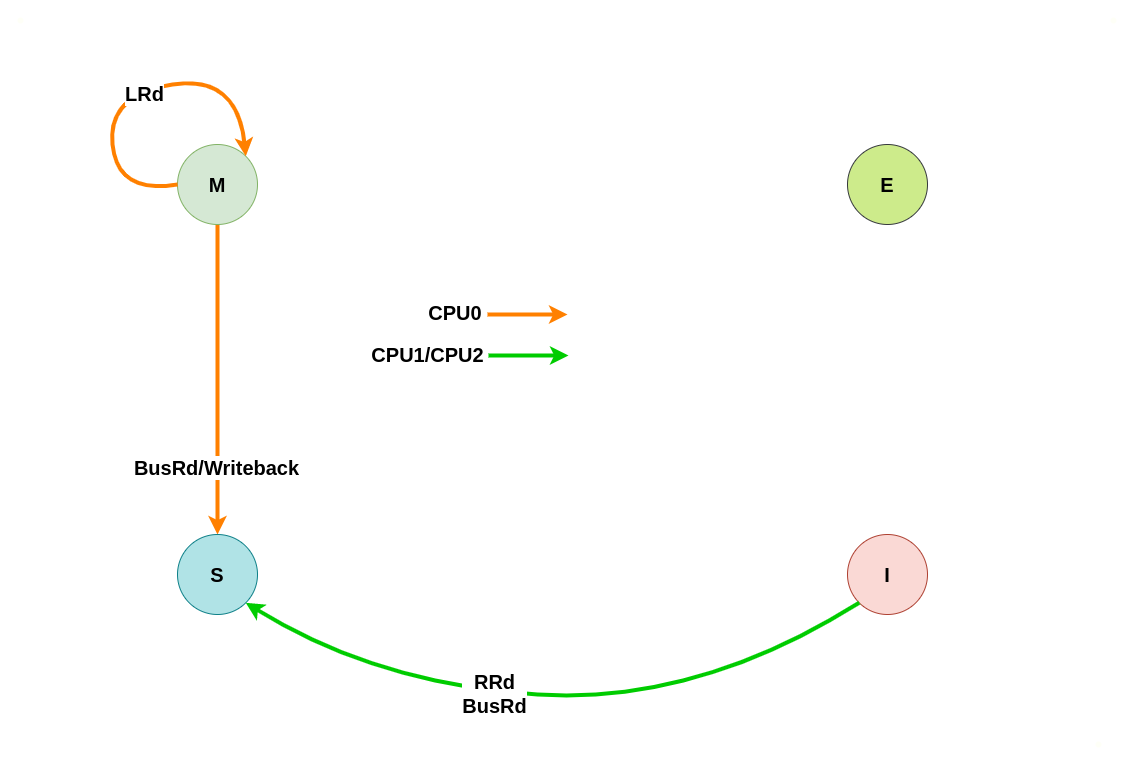

(1) 本地读请求: 当 CPU0 发起本地读请求 LRd 时,发现本地 CACHE Line 的状态为 Modify,即 CACHE 中缓存对应内容 CACHE Hit, 并且 CACHE Line 中的数据是最新的,与内存中的数据不一致,那么 CPU0 直接从本地 CACHE Line 中读取数据,并保持 CACHE Line 状态为 Modify.

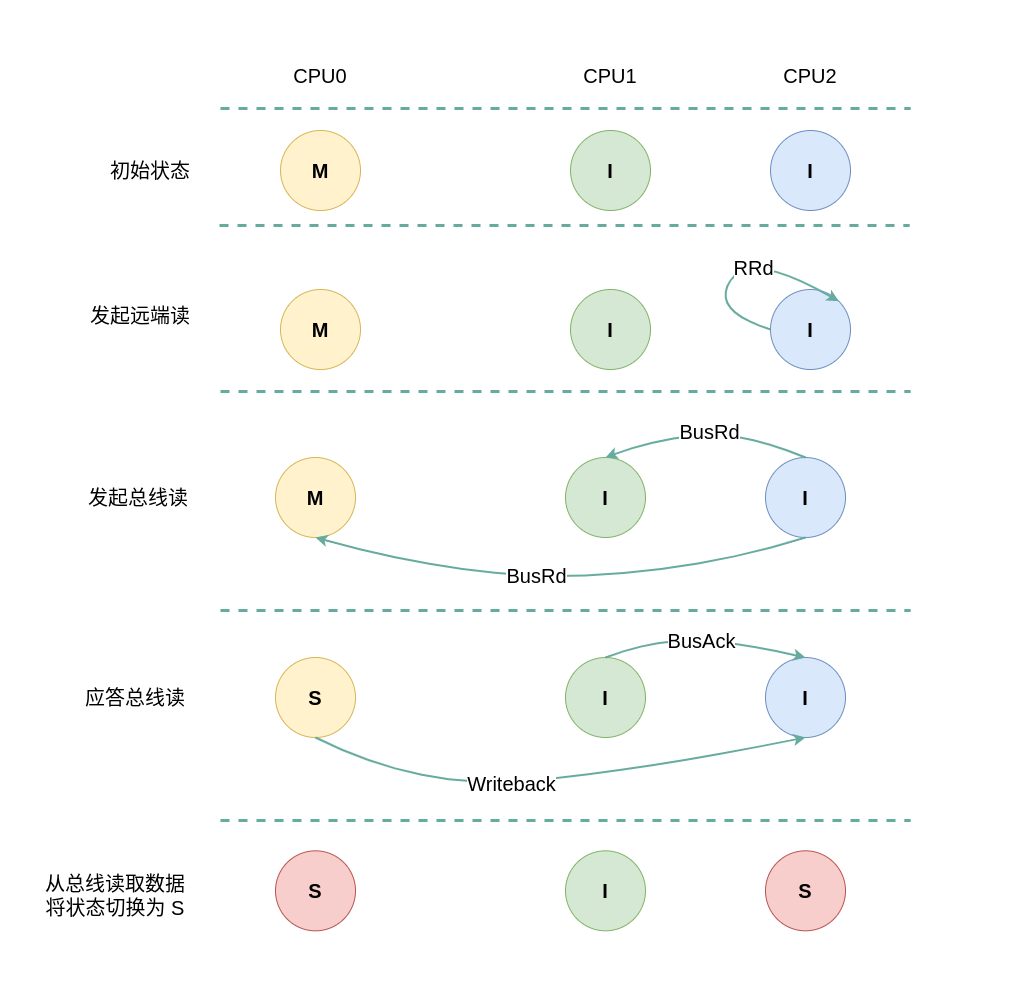

(2) 远端读本地 Modify: 当 CPU2 发起本地读请求 RRd 时,发现本地 CACHE Line 的状态为 Invalid,即 CACHE 中没有缓存对应内容 CACHE Miss, 那么在总线上产生一个总线读 BusRd, CPU1 监听到 BusRd 之后由于没有对应的副本,那么直接应答总线; CPU0 监听到 BusRd 之后发现具有对应的 CACHE Line 副本,且此时 CPU0 CACHE Line 的状态为 Modify,那么其向总线发送一个 Writeback 信号,同时将 CACHE Line 的数据发送到总线,并且将数据也写入到内存,最后将 CPU0 CACHE Line 状态设置为 Shared; CPU2 收到总线 Writeback 信号之后从总线上获得数据,并存储在 CPU2 的 CACHE Line,最后将 CACHE Line 状态设置为 Shared.

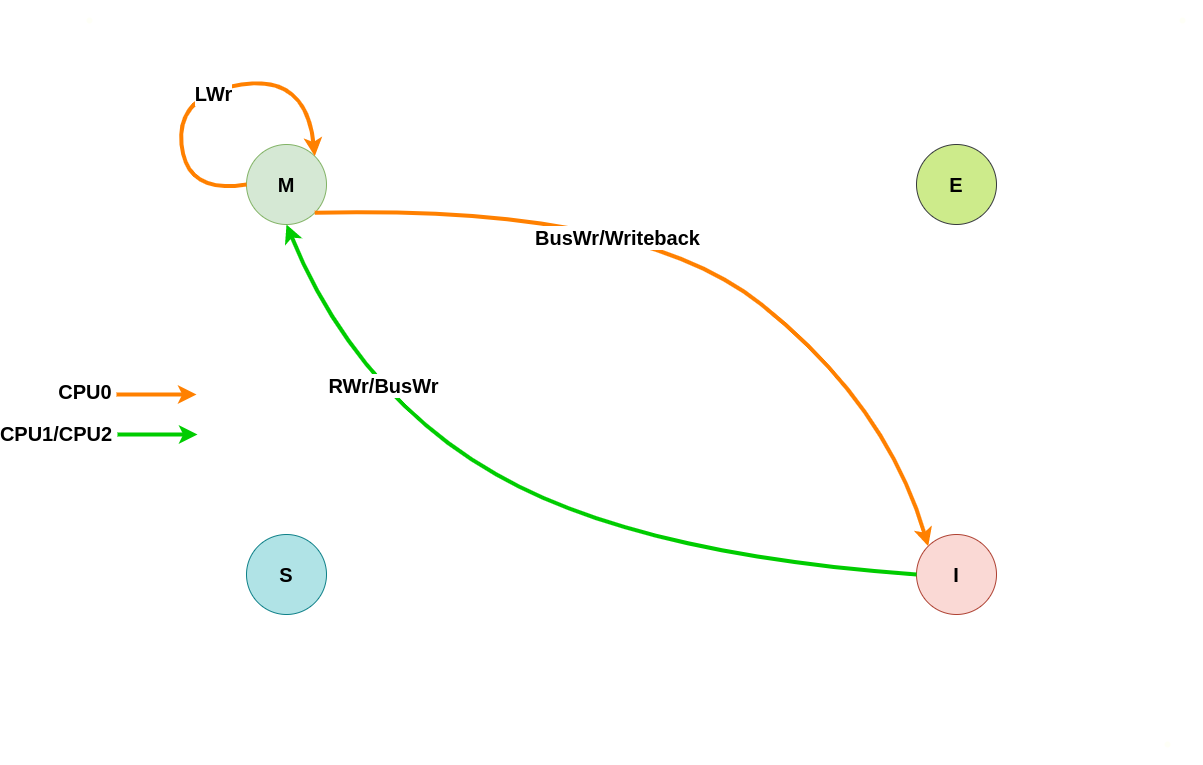

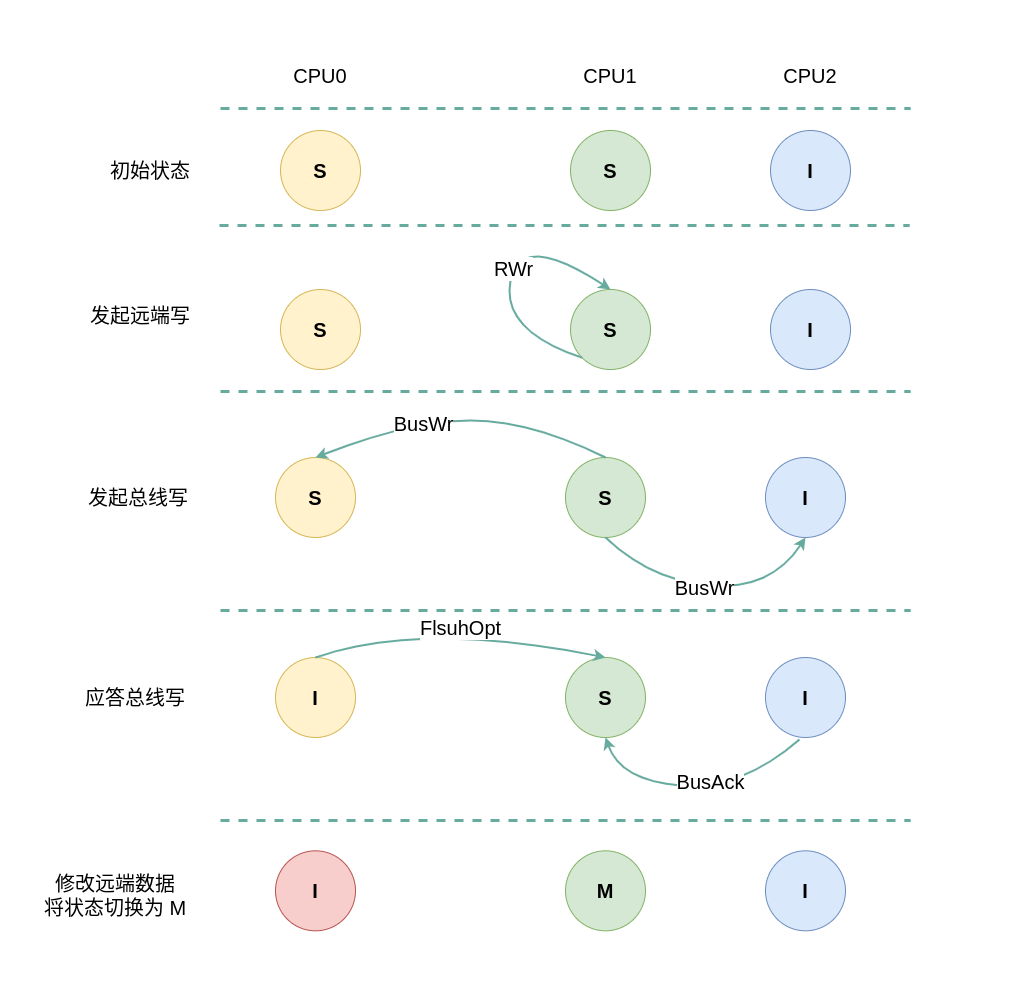

本地/总线写请求

假设系统有 3 个 CPU,分别是 CPU0、CPU1 和 CPU2,并且 CPU0 为本地视角,CPU1 和 CPU2 为远端视角,由于 CPU0 的 CACHE Line 状态为 Modify,那么其他 CPU 没有副本。写请求会引起 CACHE Line 状态在 Invalid 和 Modify 之间转换, 具体场景如下:

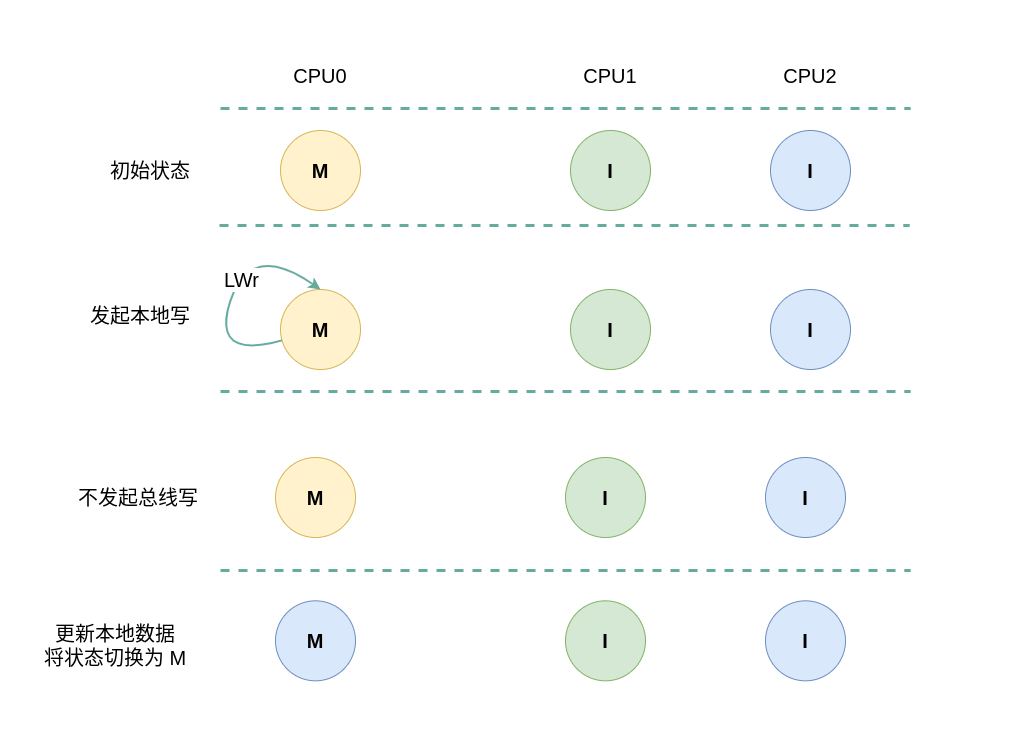

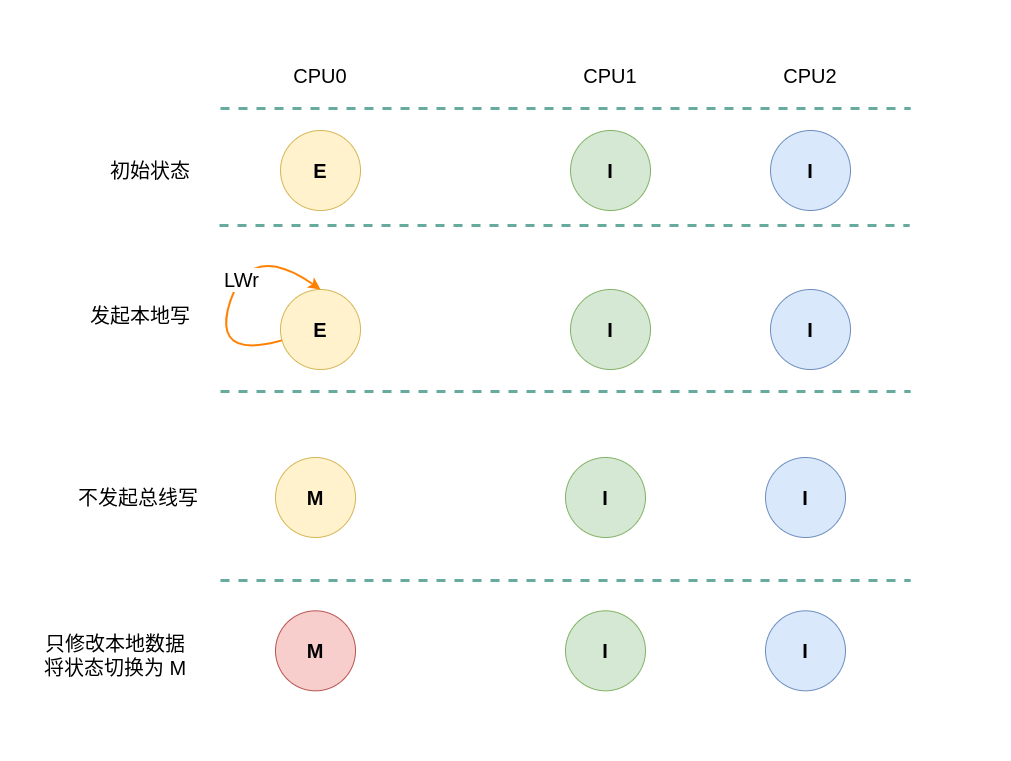

(1) 本地写请求: 当 CPU0 发起本地写请求 LWr 时,发现本地 CACHE Line 的状态为 Modify,即 CACHE 中缓存对应内容 CACHE Hit, 并且 CACHE Line 中的数据是最新的,与内存中的数据不一致,那么 CPU0 直接更新本地 CACHE Line 中数据,并保持 CACHE Line 状态为 Modify.

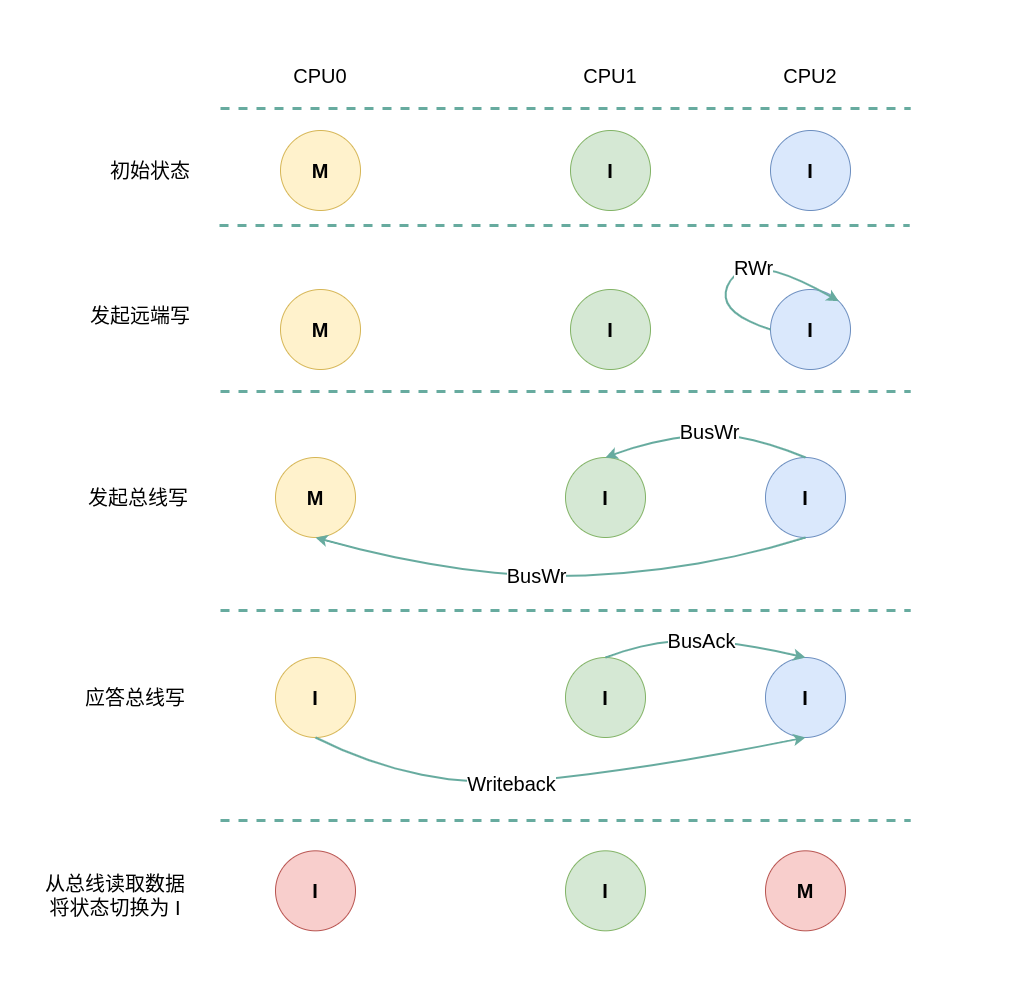

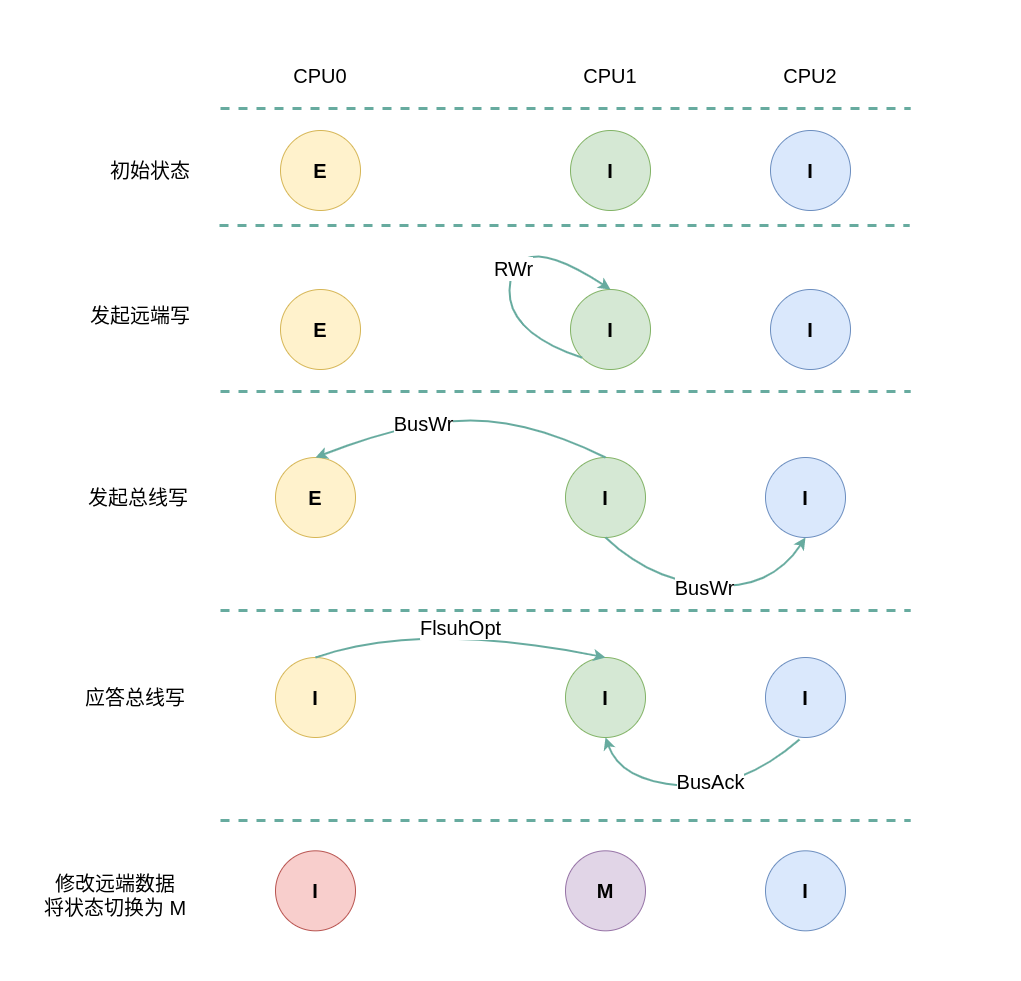

(2) 远端写本地 Modify: 当 CPU2 发起本地写请求 RRd 时,发现本地 CACHE Line 的状态为 Invalid,即 CACHE 中没有缓存对应内容 CACHE Miss, 那么在总线上产生一个总线写 BusWr, CPU1 监听到 BusWr 之后由于没有对应的副本,那么直接应答总线; CPU0 监听到 BusWr 之后发现具有对应的 CACHE Line 副本,且此时 CPU0 CACHE Line 的状态为 Modify,那么其向总线发送一个 Writeback 信号,同时将 CACHE Line 的数据发送到总线,并且将数据也写入到内存,最后将 CPU0 CACHE Line 状态设置为 Invalid; CPU2 收到总线 Writeback 信号之后从总线上获得数据,并存储在 CPU2 的 CACHE Line,接着更新 CACHE Line 中的内容,最后将 CACHE Line 状态设置为 Modify.

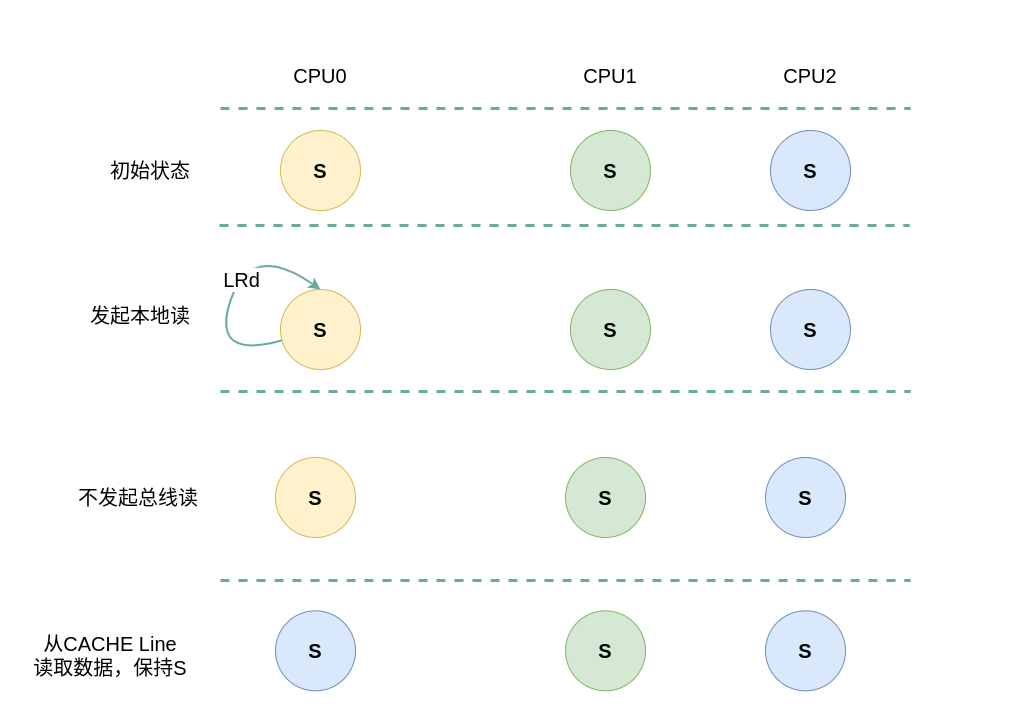

初始状态为 Shared

当本地 CACHE Line 的初始状态为 Shared,那么说明其他 CPU 也缓存了该副本,且 CACHE Line 的状态可能是 Invalid 或者 Shared. 此时无论是本地读写还是远端读写,都会改变 CACHE Line 的状态,具体改变可以从读请求和写请求场景进行分析:

本地/远端读请求

假设系统有 3 个 CPU,分别是 CPU0、CPU1 和 CPU2,并且 CPU0 为本地视角,CPU1 和 CPU2 远端视角. 当 CPU0 发起本地读请求 LRd或者 CPU1/CPU2 发起远端读请求 RRd,当本地 CACHE Line 的状态为 Shared 状态,远端 CACHE Line 的状态可能是 Shared 或 Invalid,那么 CACHE Line 的变化包括如下几种场景:

(1) 本地读请求: 当 CPU0 发起本地读请求 LRd 时,发现本地 CACHE Line 的状态为 Shared,即 CACHE 中有缓存对应内容 CACHE Hit, 其他 CPU 也有相应的副本,且所有的副本与内存上的数据是一致的,因此本地 CACHE Line 的状态保持 Shared,不会向总线发起 BusRd 信号,而是直接从 CACHE Line 中读取数据.

(2) 远端写请求: 当 CPU1 发起远端读请求 RRd 时,发现其 CACHE Line 的状态为 Invalid,即 CACHE 中有没有缓存对应内容 CACHE Miss, 那么在总线上产生一个总线读请求 BusRd,CPU0 监听到 BusRd 信号之后,发现其具有副本且 CACHE Line 状态为 Shared,那么直接应答一个 FlushOpt 信号,并将 CACHE Line 的内存发送到总线上,其他 CACHE Line 为 Shared 的也会做同样操作; CPU1 收到 FlushOpt 信号之后,从总线上读取数据到自己的 CACHE Line,并将 CACHE Line 信号更改为 Shared.

本地/远端写请求

假设系统有 3 个 CPU,分别是 CPU0、CPU1 和 CPU2,并且 CPU0 为本地视角,CPU1 和 CPU2 远端视角. 当 CPU0 发起本地写请求 LWr或者 CPU1/CPU2 发起远端写请求 RWr,当本地 CACHE Line 的状态为 Shared 状态,远端 CACHE Line 的状态可能是 Shared 或 Invalid,那么 CACHE Line 的变化包括如下几种场景:

(1) 本地写请求: 当 CPU0 发起本地写请求 LWr 时,发现本地 CACHE Line 的状态为 Shared,即 CACHE 中有缓存对应内容 CACHE Hit, 其他 CPU 也有相应的副本,且所有的副本与内存上的数据是一致的,CPU0 向总线产生一个总线写 BusWr, 其他 CPU 监听到 BusWr 之后检查是否包含对应的副本,如果有则将对应的 CACHE Line 状态设置为 Invalid,并回应一个 FlushOpt 信号. CPU0 收到 FlushOpt 应答之后直接修改本地 CACHE Line 的内容,并将 CACHE Line 的状态修改为 Modify.

(2) 远端写请求: 当 CPU1 发起远端写请求 RWr 时,发现其 CACHE Line 的状态为 Shared,即 CACHE 中有缓存对应内容 CACHE Hit, 其他 CPU 也有相应的副本,且所有的副本与内存上的数据是一致的,CPU1 向总线产生一个总线写 BusWr, CPU0 监听到 BusWr 之后检查包含对应的副本,CPU0 则将对应的 CACHE Line 状态设置为 Invalid,并回应一个 FlushOpt 信号. CPU2 监听到 BusWr 之后检查不包含对应的副本,直接应答总线. CPU1 收到 FlushOpt 应答之后直接修改其 CACHE Line 的内容,并将 CACHE Line 的状态修改为 Modify.

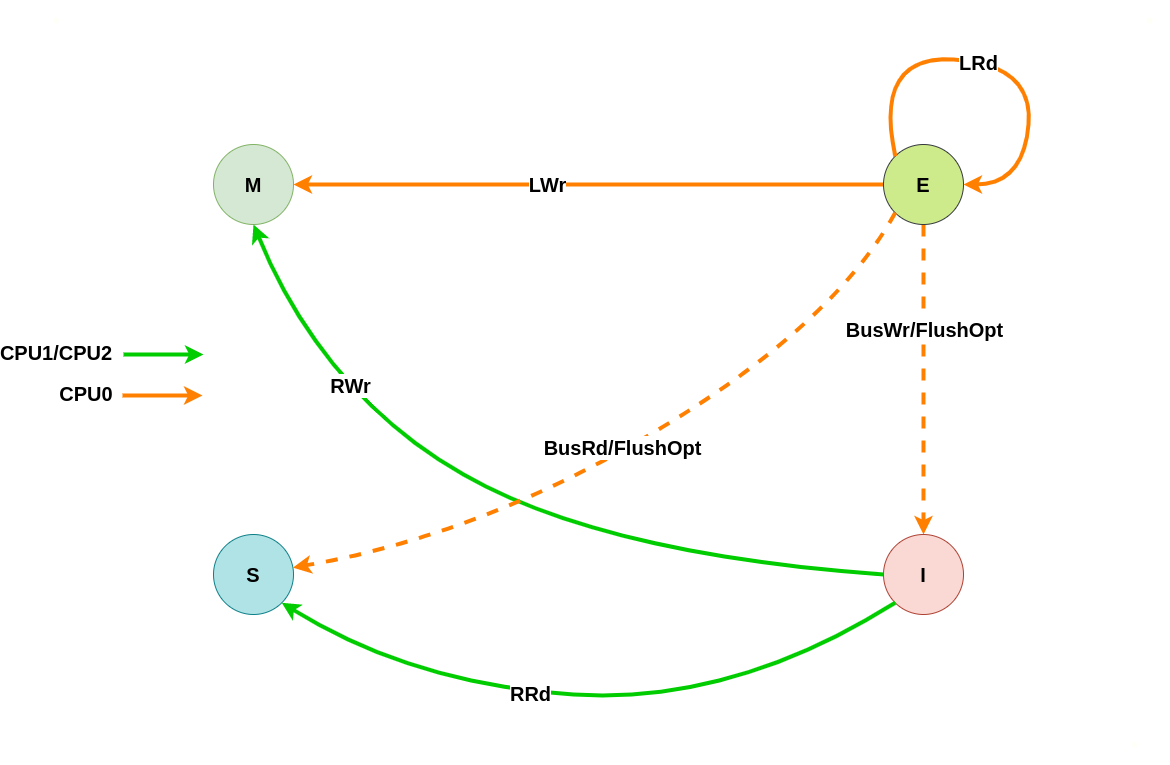

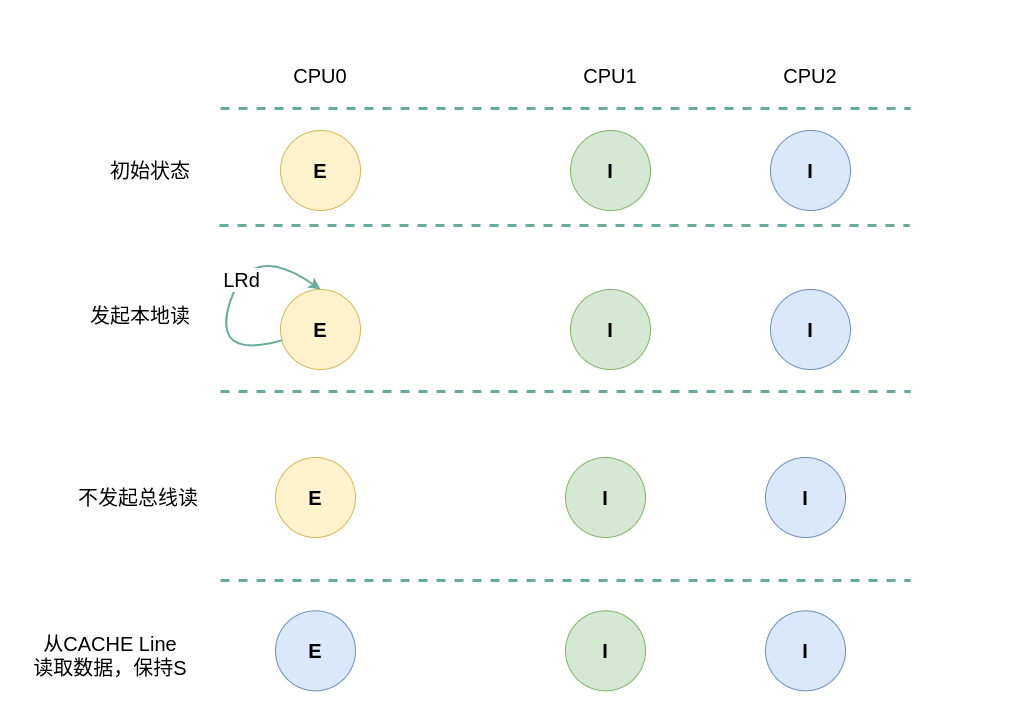

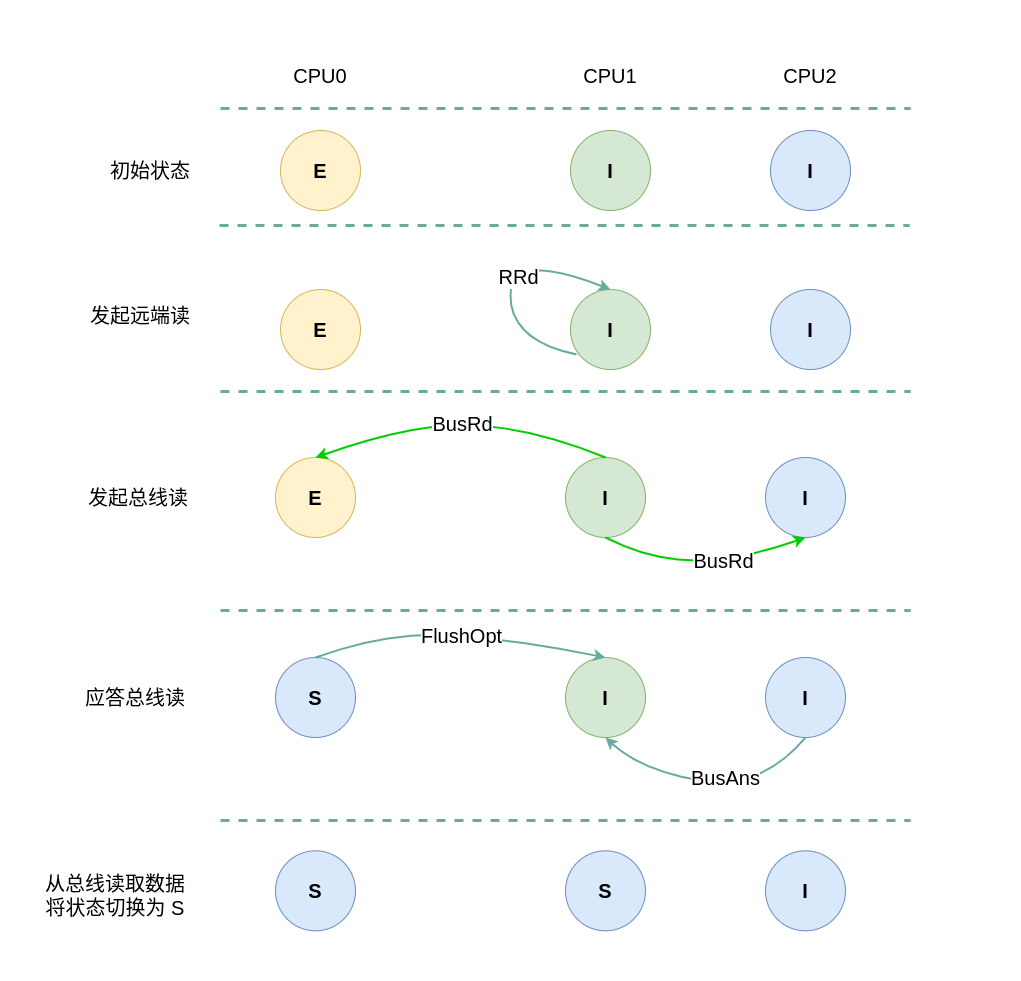

初始状态为 Exclusive

当本地 CACHE Line 的状态为 Exclusive,那么说明其他 CPU 并没有该 CACHE Line 的副本,并且本地 CACHE Line 的内容和内存中的内存是一致的. 此时无论是本地读写还是远端读写,都会改变 CACHE Line 的状态,具体改变可以从读请求和写请求场景进行分析:

本地/远端读请求

假设系统有 3 个 CPU,分别是 CPU0、CPU1 和 CPU2,并且 CPU0 为本地视角,CPU1 和 CPU2 远端视角. 当 CPU0 发起本地读请求 LRd或者 CPU1/CPU2 发起远端读请求 RRd,当本地 CACHE Line 的状态为 Exclusive 状态,远端 CACHE Line 的状态是 Invalid,那么 CACHE Line 的变化包括如下几种场景:

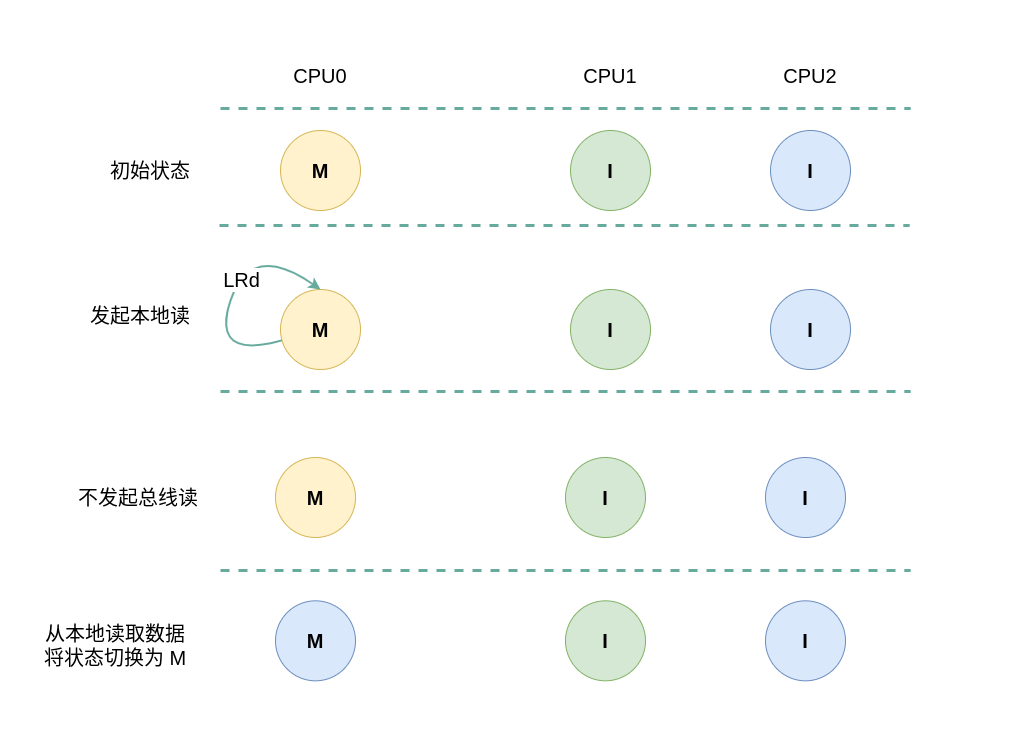

(1) 本地读请求: 当 CPU0 发起本地读请求 LRd 时,发现本地 CACHE Line 的状态为 Exclusive,即 CACHE 中有缓存对应内容 CACHE Hit, 其他 CPU 没有有相应的副本,且 CACHE Line 与内存上的数据是一致的,因此本地 CACHE Line 的状态保持 Exclusive,不会向总线发起 BusRd 信号,而是直接从 CACHE Line 中读取数据.

(2) 远端读请求: 当 CPU1 发起本地读请求 LRd 时,发现本地 CACHE Line 的状态为 Invalid,即 CACHE 中没有缓存对应内容 CACHE Miss, 那么产生一个总线读请求 BusRd. CPU0 监听到 BusRd 信号之后,检查其 CACHE 中存在副本,那么向总线发送 FlushOpt 信号并将 CACHE Line 内容发送到总线上,然后将其 CACHE Line 的状态切换成 Shared; CPU2 收到 BusRd 信号之后,检查其没有对应的副本,那么直接应答总线; CPU1 收到 FlushOpt 信号之后从总线上读取内容到本地的 CACHE Line,然后将 CACHE Line 状态设置为 Shared.

本地/远端写请求

假设系统有 3 个 CPU,分别是 CPU0、CPU1 和 CPU2,并且 CPU0 为本地视角,CPU1 和 CPU2 远端视角. 当 CPU0 发起本地写请求 LWr或者 CPU1/CPU2 发起远端写请求 RWr,当本地 CACHE Line 的状态为 Exclusive 状态,远端 CACHE Line 的状态是 Invalid,那么 CACHE Line 的变化包括如下几种场景:

(1) 本地写请求: 当 CPU0 发起本地写请求 LRd 时,发现本地 CACHE Line 的状态为 Exclusive,即 CACHE 中有缓存对应内容 CACHE Hit, 其他 CPU 没有有相应的副本,且 CACHE Line 与内存上的数据是一致的,因此直接修改 CACHE Line 的内容,并将 CACHE Line 的状态切换为 Modify.

(2) 远端写请求: 当 CPU1 发起本地写请求 LRd 时,发现本地 CACHE Line 的状态为 Invalid,即 CACHE 中没有缓存对应内容 CACHE Miss, 那么产生一个总线写请求 BusWr. CPU0 监听到 BusWr 信号之后,检查其 CACHE 中存在副本,那么向总线发送 FlushOpt 信号并将 CACHE Line 内容发送到总线上,然后将其 CACHE Line 的状态切换成 Invalid; CPU2 收到 BusWr 信号之后,检查其没有对应的副本,那么直接应答总线; CPU1 收到 FlushOpt 信号之后从总线上读取内容到本地的 CACHE Line,然后修改 CACHE Line 内容,并将 CACHE Line 状态设置为 Modify.

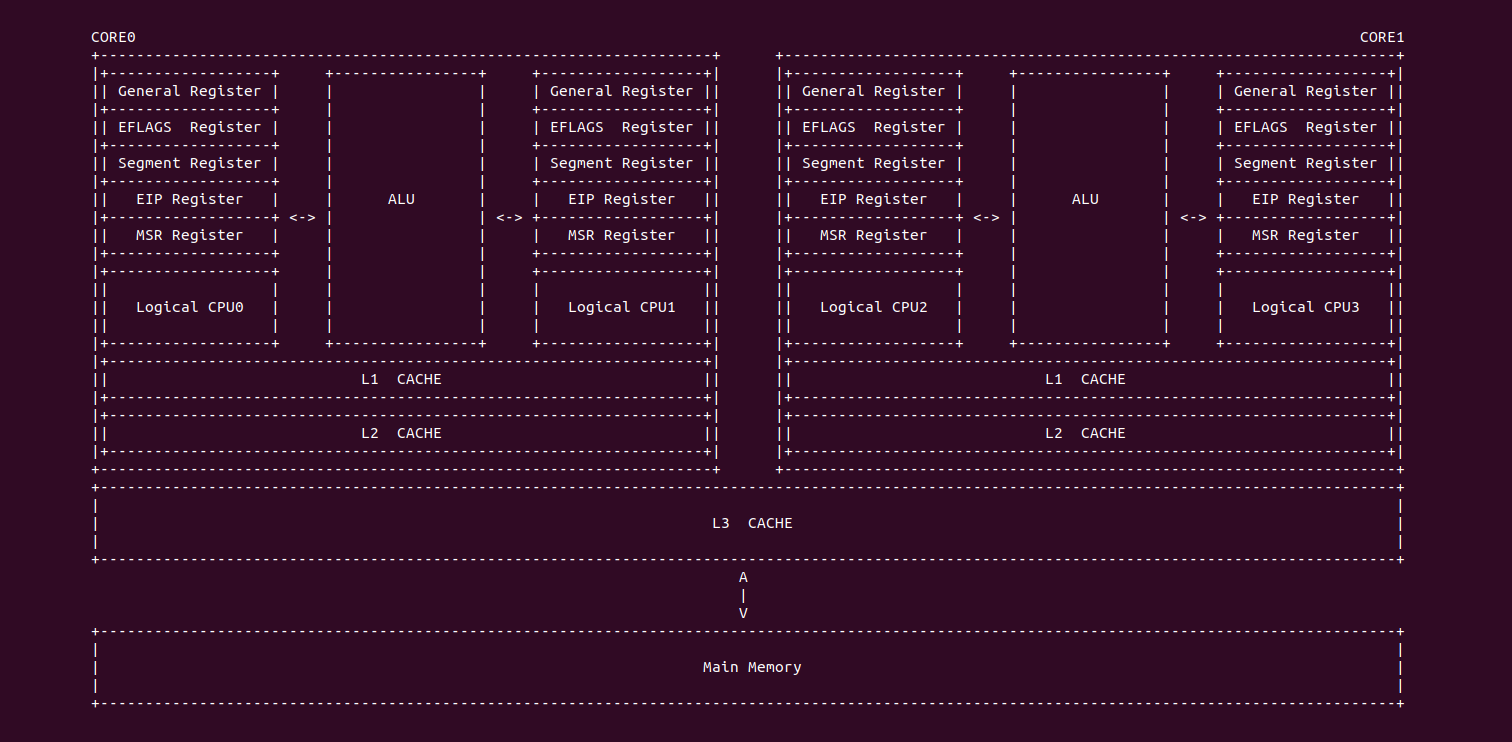

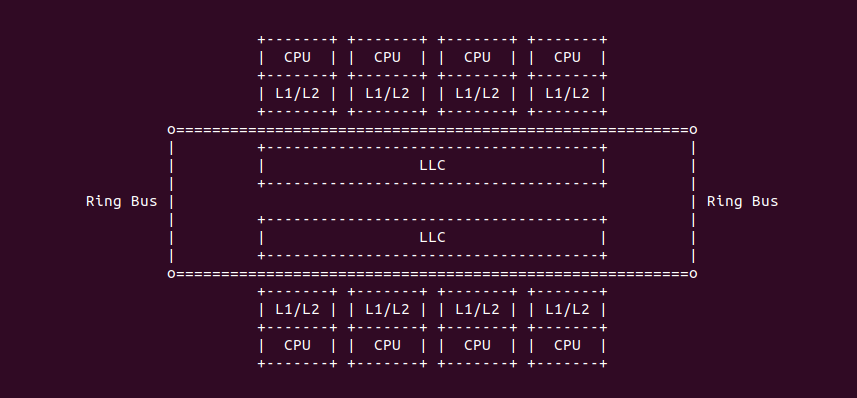

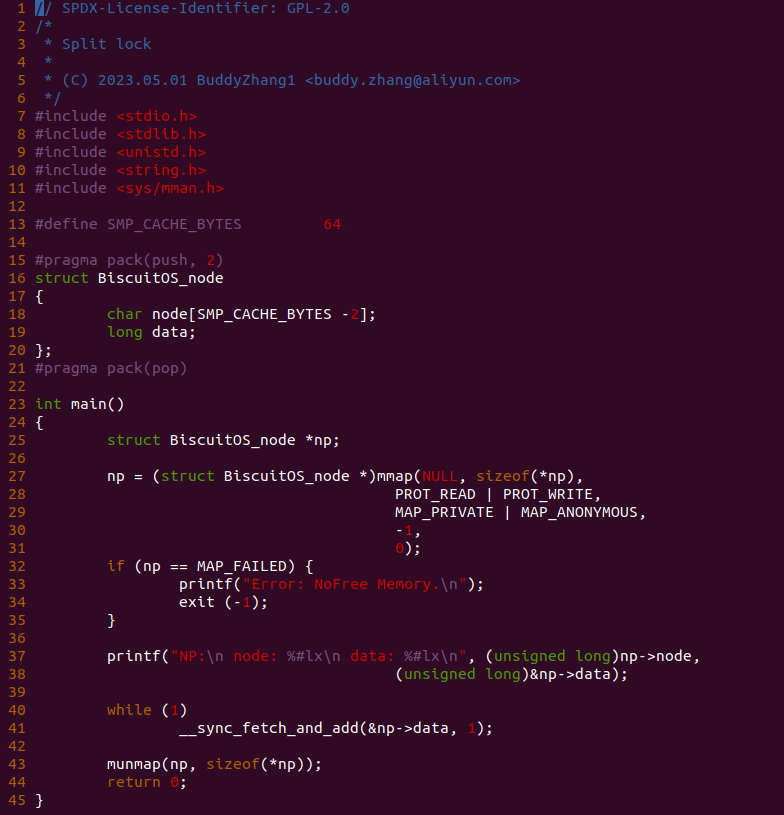

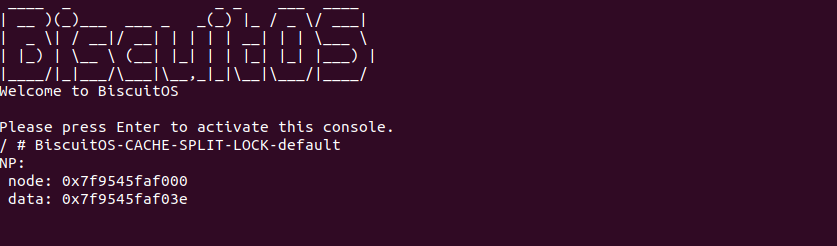

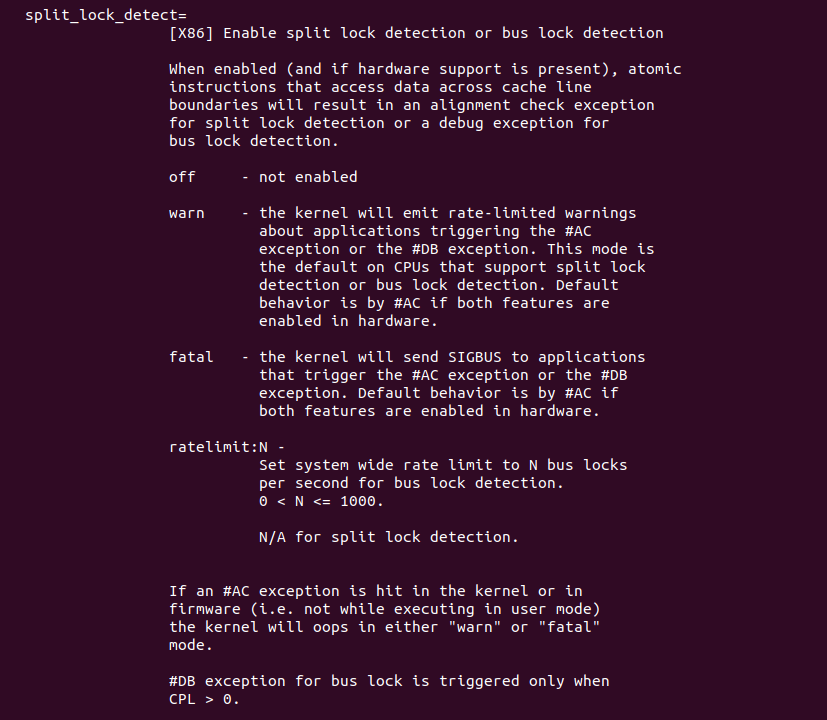

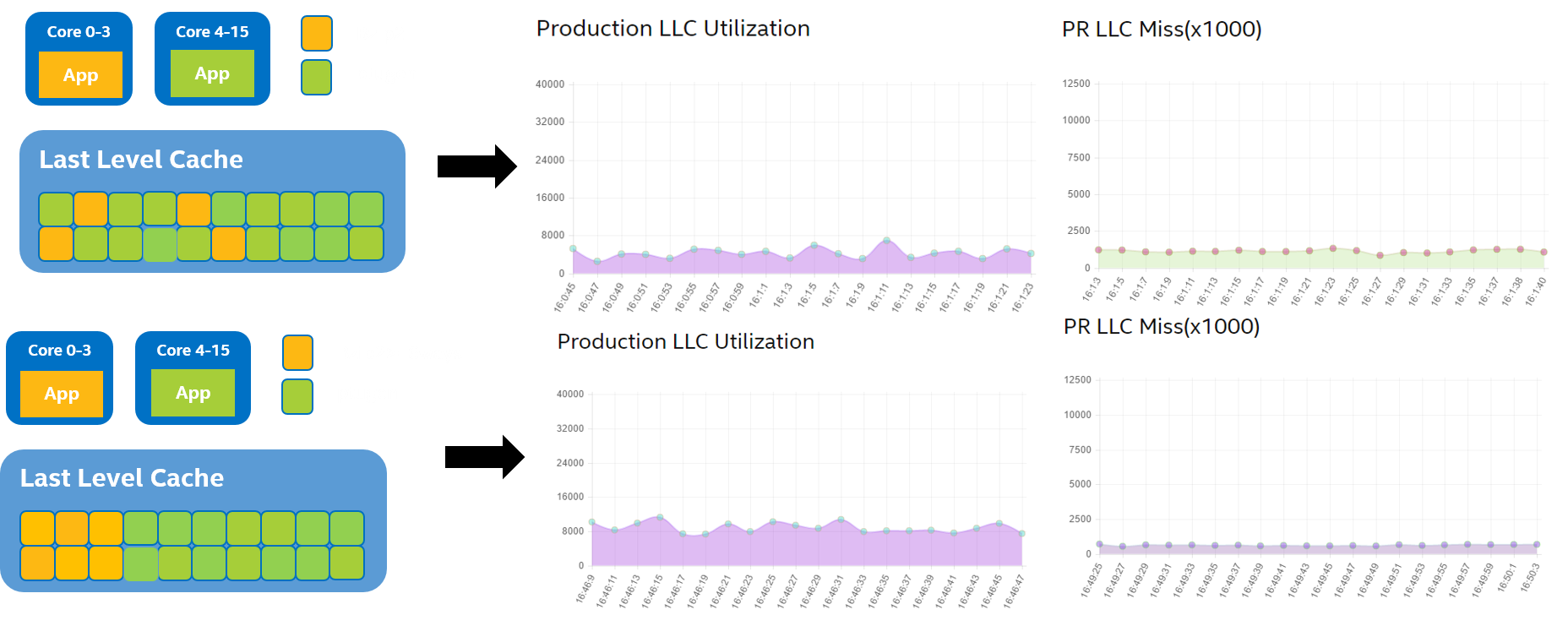

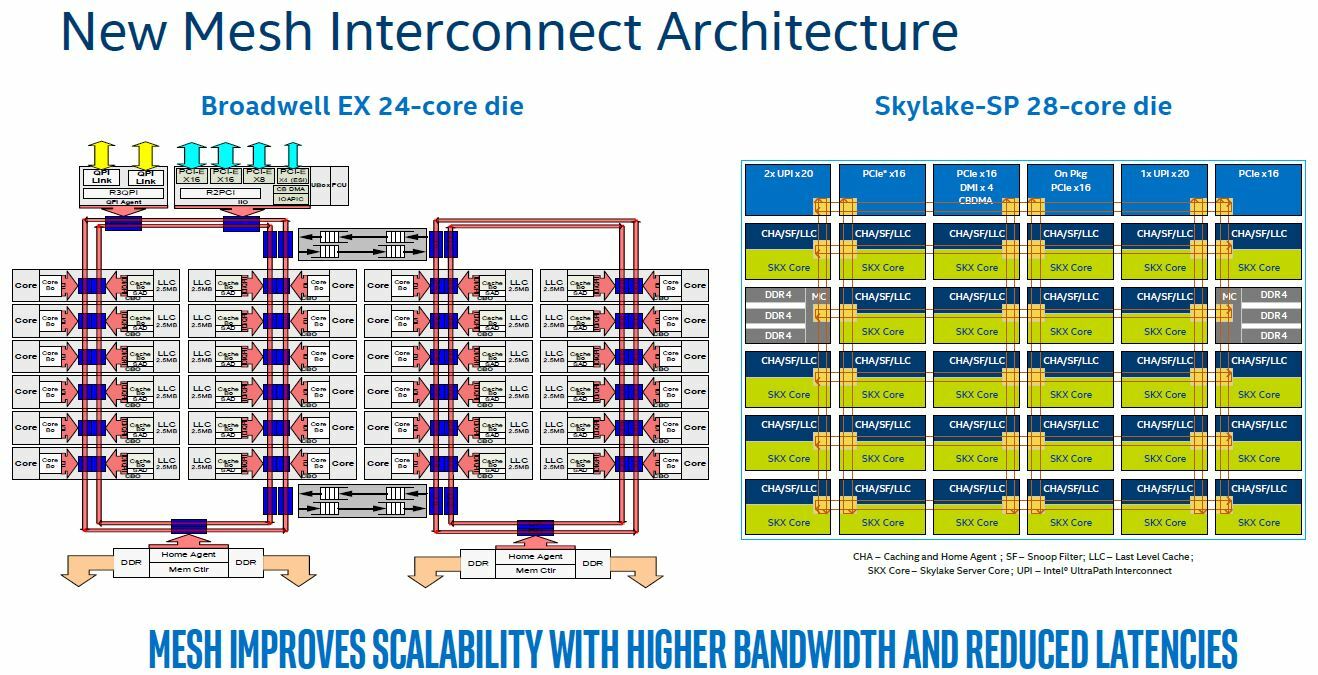

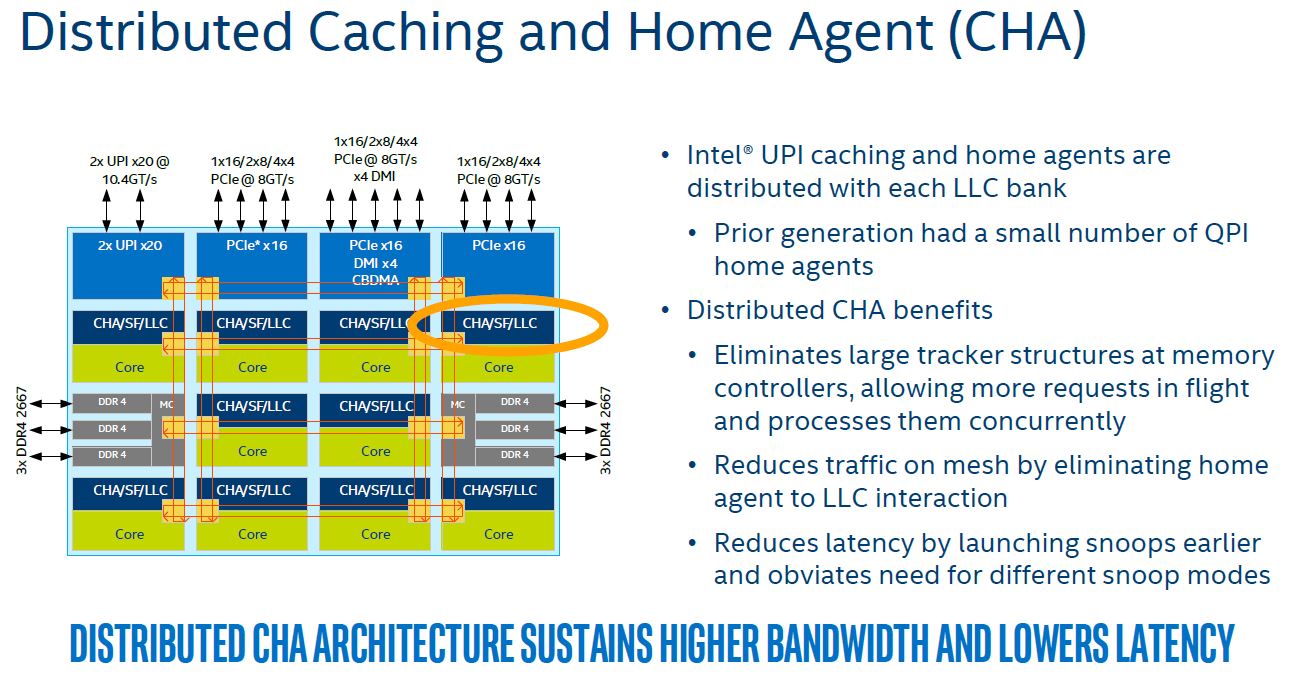

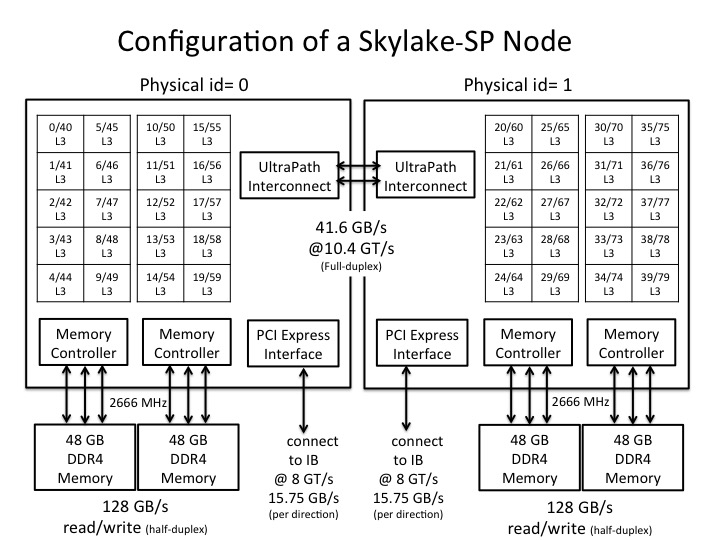

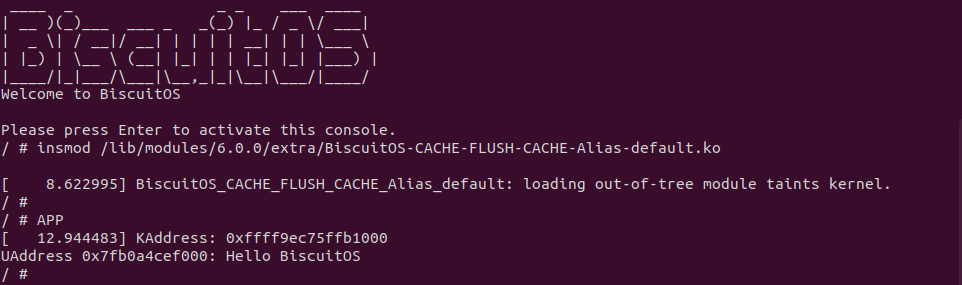

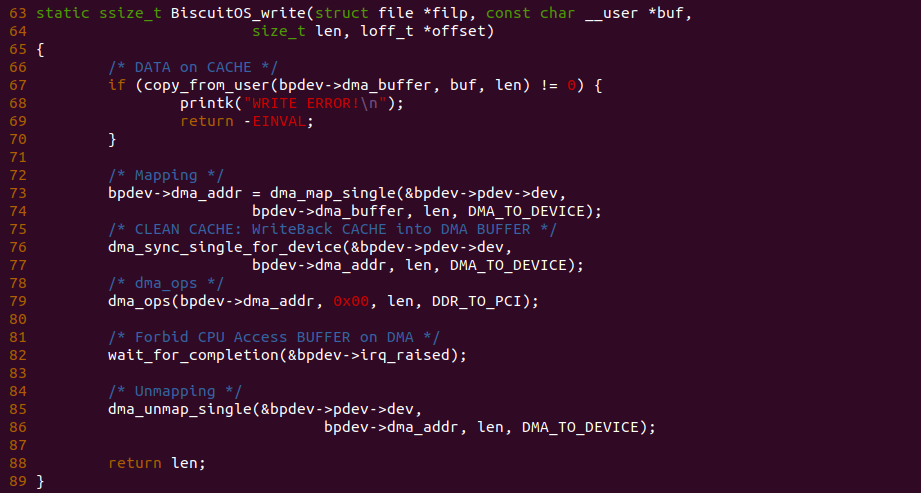

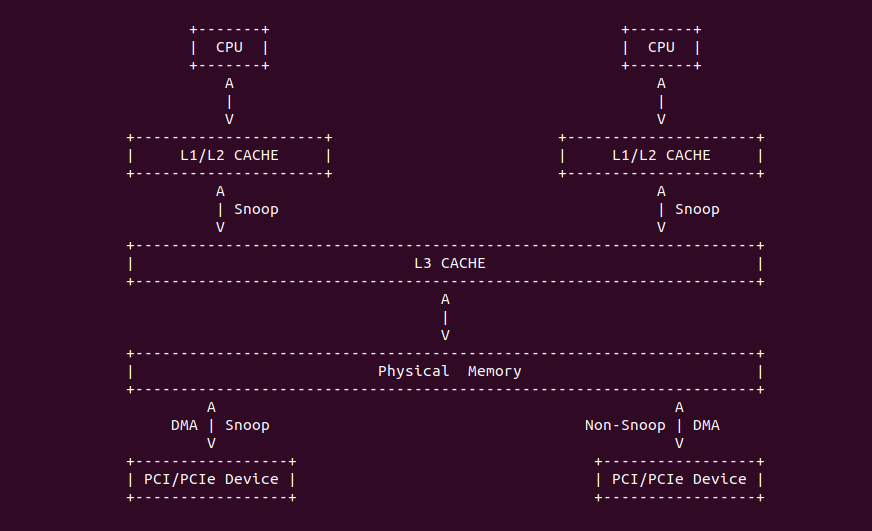

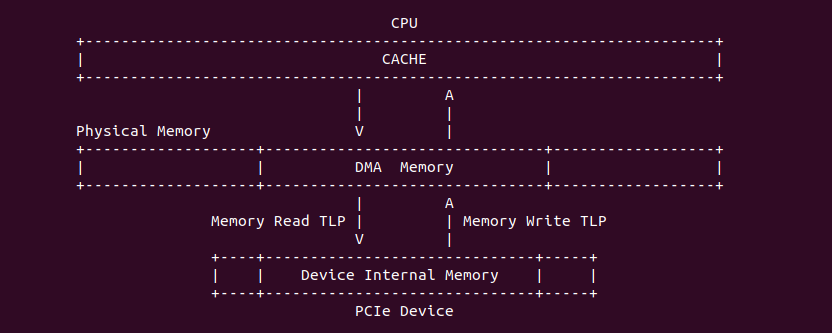

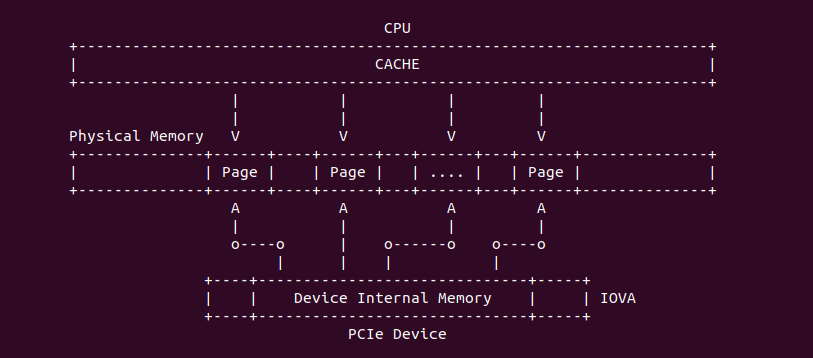

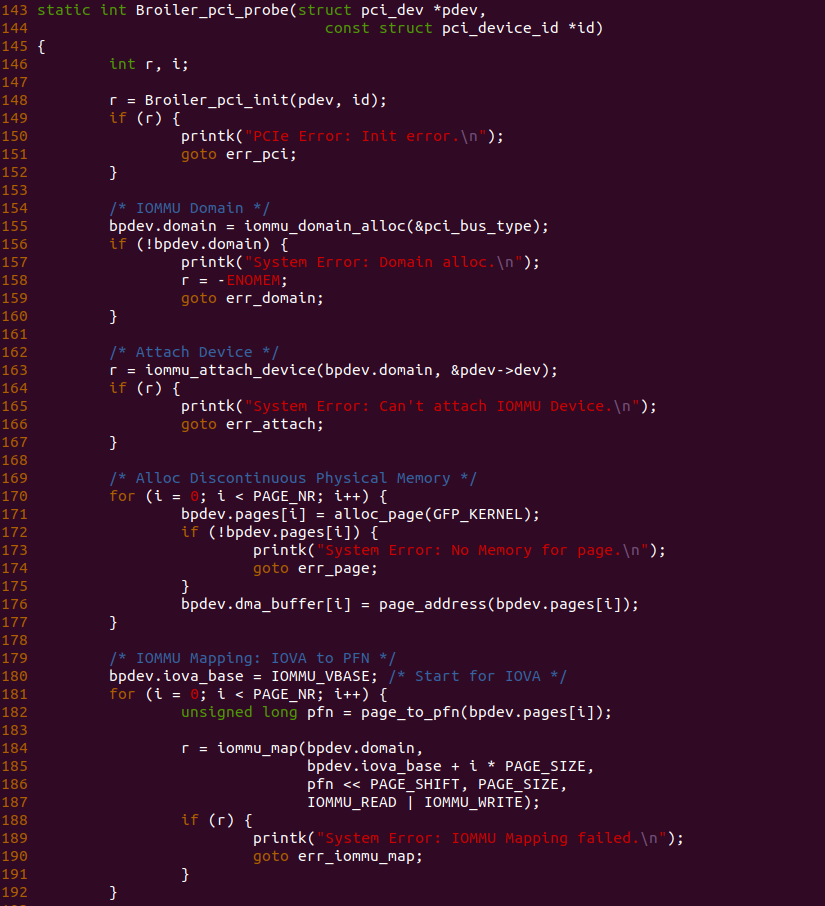

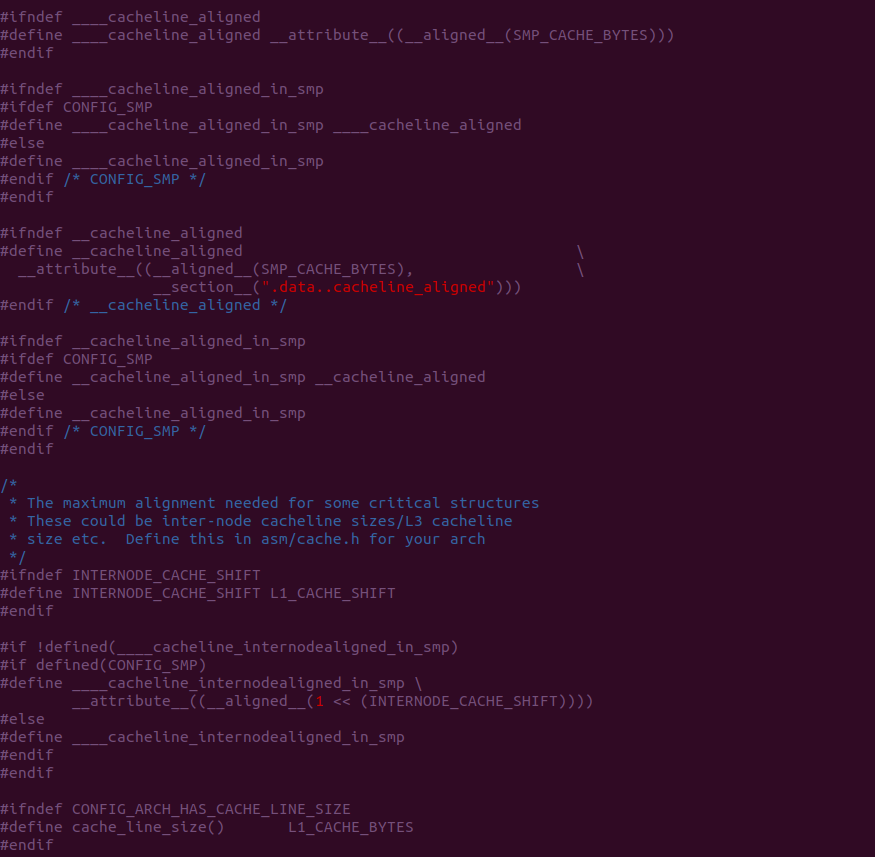

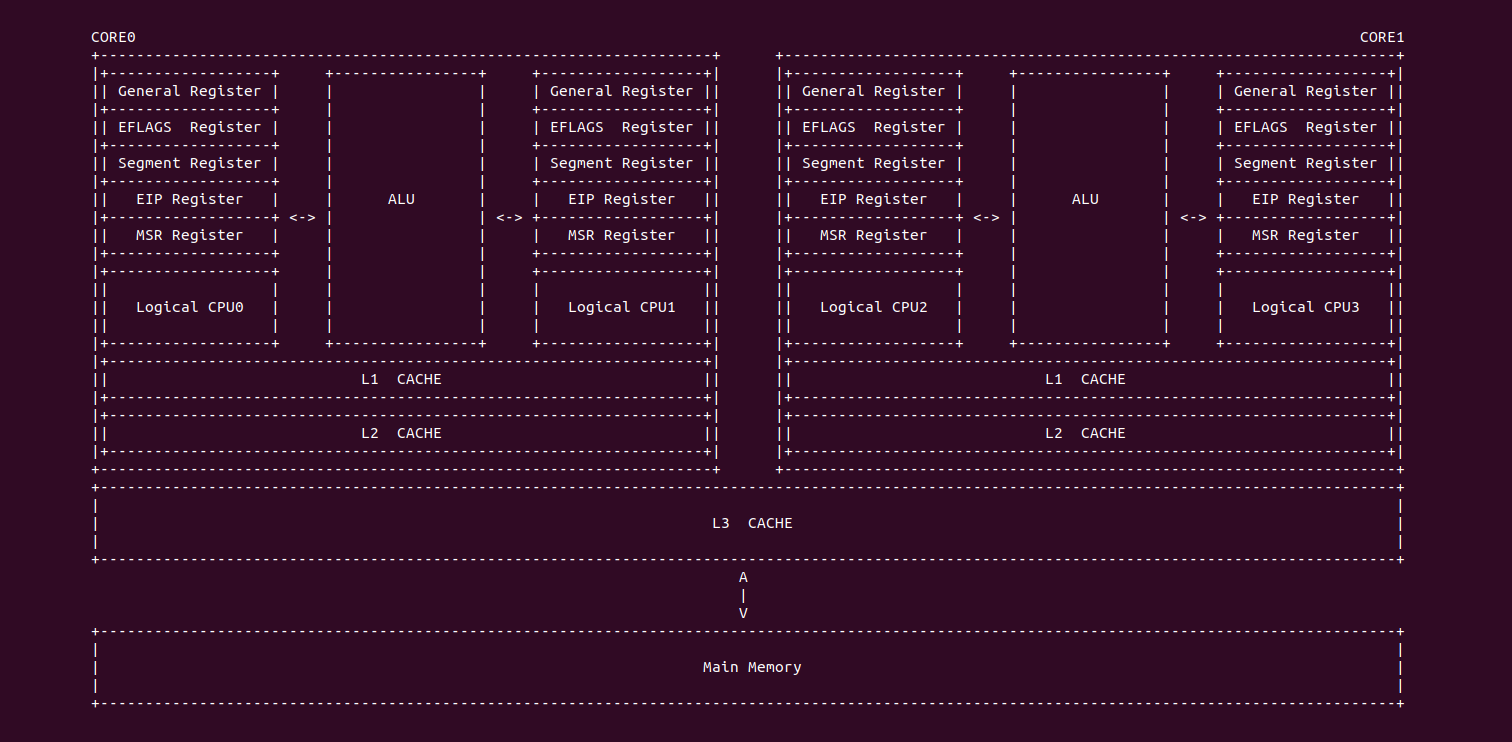

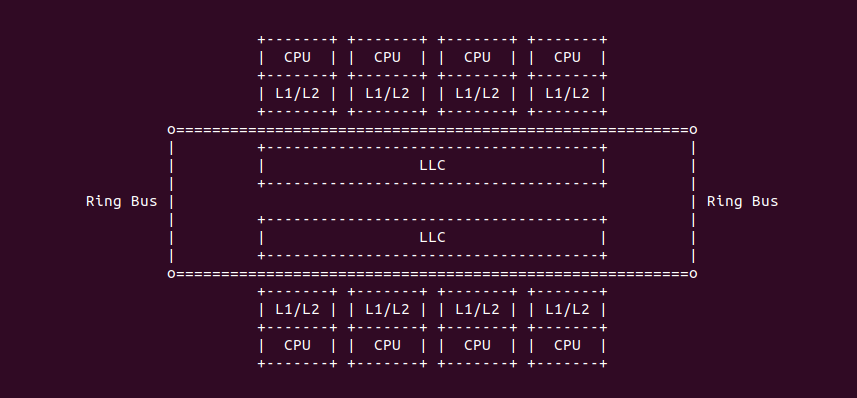

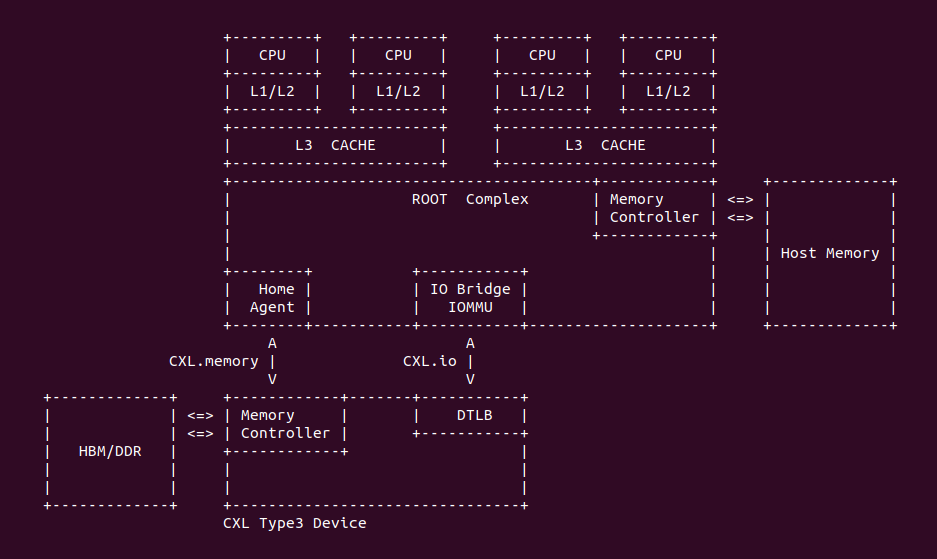

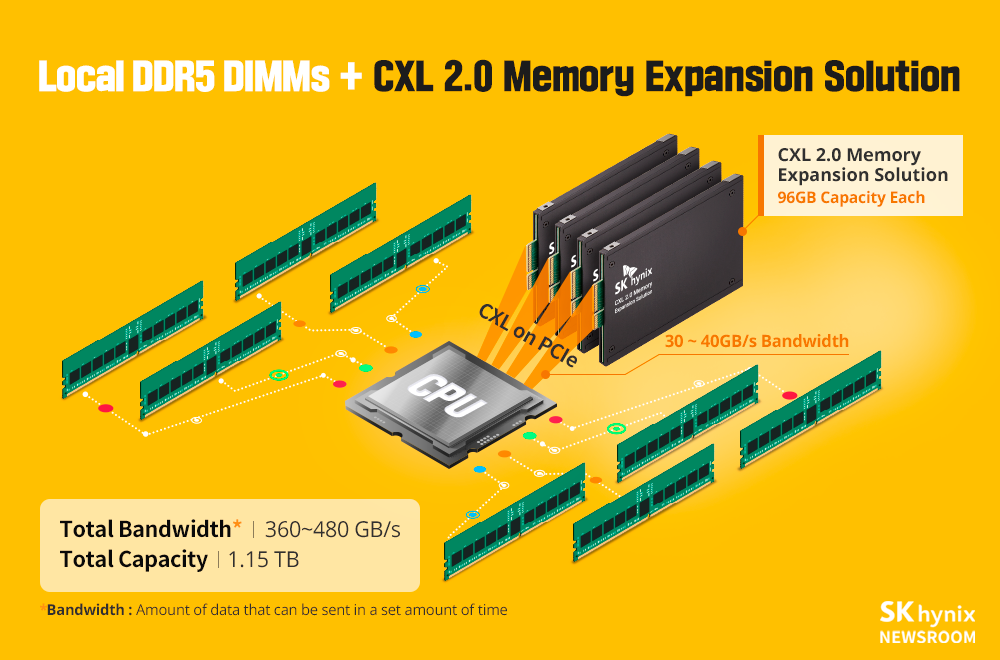

多级 CACHE 架构

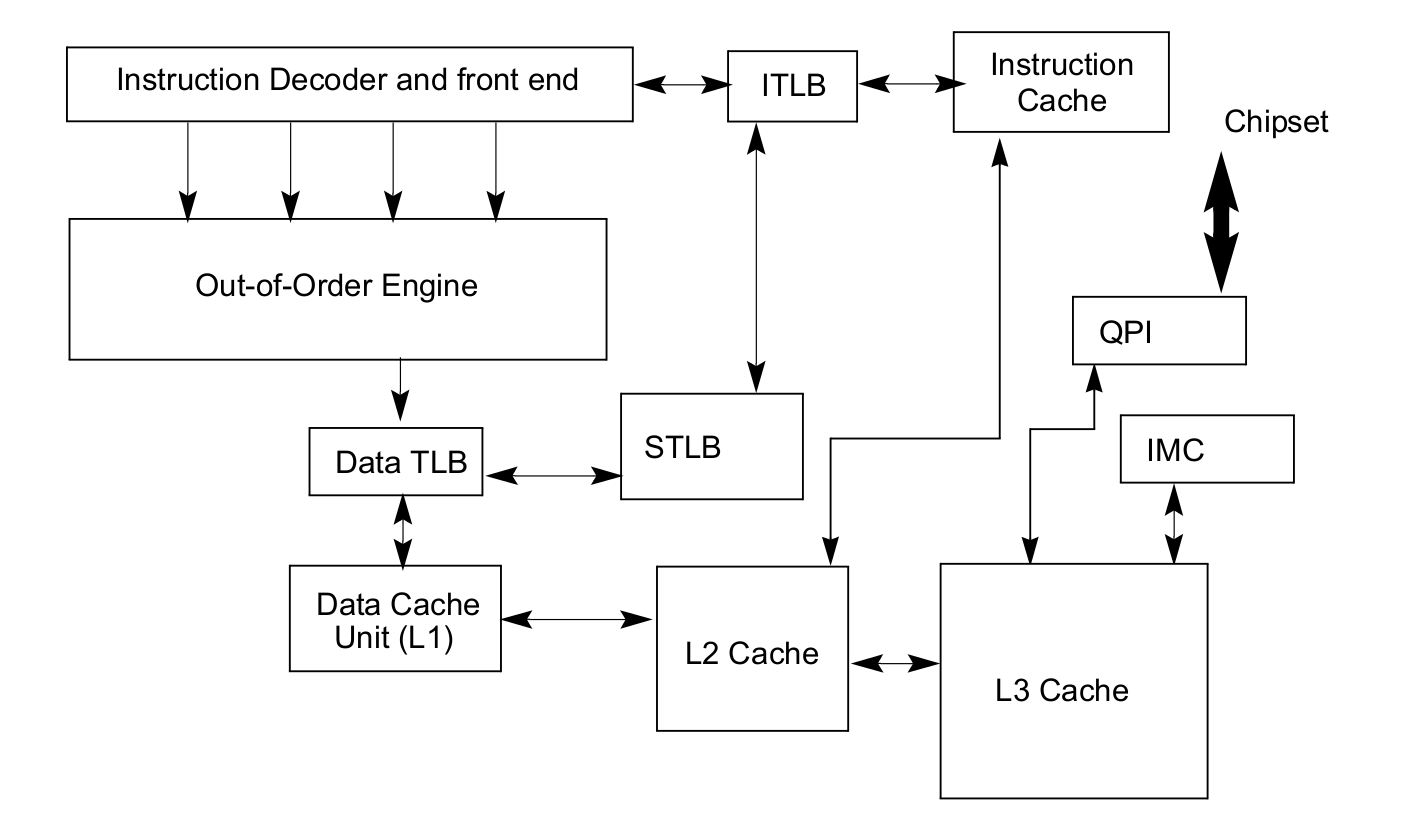

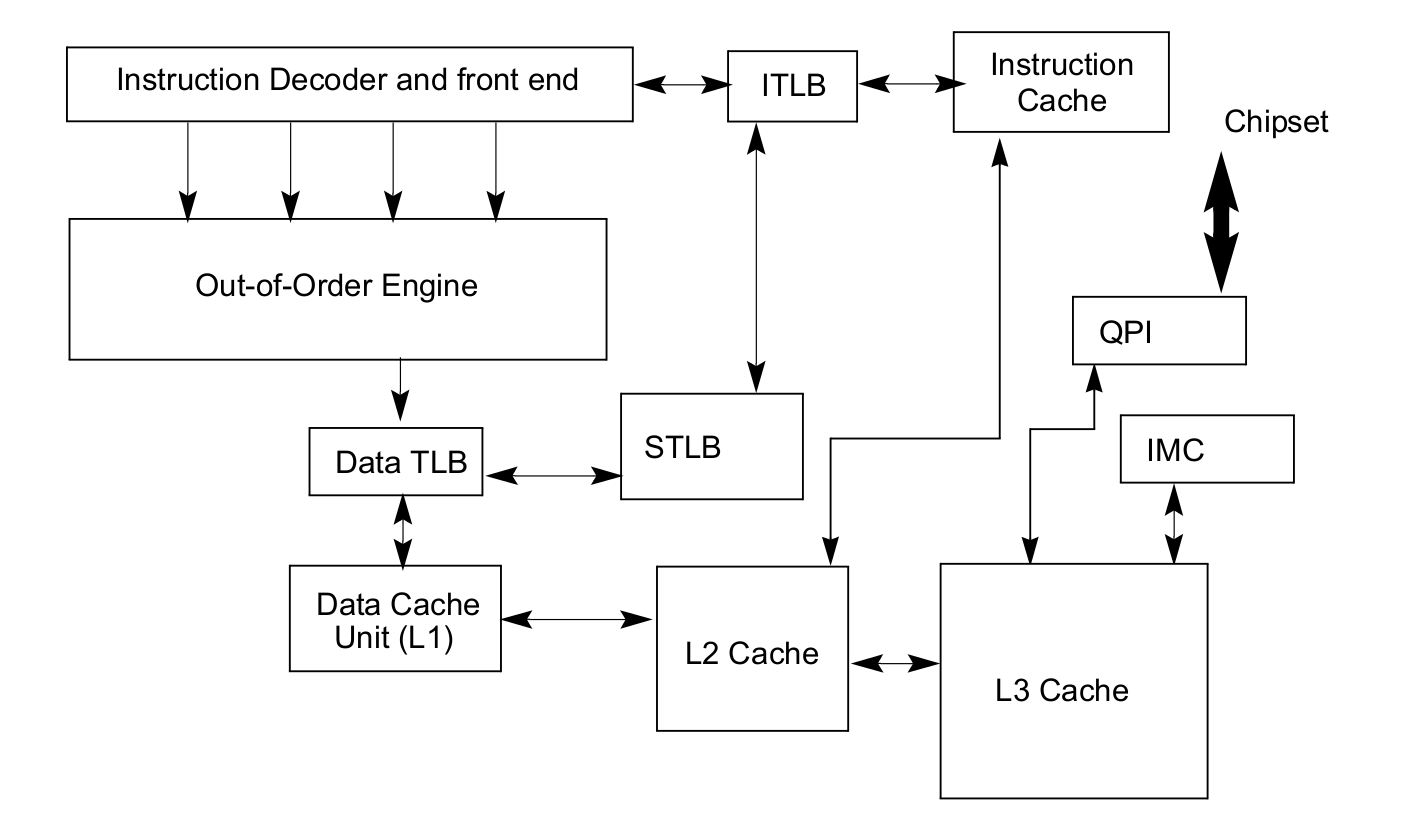

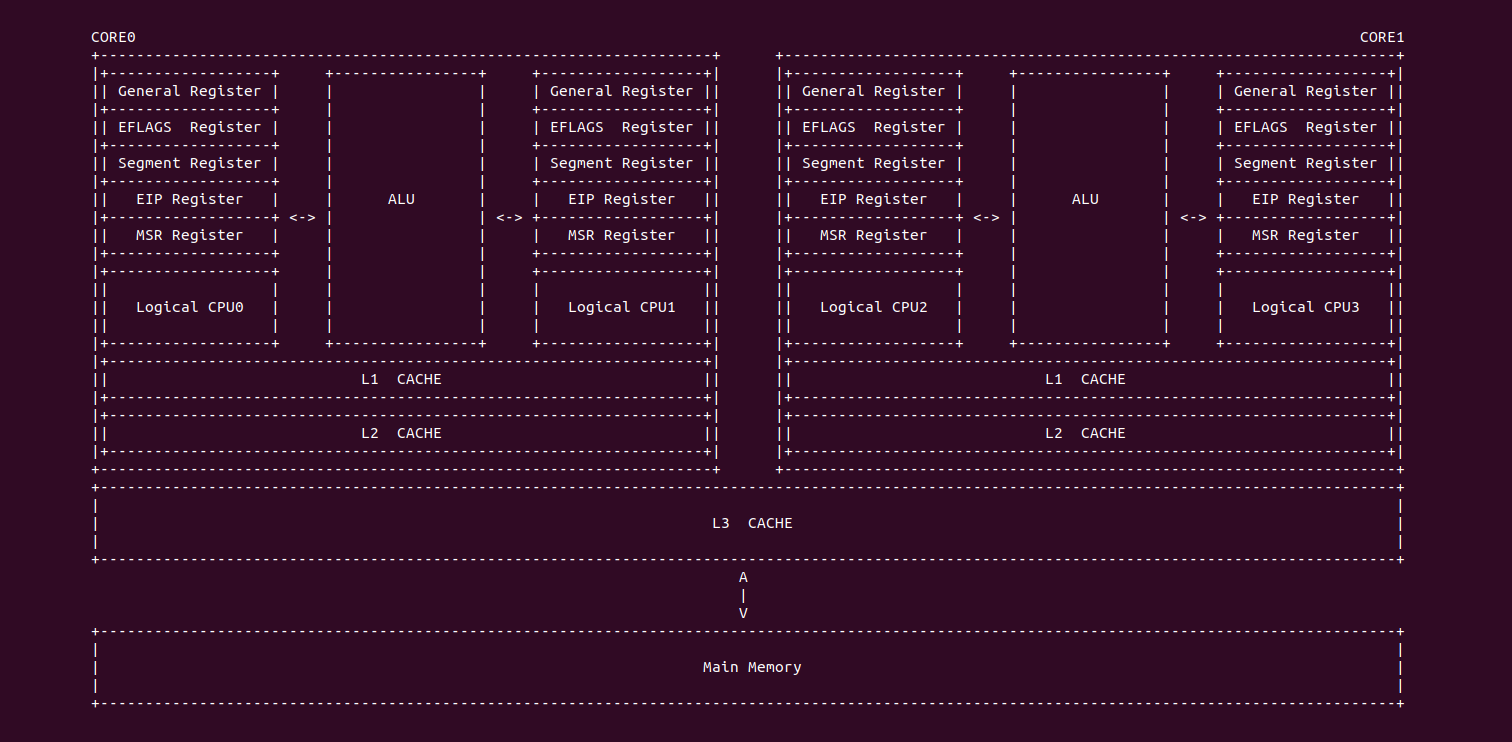

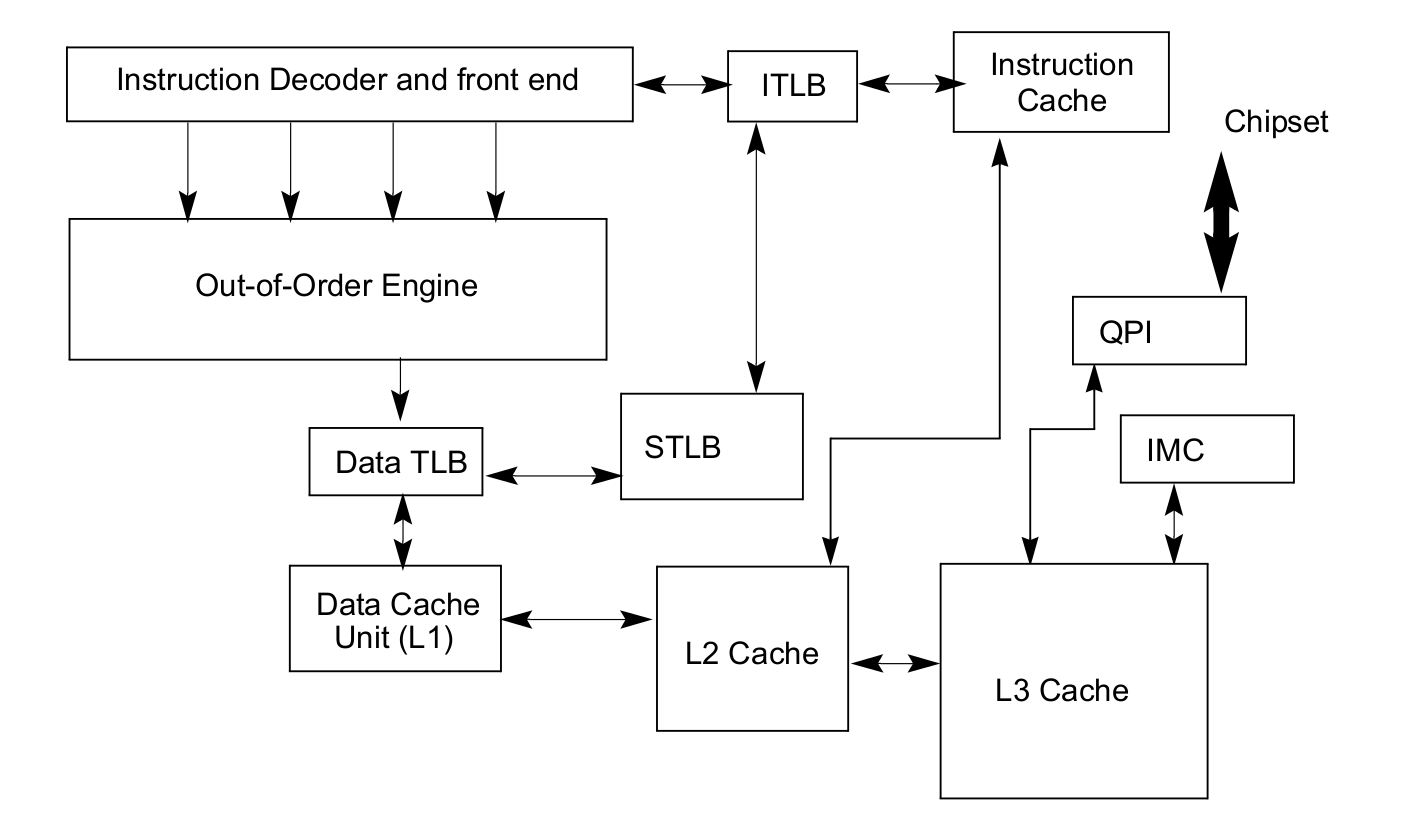

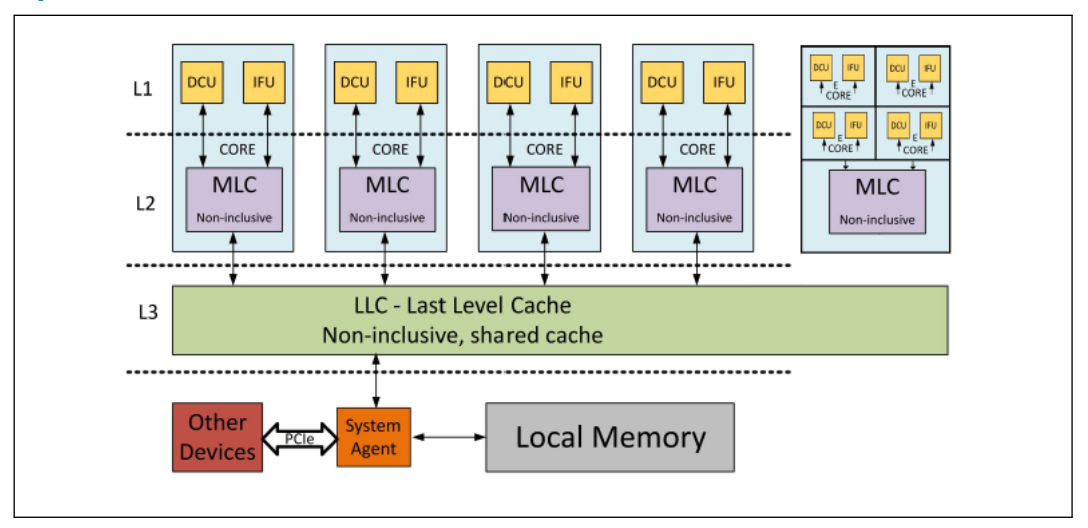

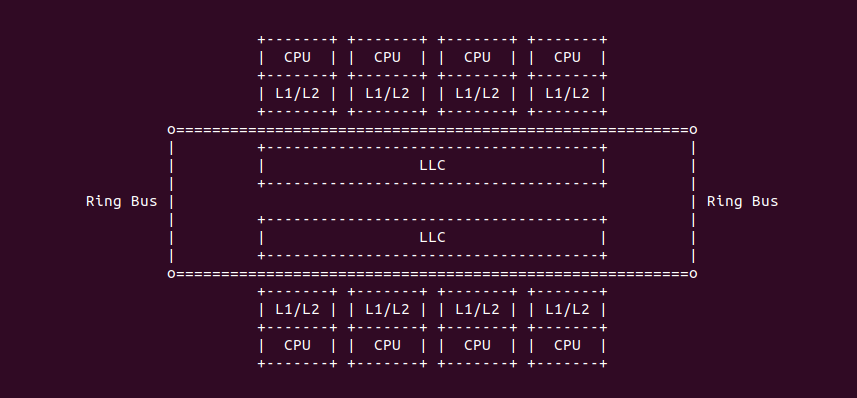

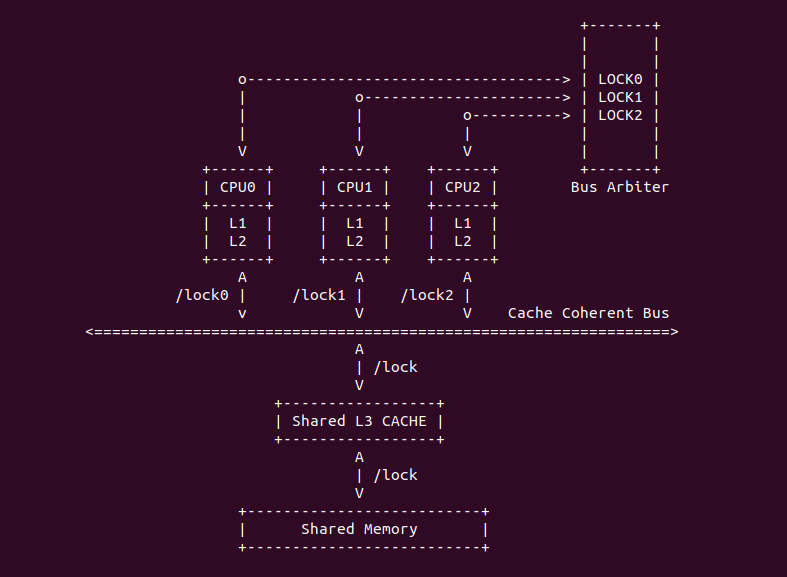

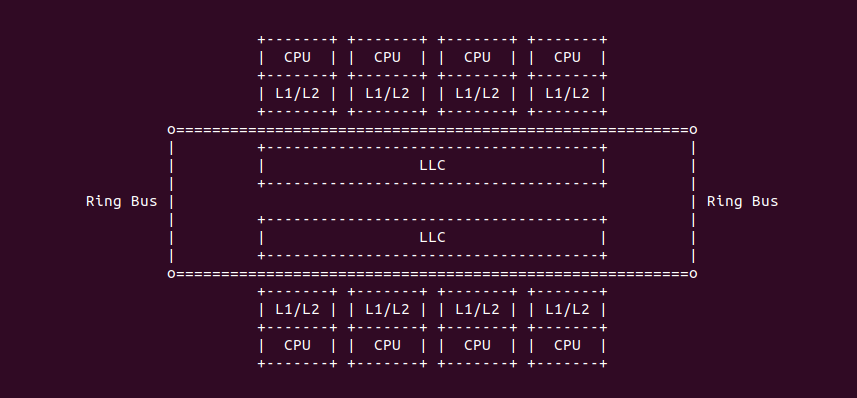

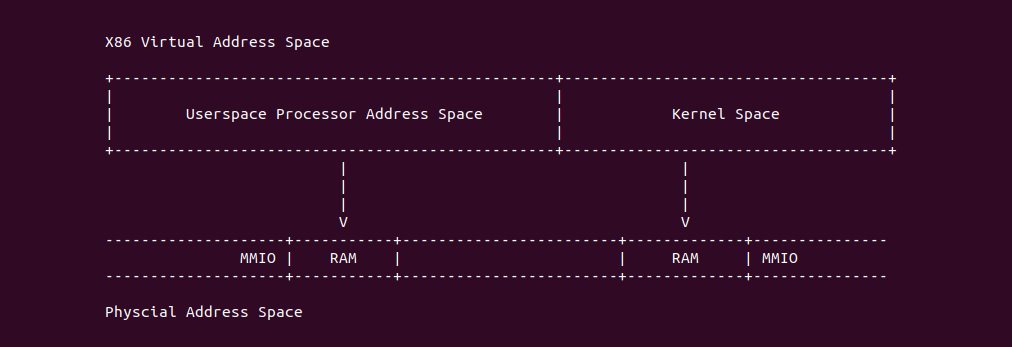

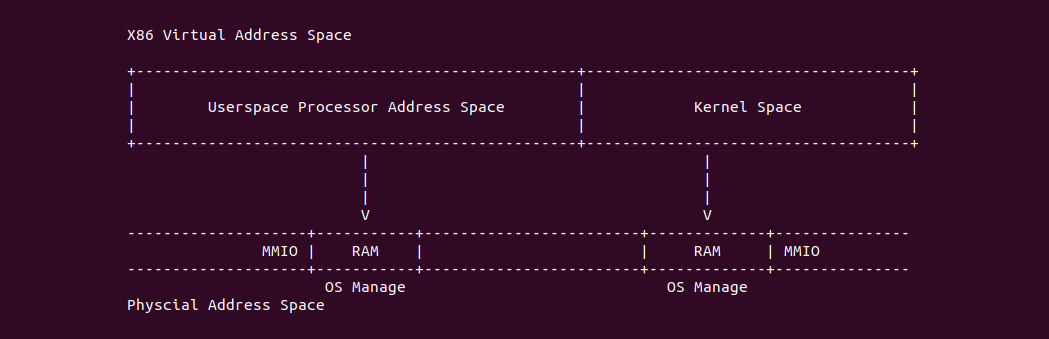

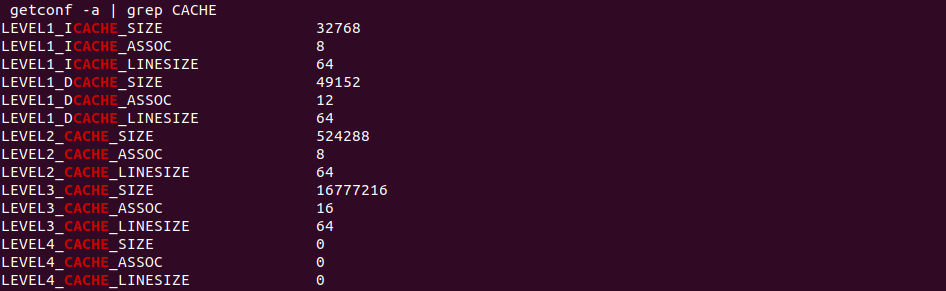

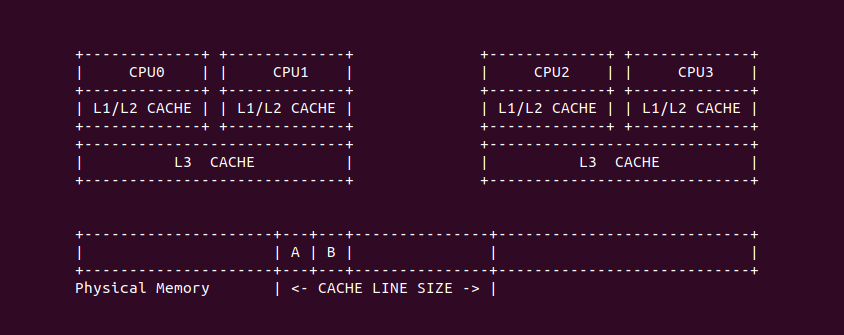

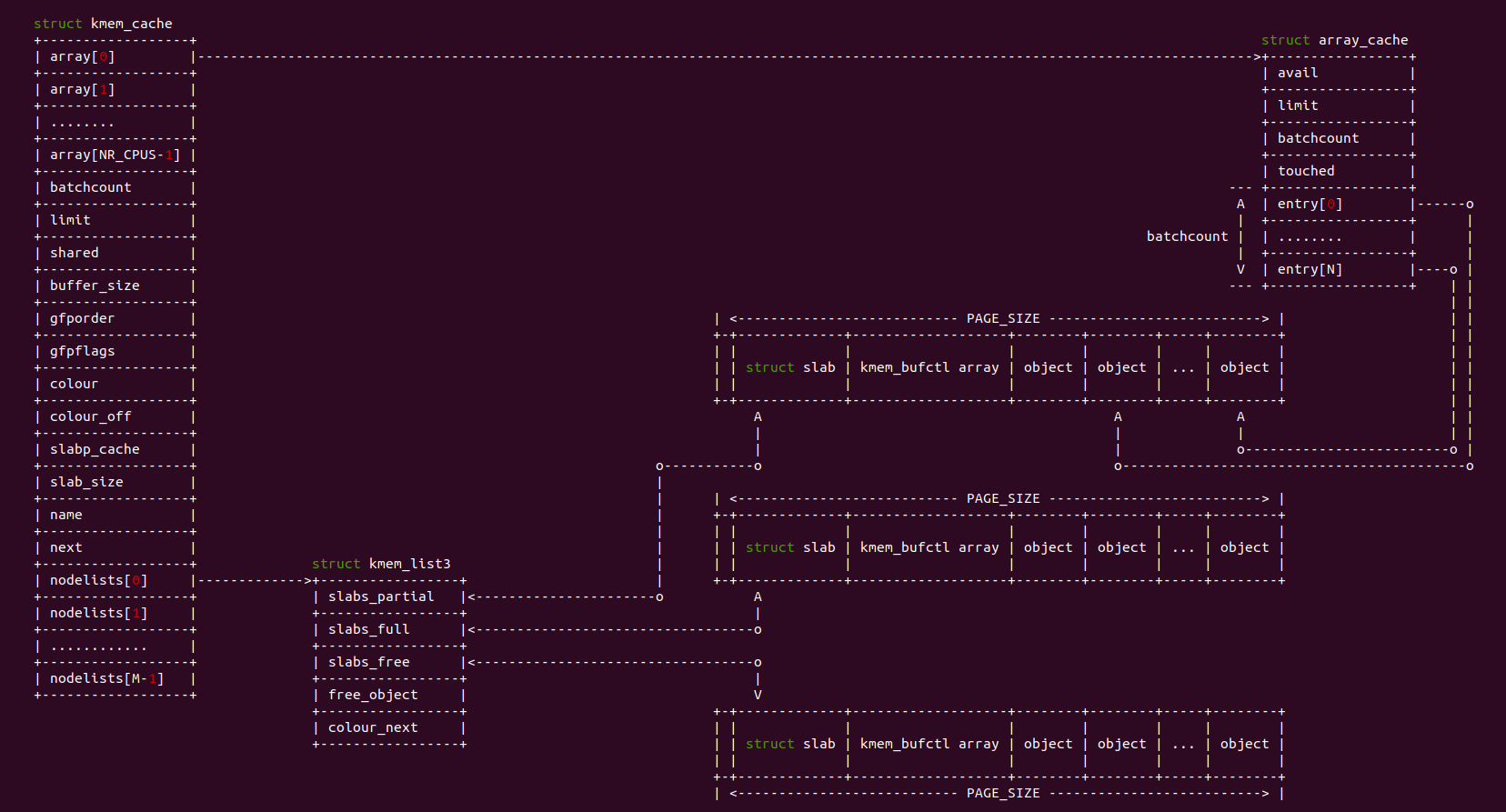

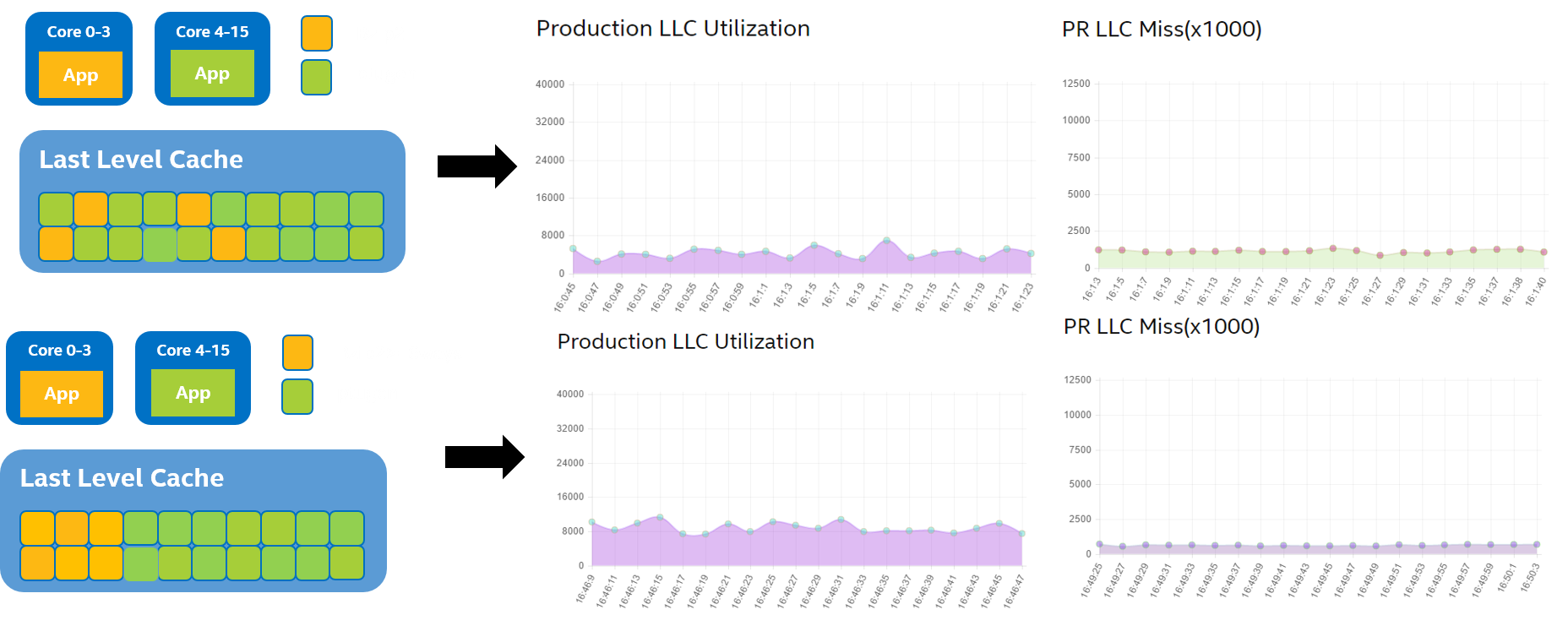

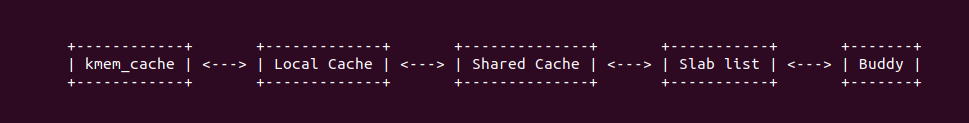

随着多核技术的不断普及以及摩尔定律的失效,CPU 的频率已经不是限制性能的主要因素,内存访问延时成为了系统性能的瓶颈,各大厂商在多核架构下通过增加 CACHE 的级数和 CACHE 容量,以此来加速对内存的访问。例如在 Intel 架构下,一个物理 Core 包含了两个逻辑核,两个逻辑核共用 L1 和 L2 CACHE,也就是一个物理核只有一个 L1 和 L2 CACHE。一个 CPU Socket 上面可能有一个或多个物理核,这些物理核共用 L3 CACHE,L3 CACHE 也被称为 LLC(Last Level CACHE),L2 CACHE 则被称为 MLC(Middle LeveL CACHE). L1 CACHE 又分为 Data CACHE 和 Instruct CACHE. 在有的架构中可能存在 4 级 CACHE,本文重点描述 3 级 CACHE 的架构.

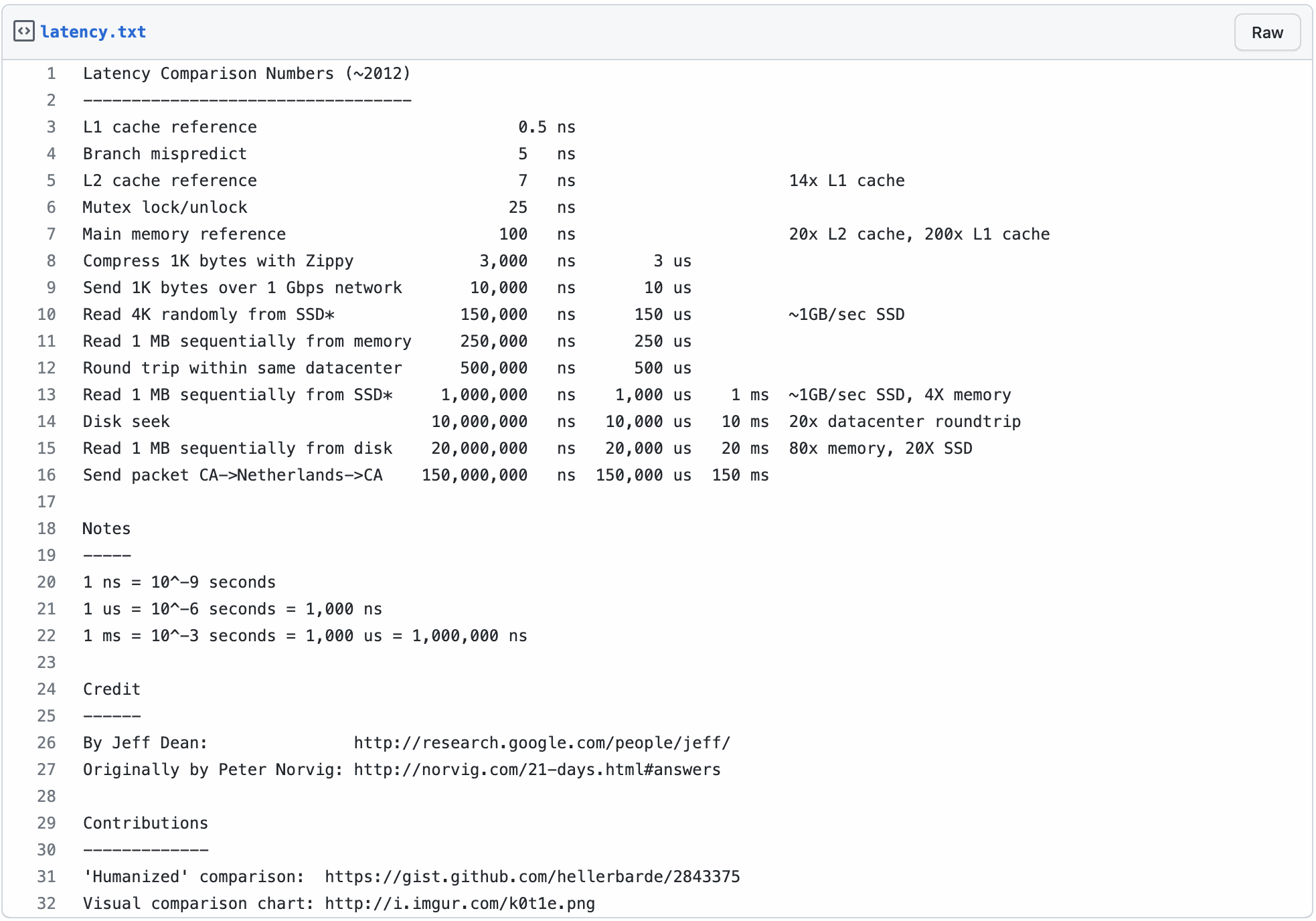

上表是 X86 架构下各级 CACHE 的 latency,CPU 访问每一级 CACHE 的延时不相同,L1 CACHE 的延时基本和指令执行的周期一致,MLC 的延时为 7ns,访问主存的时延是 100ns. 为什么采用多级 CACHE 架构就能显著提升系统性能呢? 这里通过一个例子进行讲解:

- 假设把 CPU 的一个时钟周期看做 1s,系统访问数据比作在图书管理里面查资料

- 从 L1 CACHE 读取信息就好比拿起桌上一张草稿纸(3s), 草稿纸上没有则从书包里找.

- 从 L2 CACHE 读取信息就好比是从书包里找书(14s). 书包里如果没有则去书架上找.

- 从 L3 Cache 读取信息好比从身边的书架上取出一本书(60s). 3 楼书架没有则去 1 楼书架找.

- 从主存中读取数据好比从 3 楼去 1 楼书架上查找(6 分钟). 1 楼没有则联系开发商补书.

- 从磁盘中读取数据好比联系开发商重新补印书本(长达一年零三个月).

通过上面的例子就知道多级 CACHE 对系统性能提升的重要性了吧,可以看到在性能极佳的场景下,CPU 访问的数据都在 L1 CACHE 中,系统基本没有延时的访问数据。而性能最差的场景则是所有访问的数据都在磁盘上, 系统大部分时间浪费在等待磁盘访问上,这简直是系统的噩耗.

多级 CACHE 架构发展

最早出现缓存的时候其实是单级缓存(L1 CACHE), 但随着技术的不断演进,多级缓存提供了更好的低平均请求延迟 Latency(平均所有命中和未命中). 另外目前处理器采用多核架构,所有核心都共享连接相对高延迟的 DRAM,因此多级是必不可少的。另外一个原因是多级缓存设计可以分开设计功率,而功率/热量是现代 CPU 设计中最重要的限制因素之一. 目前的 CPU 处理器都有 3 级 CACHE,但是三者存在明显差异。L1 CACHE 注重速度,L2 CACHE 要在 L1 CACHE Miss 之后才发挥作用,更注重节能和容量,L3 CACHE 则更追求容量和共享。但查询一个地址时,L1、L2 和 L3 的行为是不同的:

- L1 CACHE 会把多个 CACHE Line 的 Tag 和数据全部取出,然后再比较 Tag 看哪个命中或者都没命中,如果命中直接使用数据.

- L2 CACHE 虽然也是 N 路组相联,但比较时先只取 Tag,当找到命中的 CACHE Line 之后再去把对应的数据取出来.

- L3 CACHE 位于核外,多个物理核共享,因此还需要额外考虑一致性等.

L1 CACHE

L1 CACHE 与 CPU Core 紧密耦合,CPU 每次访问内存时都会访问 L1 CACHE,需要非常快速地返回数据,通常延时在 0.5ns,基本和时钟周期一致,因此 L1 需要非常快(低延时和高吞吐), 也意味着其命中率有限. 为了提高带宽,需要大量的读写端口来支持 L1 CACHE 的高速访问,端口数量是一个非常重要的设计点,会消耗芯片面积,这是因为端口会向 CACHE 添加线路(铜线). 同时高吞吐量也意味着能够在每个周期处理多个读取和写入(多个端口),使得功率暴增.

L1 CACHE 又分配 L1 Data CACHE(L1D) 和 L1 Instruction CACHE(L1I), 其在 CPU 内部的布局如上图。L1I 可以放置在物理上接近代码获取逻辑,而 L1D 可以放置在物理上靠近加载/存储单元. 这样的设计当时钟周期仅持续 1/3 纳秒时(2.5GHz, 为 0.4ns),光速传输线延迟也称为大问题,所以布线也很重要(例如 Intel 最新处理器硅片上有 13+ 层铜,类似 PCB 13 层板).

L1 CACHE 容量: L1 CACHE 的特点就是快,如果 L1 变得更大,它将增加 L1 访问延迟从而降低性能, 因此 L1 CACHE 的大小几乎没有争议。目前主流处理器的 L1 CACHE 大小为 64KiB。即使决定增加 L1 CACHE,L2 CACHE 也会同步跟进增加,以此加速 L1 CACHE Miss,但这样带来了成本和功耗的暴增.

L2 CACHE: MLC

系统中如果不存在 L2 CACHE,那么 L1 CACHE Miss 之后直接从主存中存取数据, 这样直接导致很多访问进入内存,不但意味着需要更多的内存带宽,也意味着性能严重降级. 所以 L2 CACHE 是为了缓解内存带宽压力,保持 L2 CACHE 一定大小,使其具备一定的带宽能力是非常必须的。如果架构中没有 L3 CACHE,那么 L2 CACHE 通常作为带宽过滤器,减少内存带宽使用. 如果架构中包含 L3 CACHE,那么 L2 CACHE 可以有效减少对片上互联和对 L3 的访问.

L2 CACHE 没有像 L1 CACHE 分为 L1 Data CACHE 和 L1 Instruction CACHE,而是无差别对待指令和数据,因此称 L2 CACHE 为 L2 Unitied CACHE. L2 CACHE 的位置如上图,其位于 CPU CORE 内部,被多个逻辑核共享,且每个物理核只有一个 L2 CACHE. 虽然 L1 区分指令和数据对速度有很多的帮助,当统一的 L2 CACHE 还是最佳的选择,因为有些任务的代码量比较小,但其数据量远大于代码量,L2 CACHE的统一以适应不同的任务负载是有意义,而不是静态地划分为代码和数据.

L3 CACHE: LLC

主流的架构中都包含了 L3 CACHE,并且 L3 CACHE 作为最后一级 CACHE,简称为 LLC. L3 CACHE 不在物理核内部,其位于一个 CPU Socket 内部,被多个物理核共享. L3 CACHE 通常使用 ECC,可以完成 ECC 在较大的块上以降低开销. 相对 L2 CACHE,L3 CACHE 速度更慢,慢速可以以较低的电压/时钟速度运行,减少热量. 甚至可以为每个存储单元使用不同的晶体管布置,以使存储器更优化功率而不是高速存储器.

Inclusive 与 Exclusive

在 《CACHE 一致性章节》描述了 MESI 如何维护 CACHE 一致性的,其中 CACHE Line 具有 Exclusive 状态,其表示只有该 CPU 缓存了 CACHE Line,并且 CACHE Line 中的内存与主存中的一致.

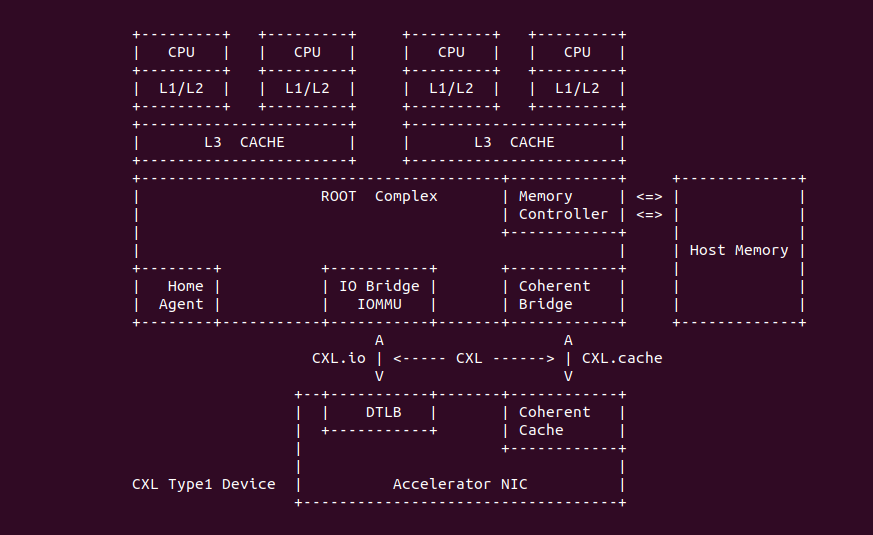

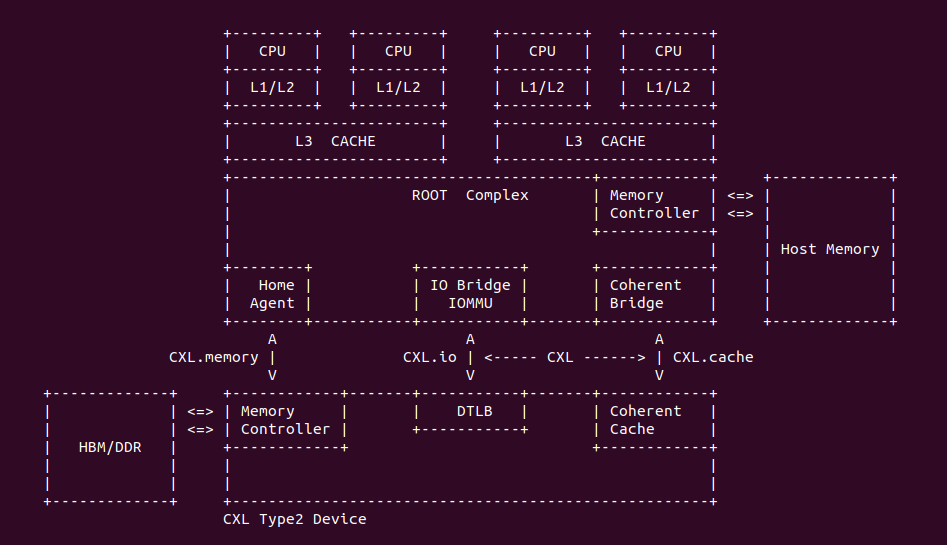

Intel® X86 架构 CACHE 机制

Intel® Core-i7 and Xeon CACHE

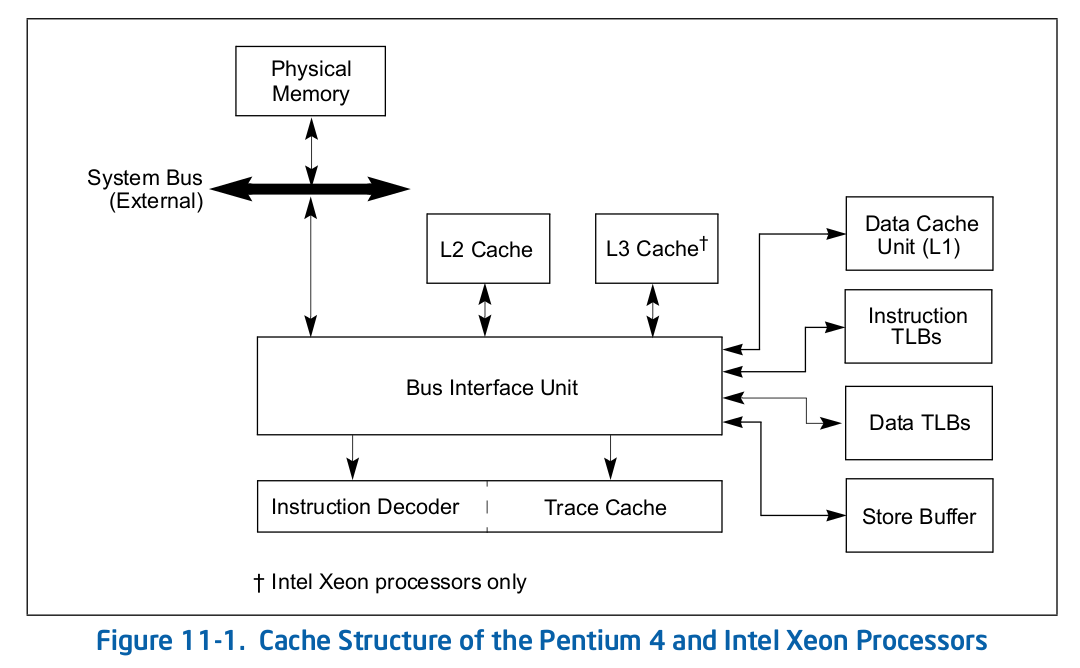

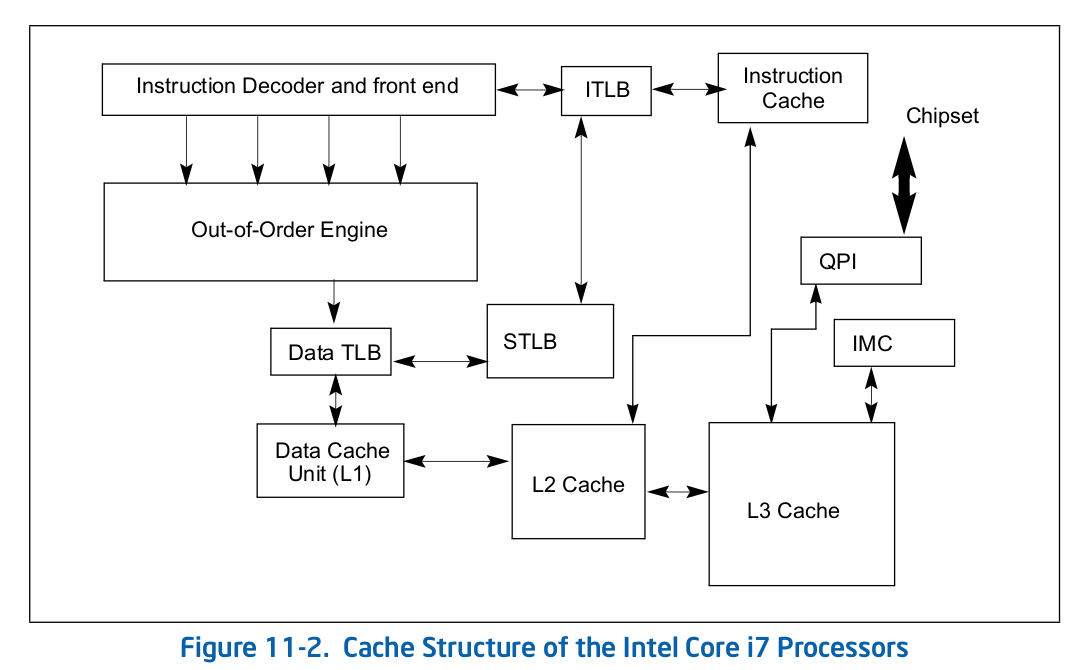

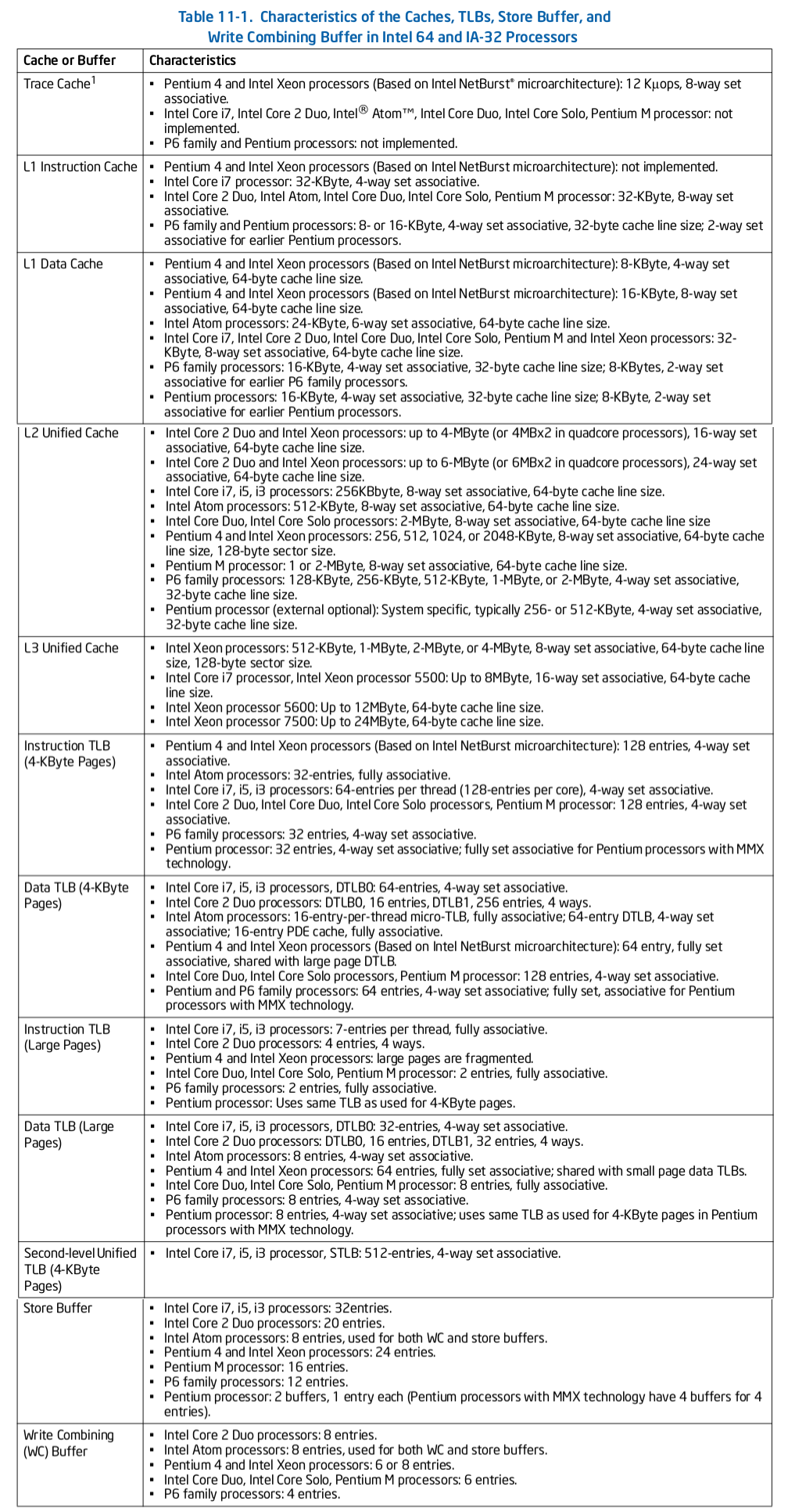

Intel 64 架构和 IA-32 架构的 CACHE 系统由Data CACHE Unit(L1)、Instruction CACHE、Data TLB、Instruction TLB、L2 CACHE、L3 CACHE、Store Buffer 以及 Trace CACHE 等硬件组成,不同系列的处理器 CACHE 架构可能有所差异,大体上可以分为 Xeon 系列和 Core 系列,Figure 11-1 展示 Xeon 系列处理器 CACHE 基本组成架构,Figure 11-2 则展示了 Core i7 处理器的 CACHE 基本架构。两种图的差异不仅体现在硬件组织方式,还体现在同种硬件的大小,其与具体的系列有关系,那么接下来对每种硬件进行介绍:

Trace CACHE Trace CACHE 是一种加快指令提取的技术,使用处理器能以更短时间读取更多的指令,能有效的提高处理器性能. L1 Instruct CACHE 片上 L1 指令 CACHE,靠近代码获取逻辑,专门用于缓存指令,加速指令的读取. L1 Data CACHE 片上 L1 数据 CACHE,靠近加载/存储单元,专门用于缓存数据,加速数据的读取. L2 Unitied CACHE 片上的 L2 CACHE,不区分指令和数据,缓解内存带宽压力,通常作为带宽过滤器. L3 Unified CACHE 被同一个 Socket 上的物理核共享,不缺分指令和数据,缓解内存带宽压力. Instruction TLB(4-KByte Pages) 用于缓存 L1 Instruction CACHE 中虚拟地址到 4KiB 物理页的映射关系, 加速地址翻译.

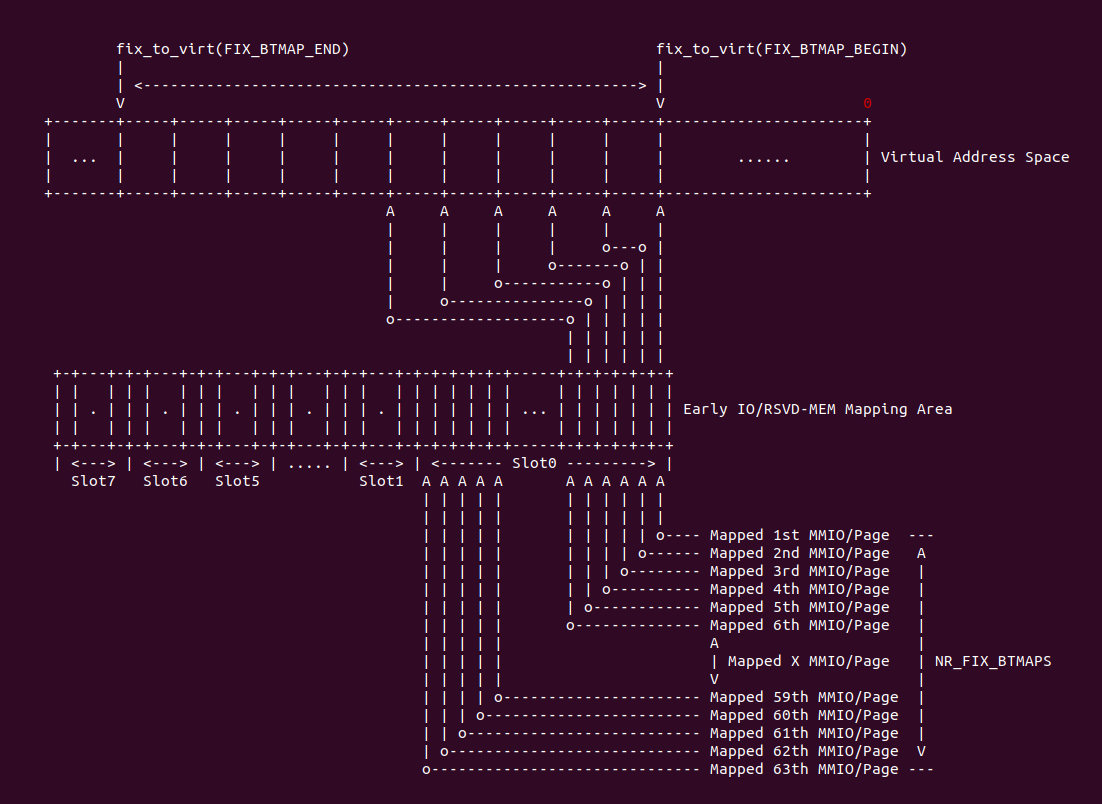

Data TLB(4-KByte Pages) 用于缓存 L1 Data CACHE 中虚拟地址到 4KiB 物理页的映射关系, 加速地址翻译. Instruction TLB(Large Pages) 用于缓存 L1 Instruction CACHE 中虚拟地址到巨型物理页(2M/1G/512G HugePage)的映射关系,加速地址翻译. Data TLB(Large Pages) 用于缓存 L1 Data CACHE 中虚拟地址到巨型物理页(2M/1G/512G HugePage)的映射关系, 加速地址翻译. Second-level Unified TLB(4-KByte Pages) 用于缓存 L2 Unified CACHE 中虚拟地址到物理页的映射关系,加速地址翻译. Store Buffer 可先将 CPU 写数据缓存到 Store Buffer,然后给其他 CPU 发送消息,然后处理其他事,待其他 CPU 发送应答消息之后,再将数据从 Store Buffer 写入到 CACHE Line. Write Combining(WC) Buffer 当 L1 CACHE Write Miss,WC Buffer 为了减少 Write Miss 带来的性能开销,可以把多个对同一 CACHE Line Store 操作的数据放到 WC Buffer,等到需要读取时再一次性写入,以此减少写入的次数和总线的压力.

Table 11-1 描述了各硬件在不同系列的 Intel 处理器的大小信息.

Intel® Smart CACHE Technology

在 Intel 12 代 Core CPU 上使用了 Smart CACHE 技术,其共享了最后一级缓存 LLC. 由于共享了最后一级 CACHE,那么 LLC 具有了 non-inclusive 特点,LLC 被所有的物理核共享(因为只有一个 Socket). 上图为 12 代 CPU 的 Hybrid CACHE 架构, CPU 被换分为 P-Core 和 E-Core,P-Core 用于处理较重的任务,而 E-Core 则是低功耗且处理相对轻松的后台任务.

L1 CACHE: P-Core 的 L1 CACHE 被分为数据 CACHE (DFU) 和指令 CACHE (IFU), L1 CACHE 包含了 48KiB 的 DFU 和 32KiB 的 IFU, L1 CACHE 是一个 12-Way 的组相联 CACHE 架构, P-Core L1 CACHE 不被其他物理核共享. E-Core 的 L1 CACHE 同样被分为数据 CACHE(DFU) 和指令 CACHE(IFU), L1 CACHE 包含了 64KiB DFU 和 32KiB IFU,E-Core 的 L1 CACHE 是一个 8-Way 的组相联 CACHE 架构, E-Core L1 CACHE 不被其他物理核共享.

L2 CACHE: L2 CACHE 不区分数据和指令,其也被称为 MLC. P-Core L2 CACHE 大小为 1.25MiB, 10-Way non-inclusive 组相联 CACHE 结构,P-Core 不与其他物理核共享 L2 CACHE. E-Core 由 4 个物理核共享一个 L2 CACHE,其 16-Way non-inclusive 组相联的 2MiB CACHE.

L3 CACHE: L2 CACHE 不区分数据和指令,其被称为 LLC. LLC 被所有 P-Core 共享,且每个 P-Core 物理核最大包含 3MiB 的 12-Way 组相联 CACHE. LLC 也被所有 E-Core 共享,但 4 个 E-Core 包含 3MiB 的 12-Way 组相联 CACHE.

From《2.4.2 12 IA Cores L1 and L2 Caches - 12th Generation Intel® Core ™Processors》

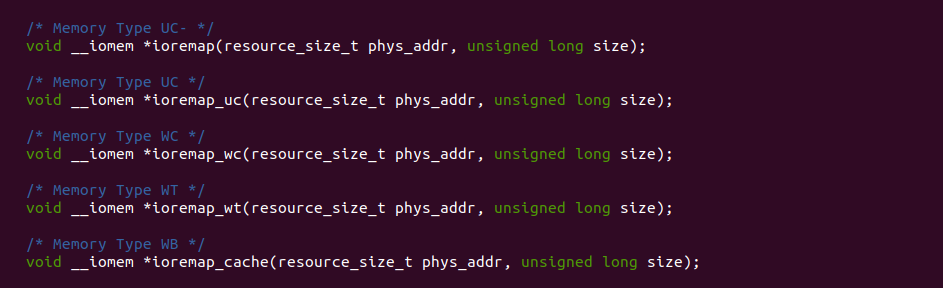

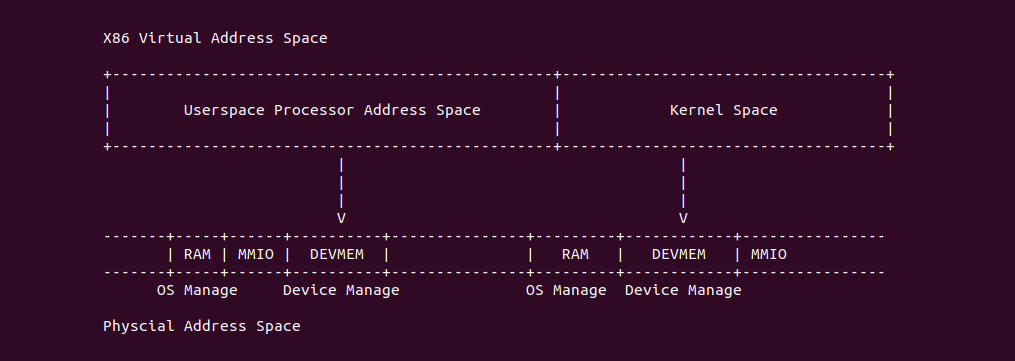

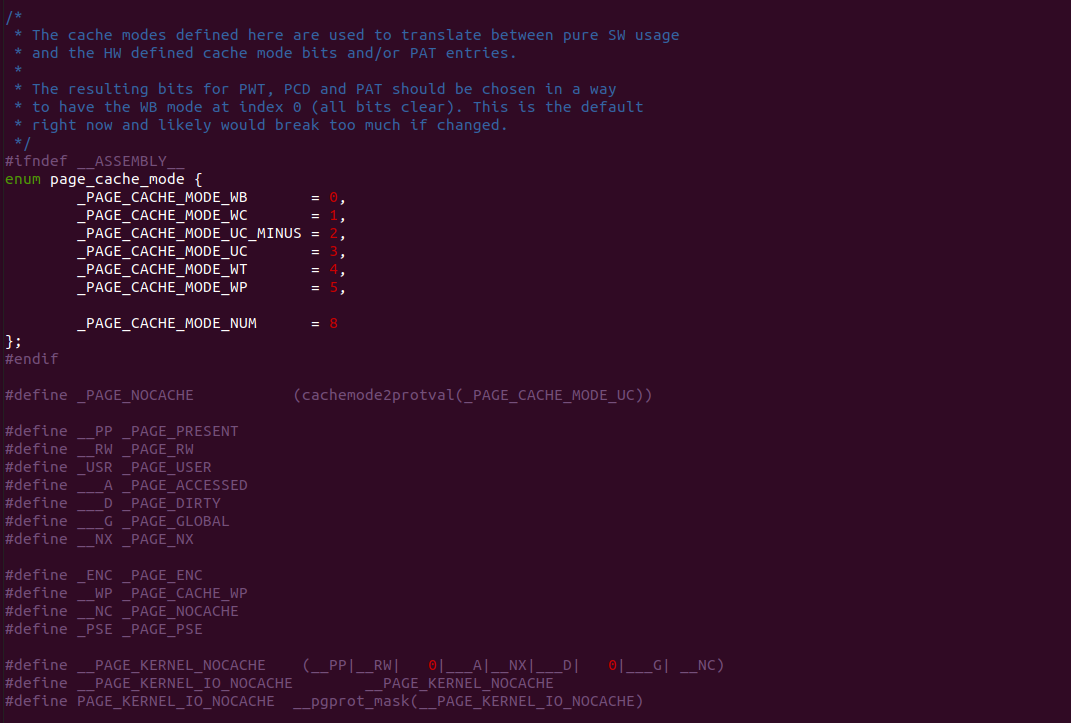

Intel® Memory Type

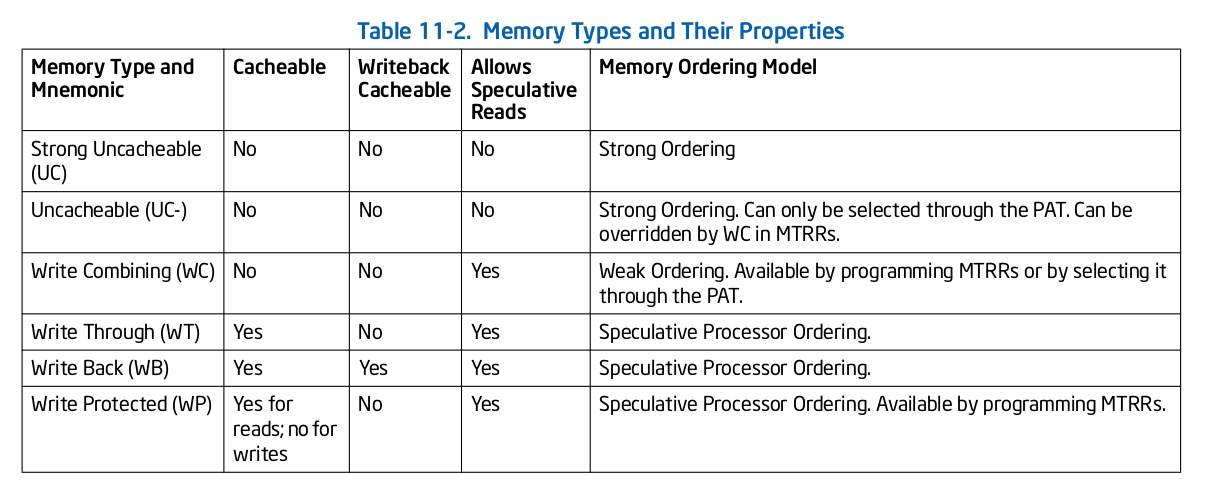

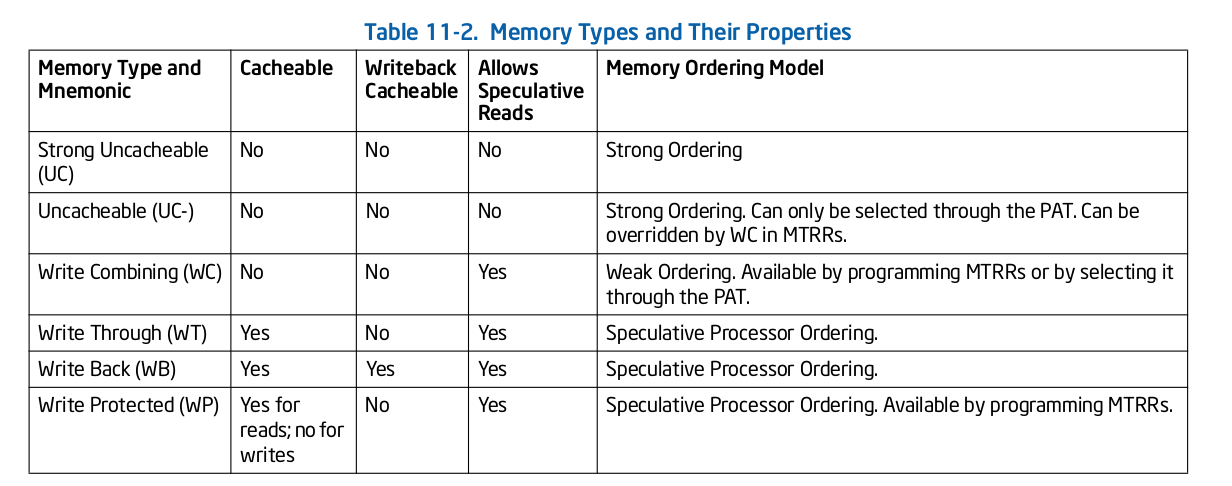

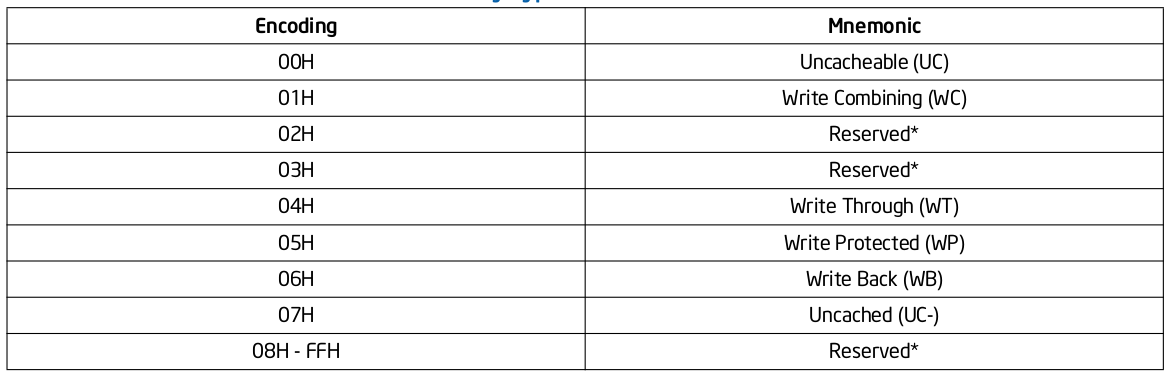

Intel X86 架构可以将所有的物理内存缓存到 L1/L2/L3 CACHE, 并且架构支持按独立页或者独立区域的粒度设置物理内存的缓存方式,在 Intel 架构下将物理内存缓存方式称为 memory type. Table 11-2 定义了 Intel 64 和 Intel IA-32 架构都支持的 memory type, 包括了 UC/UC-/WC/WT/WB/WP, 那么接下来对每种缓存类型进行详细的分析.

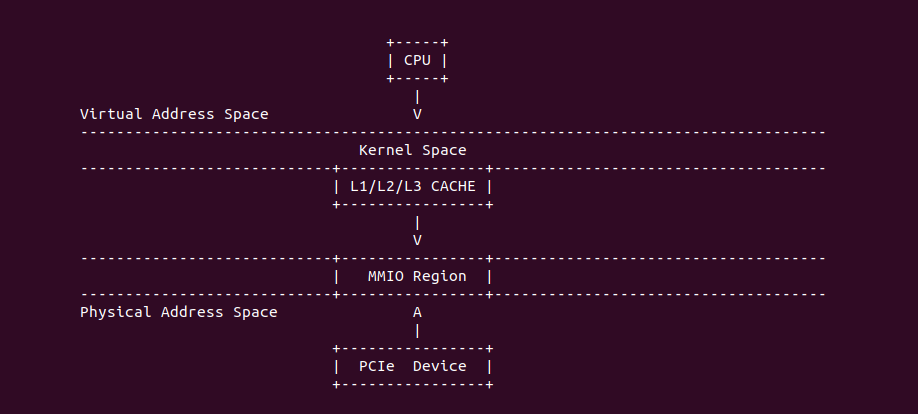

Strong Uncacheable (UC)

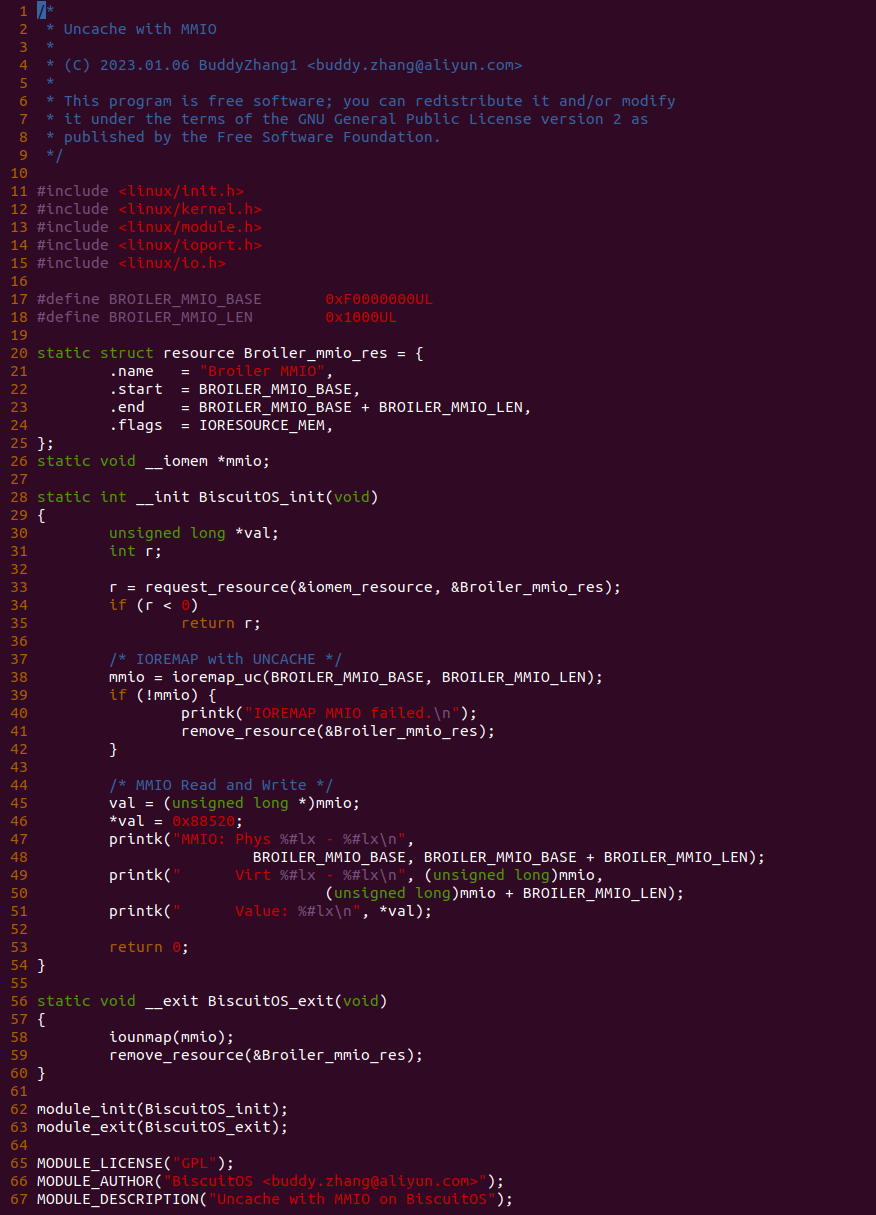

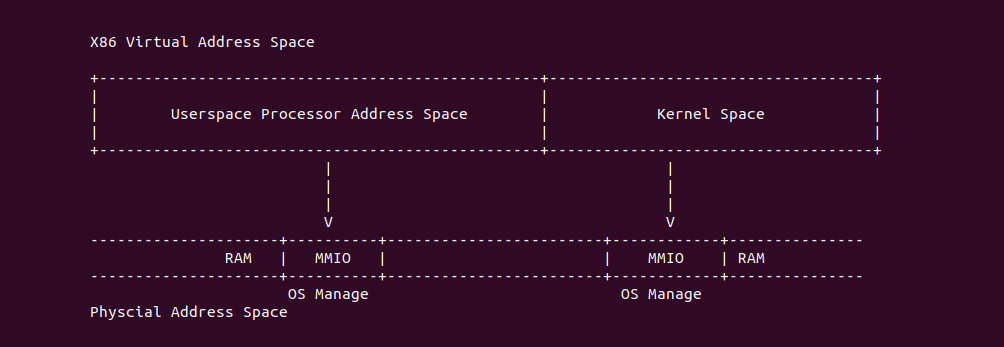

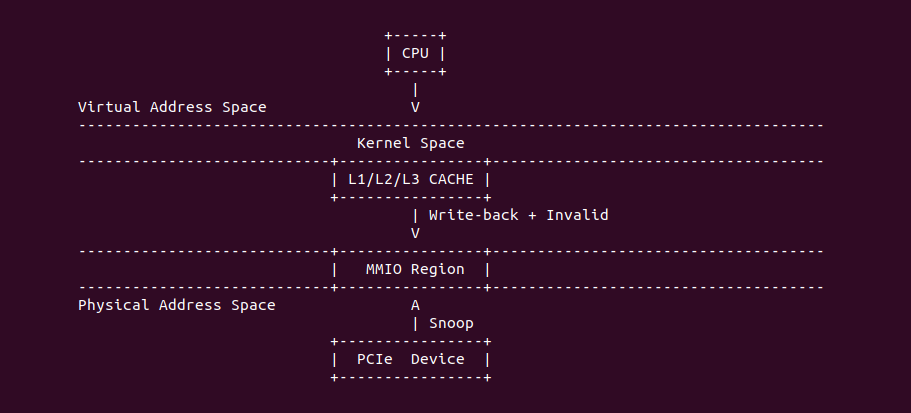

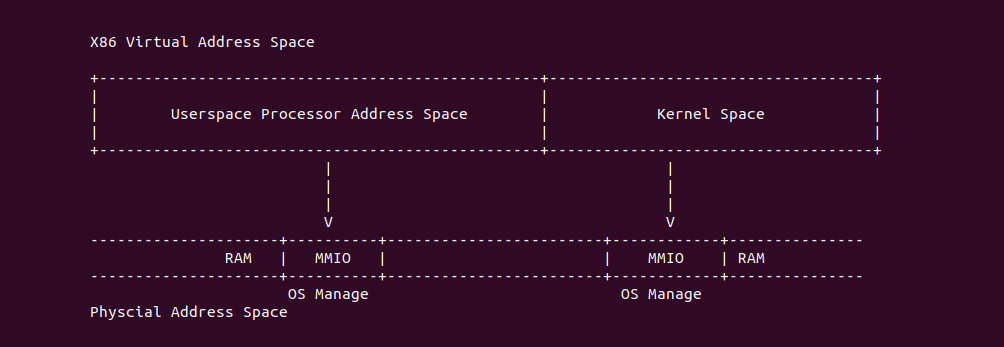

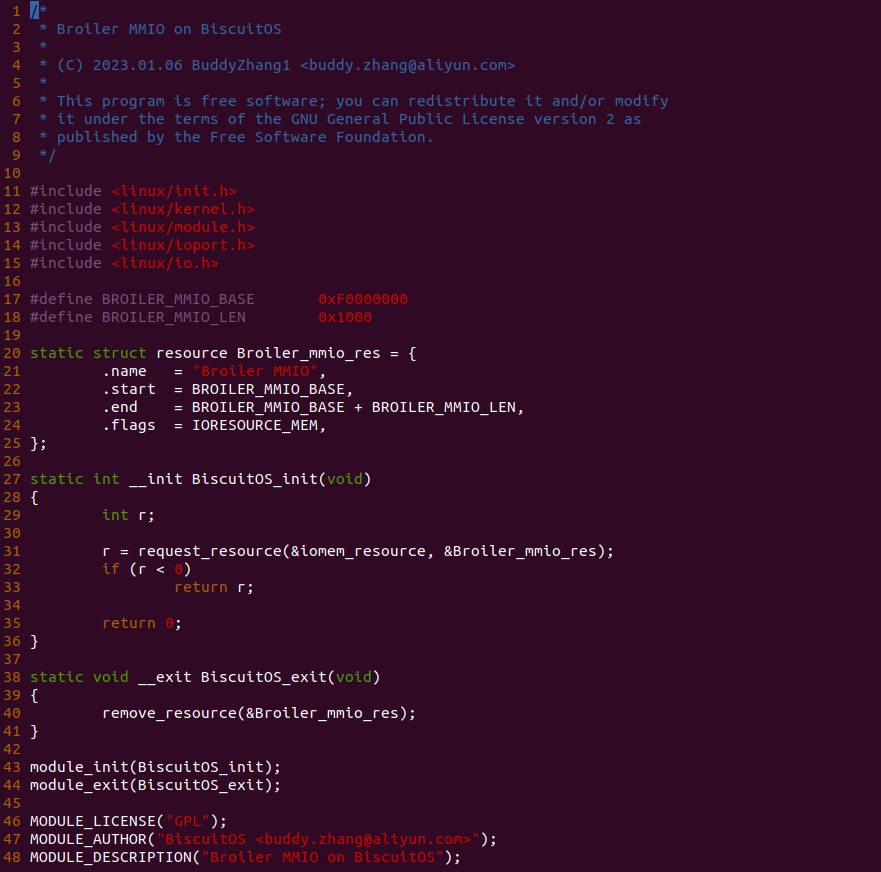

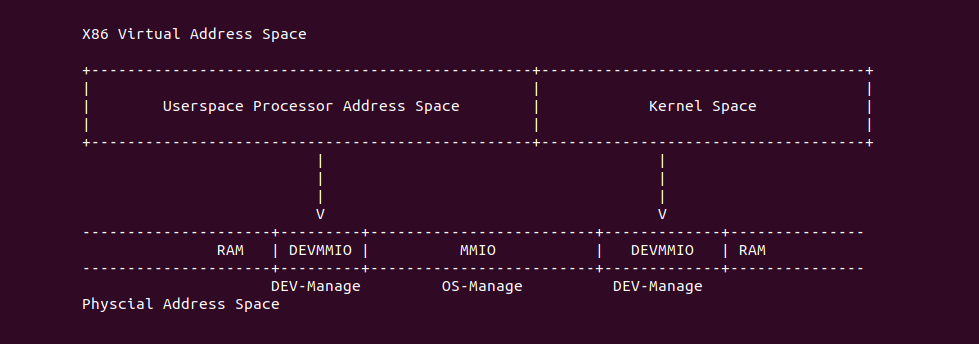

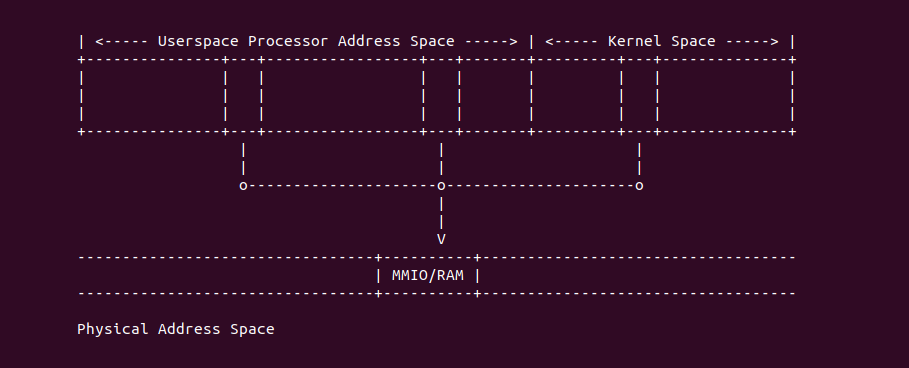

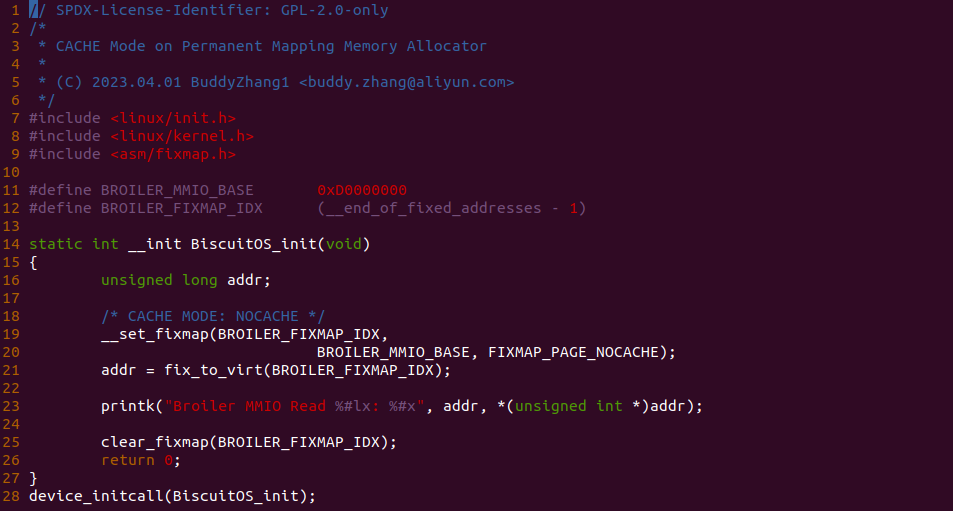

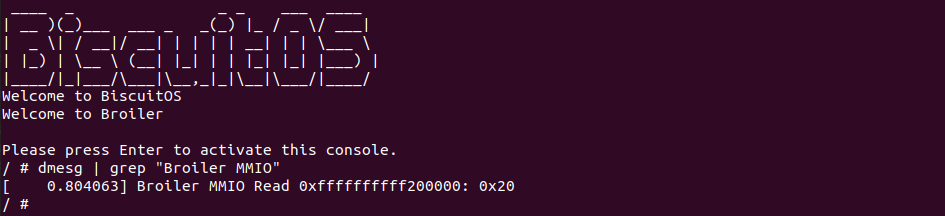

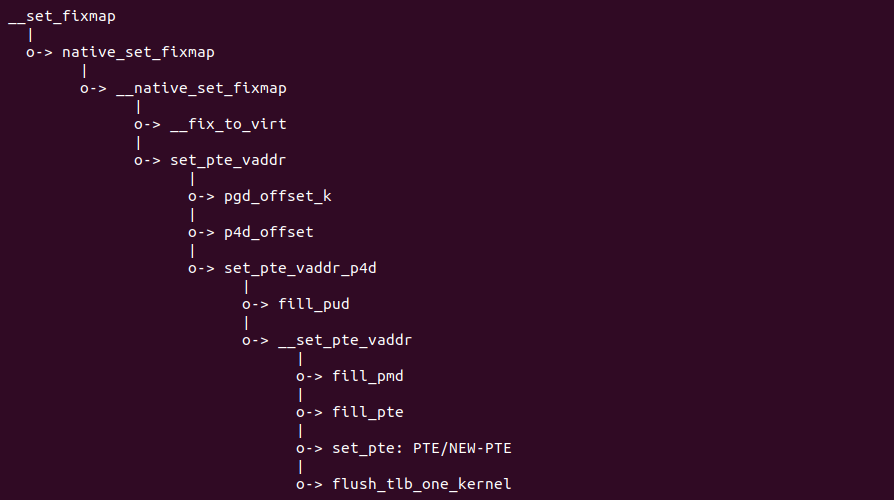

Strong Uncacheable (UC): 强非缓存类型,该类型的物理内存不使用任何缓存机制. 系统对该类型的物理内存的读写请求会直接发送到总线上,另外硬件上不会对该类型物理内存的访问和对应页表遍历预测功能,同样也不会对分支进行预测. UC 缓存类型通常用于映射外设的 MMIO,因为外设不具有监听(snoop)总线的能力,为了保持设备看物理区域与 CPU 看到的一致,因此将该物理区域设置为 UC 之后,CPU 对该区域的读写请求直接访问到物理地址上,不会缓存在 CACHE 里,因此可以保持设备和 CPU 看到数据的一致性. 不建议将普通的物理内存的缓存类型设置为 UC,这样会 CPU 每次都对物理内存进行访问,这会大大影响系统性能. 接下来通过一个实践案例介绍内核如何将一段 MMIO 区域的缓存类型设置为 UC, 其在 BiscuitOS 上的部署逻辑如下:

内核空间虚拟地址映射 UC MMIO

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support BiscuitOS Hardware Emulate

[*] CACHE --->

[*] UNCACHE(UC): Mapping UC MMIO on Kernel --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-UNCACHE-MMIO-KERNEL-default

# 部署源码

make download

# 在 BiscuitOS/Broiler 中实践

make broilerBiscuitOS-CACHE-UNCACHE-MMIO-KERNEL-default Source Code on Gitee

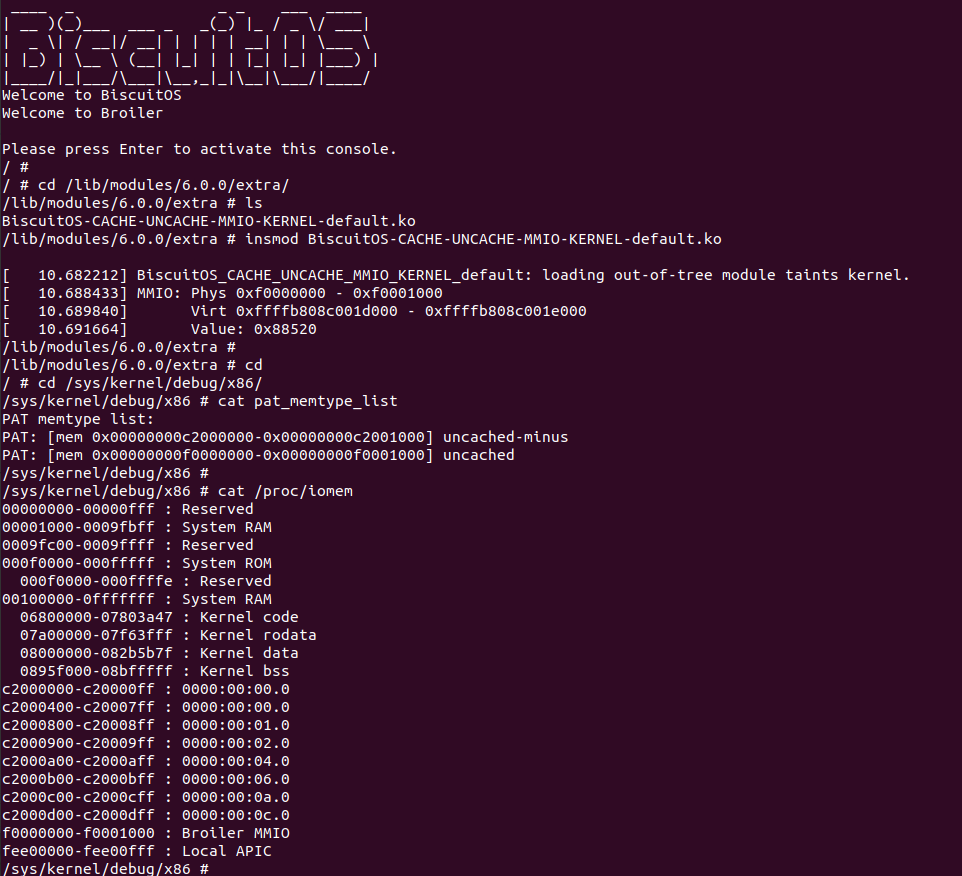

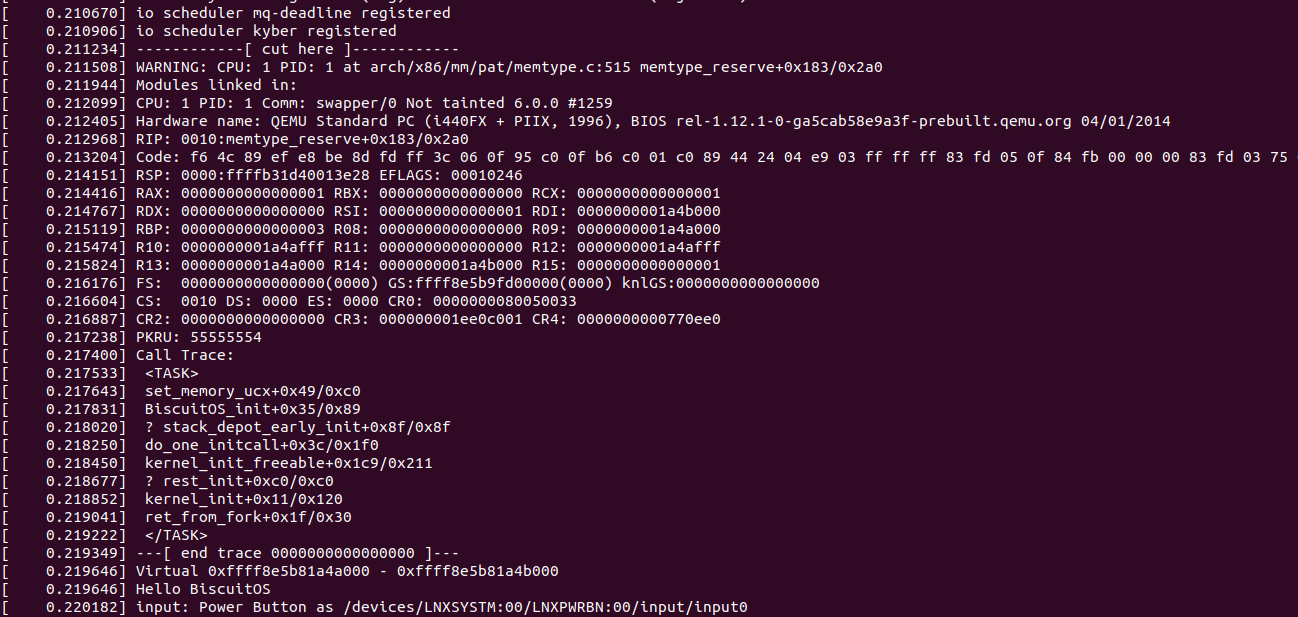

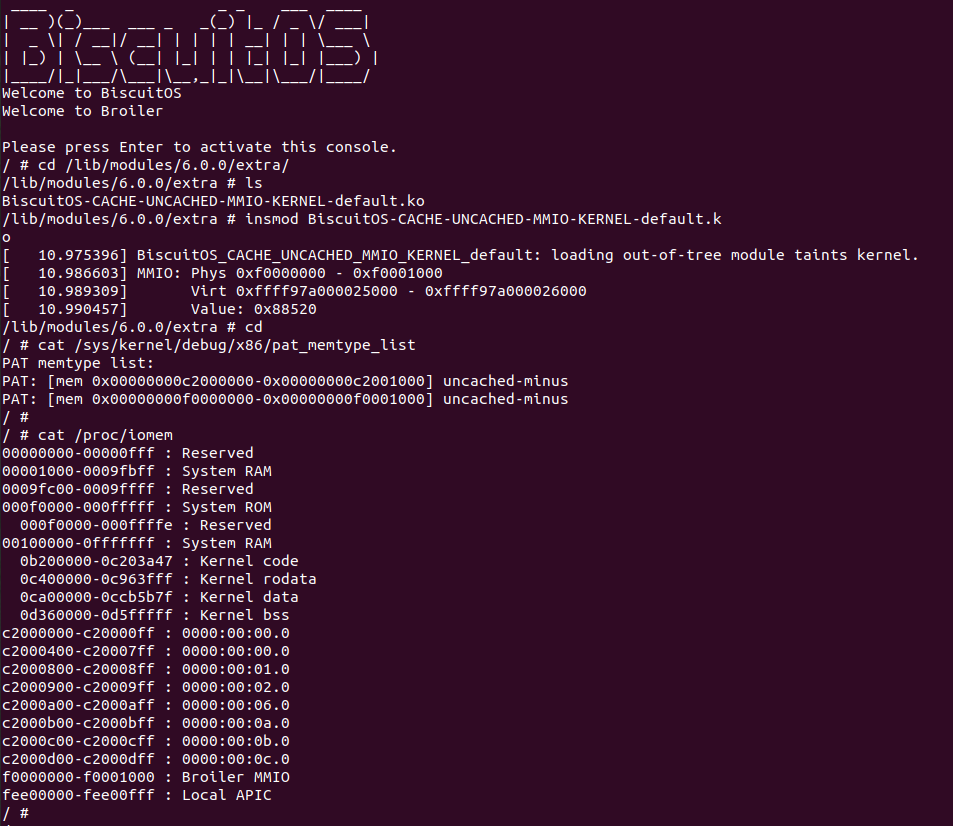

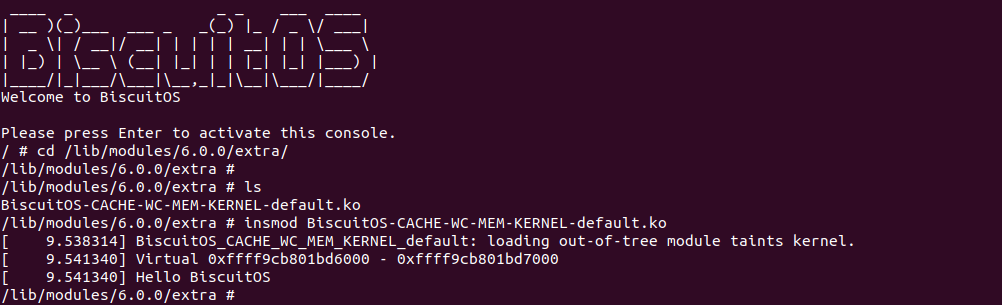

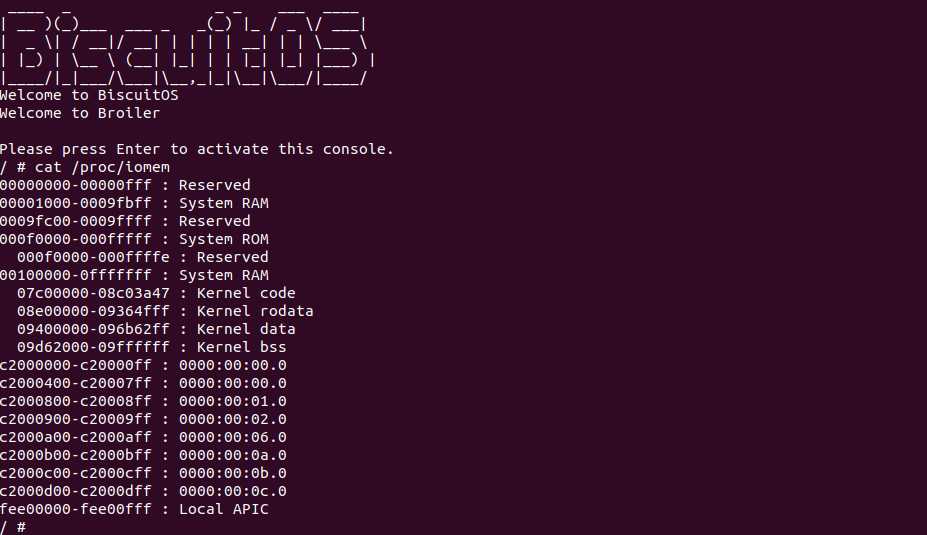

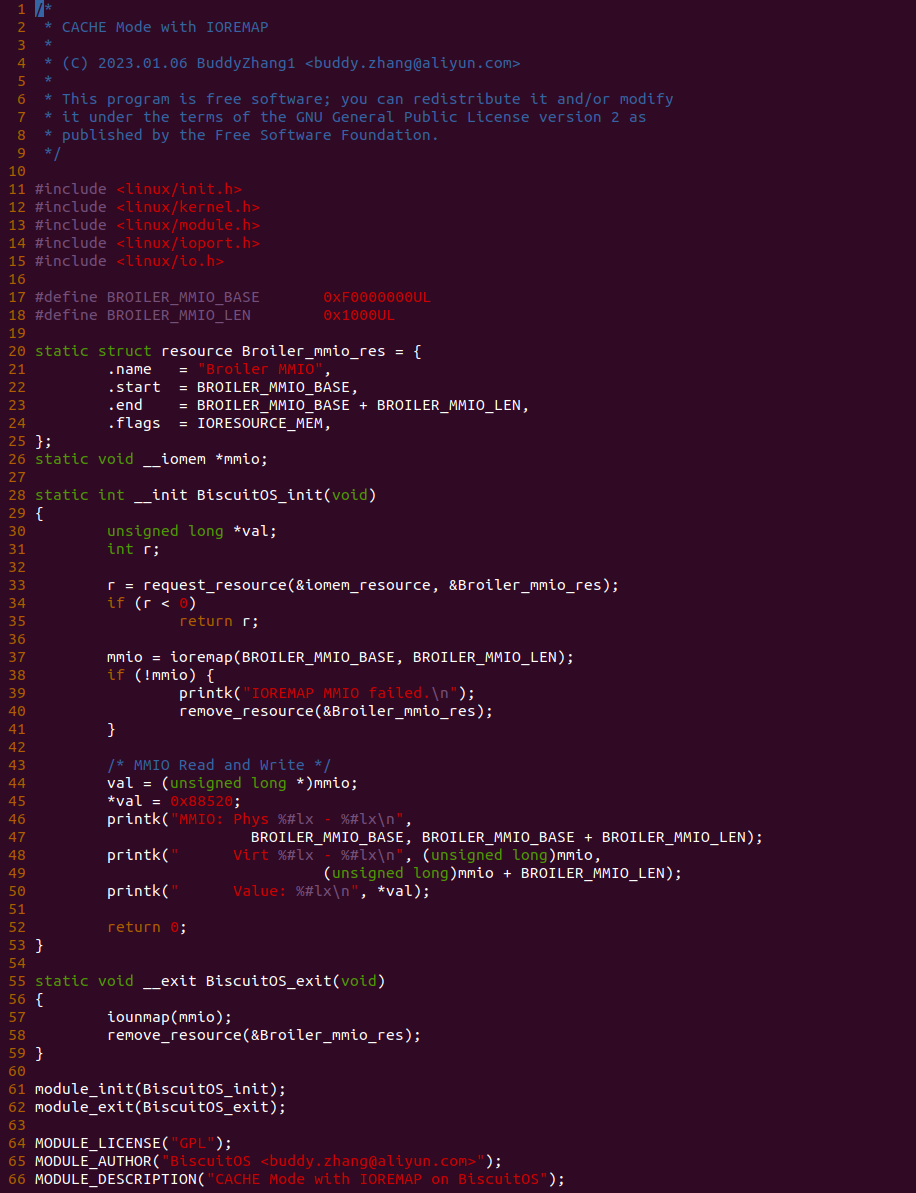

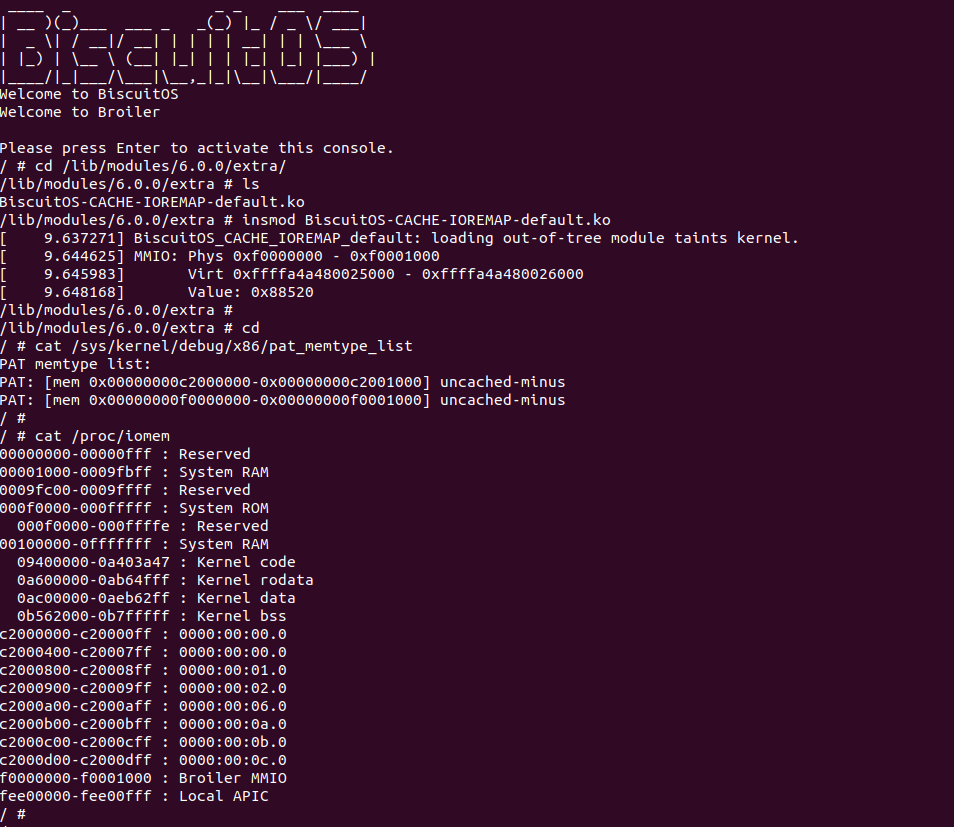

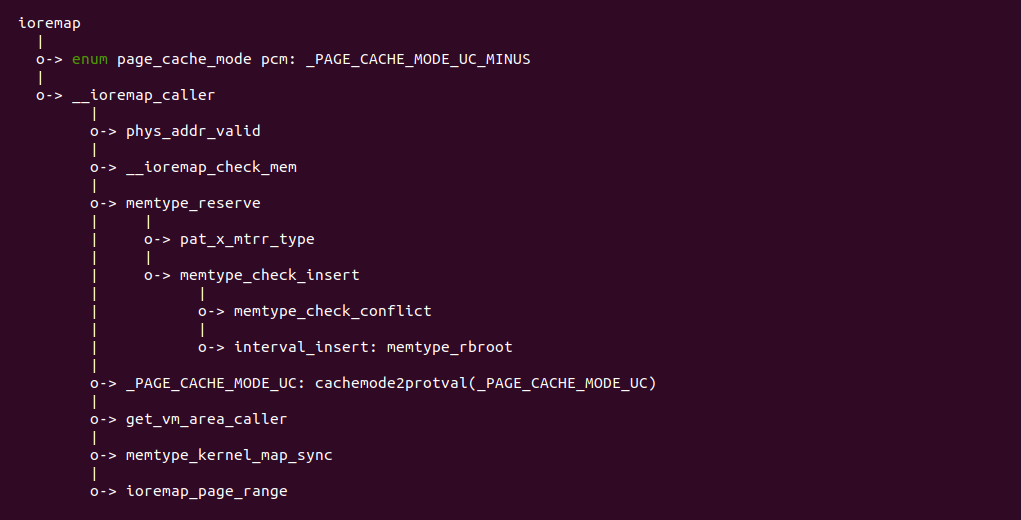

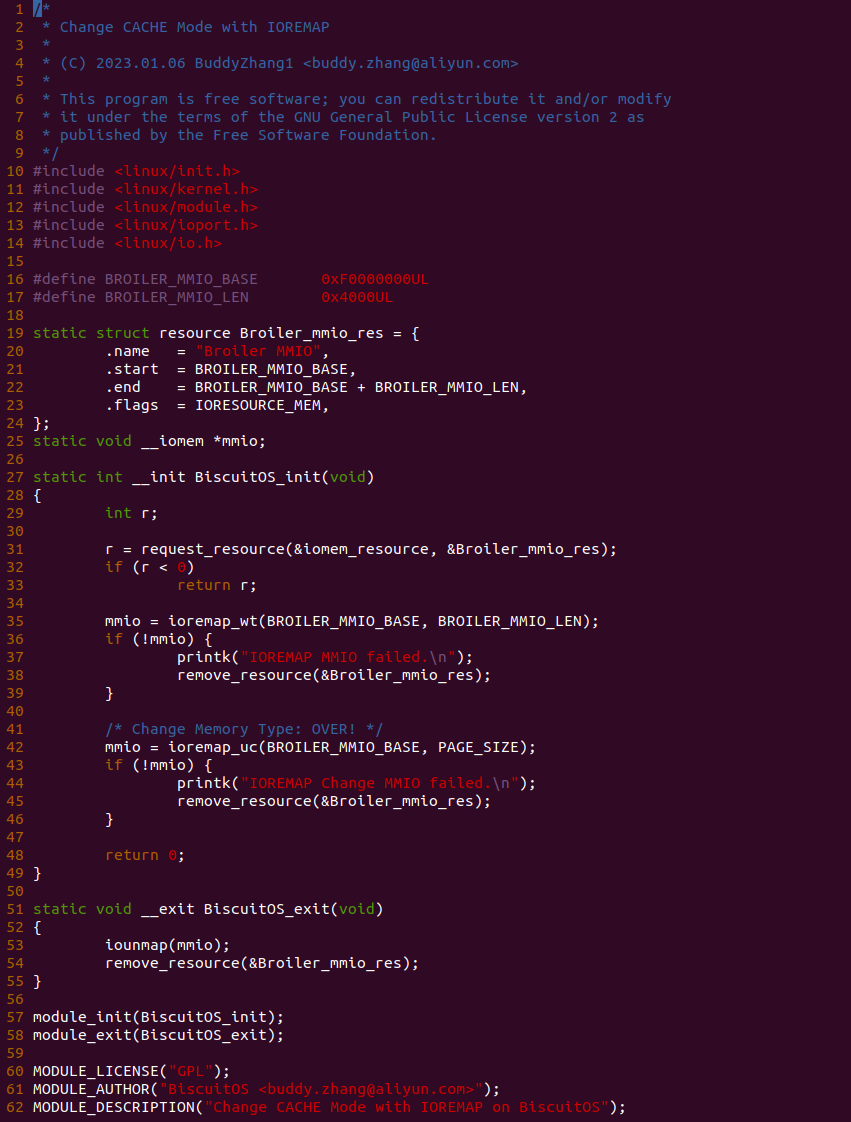

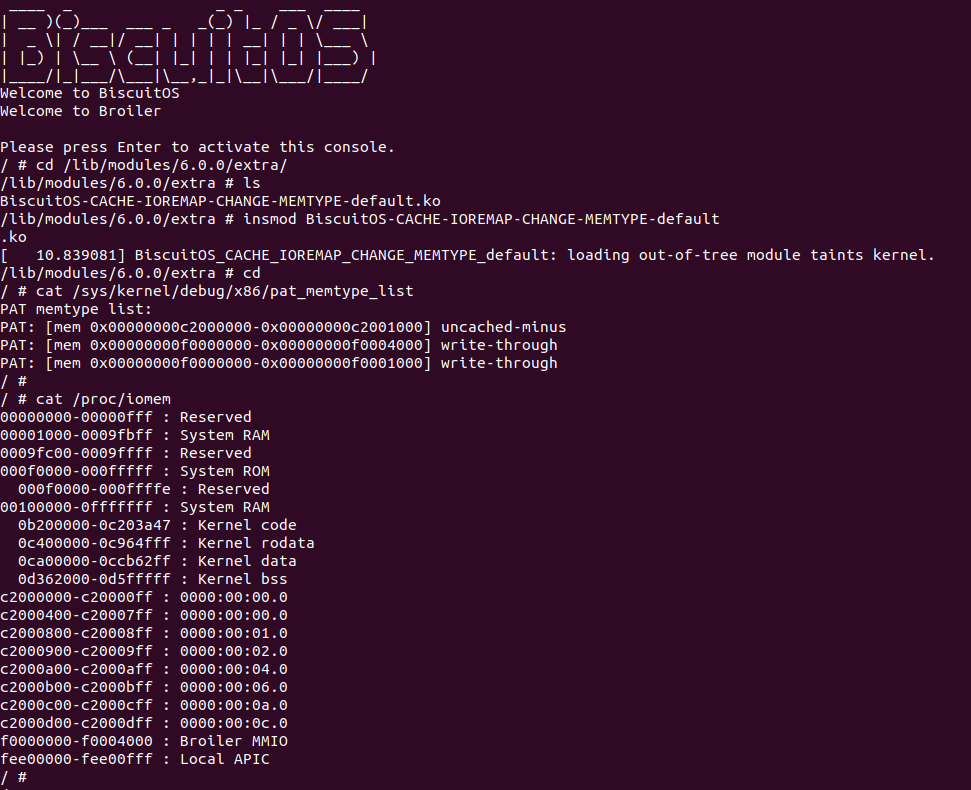

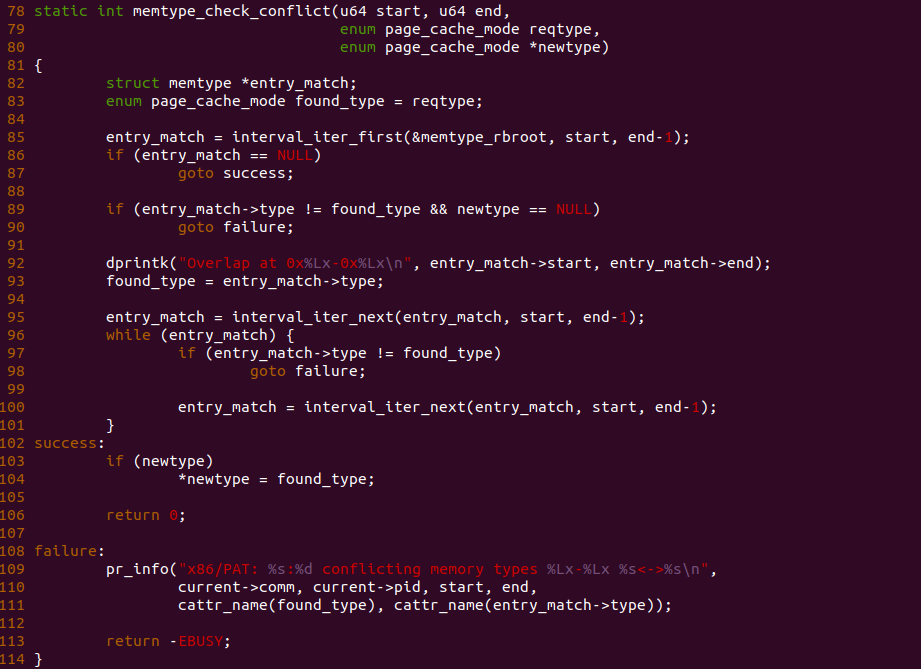

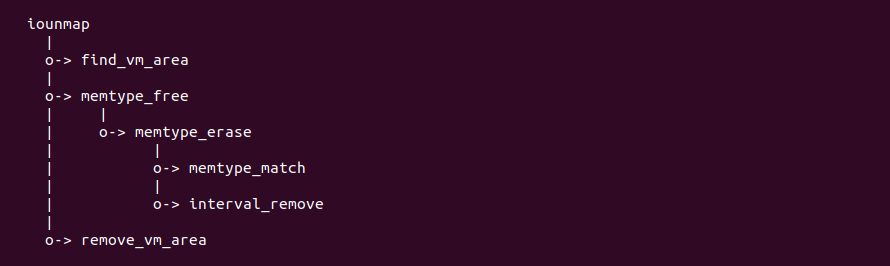

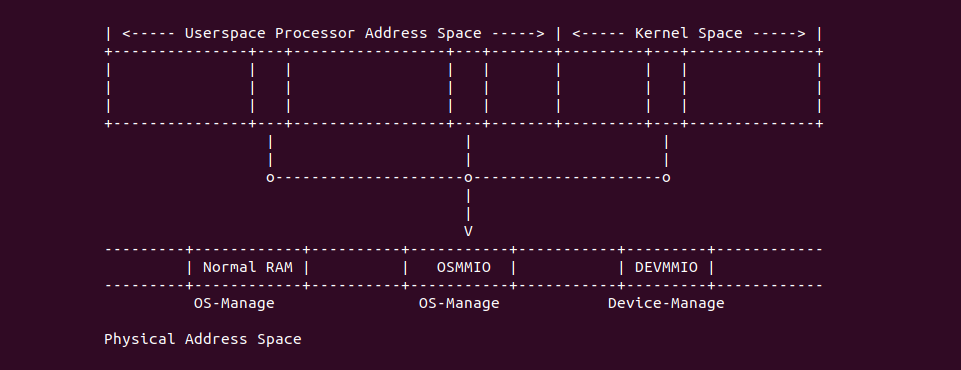

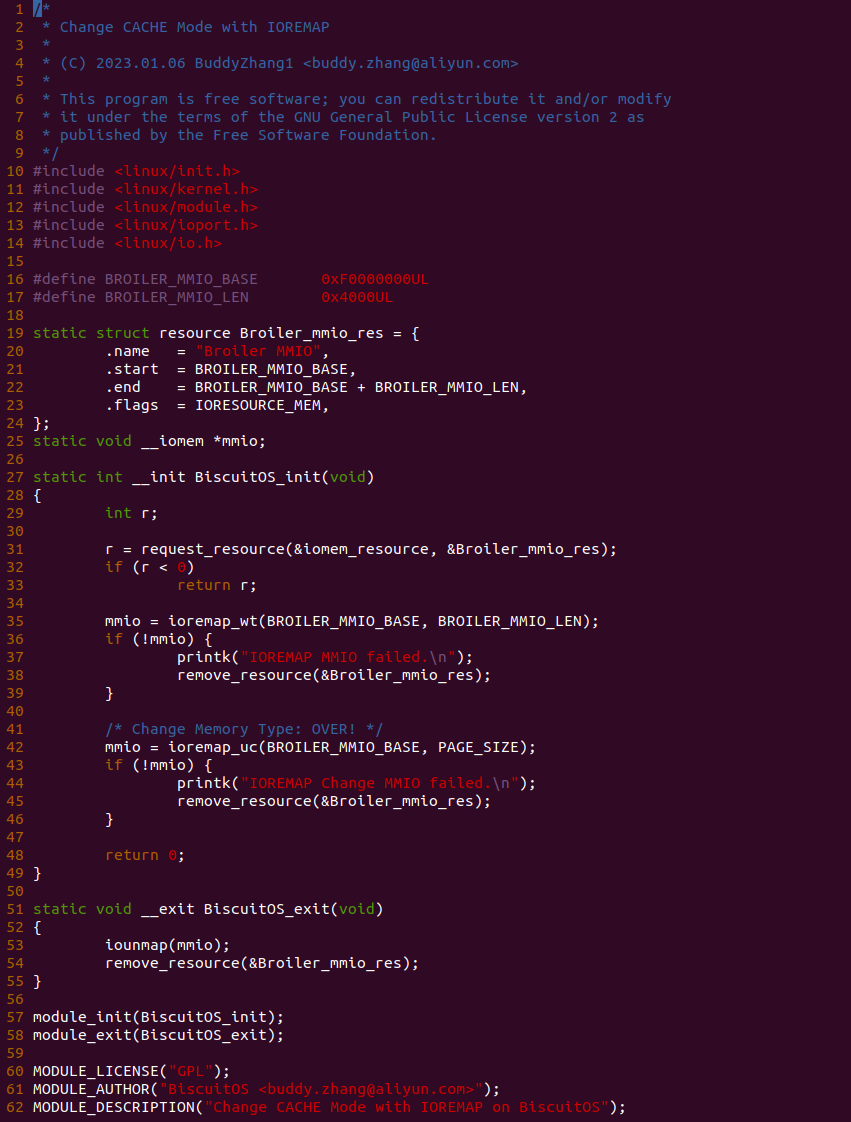

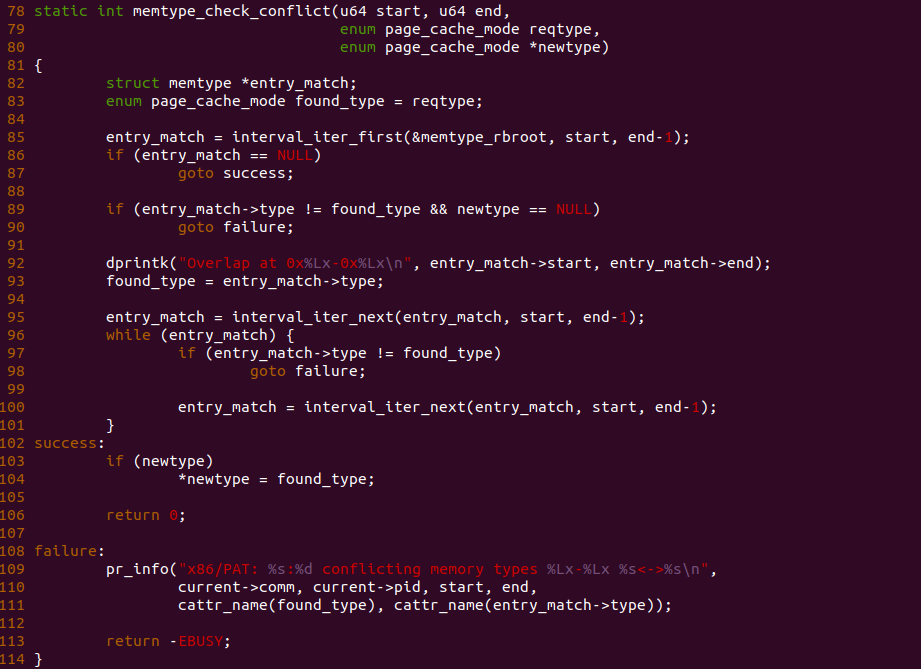

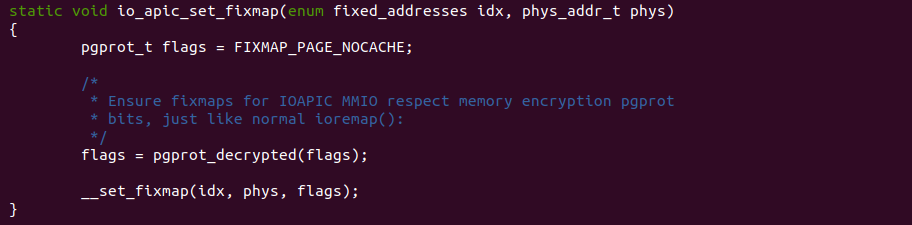

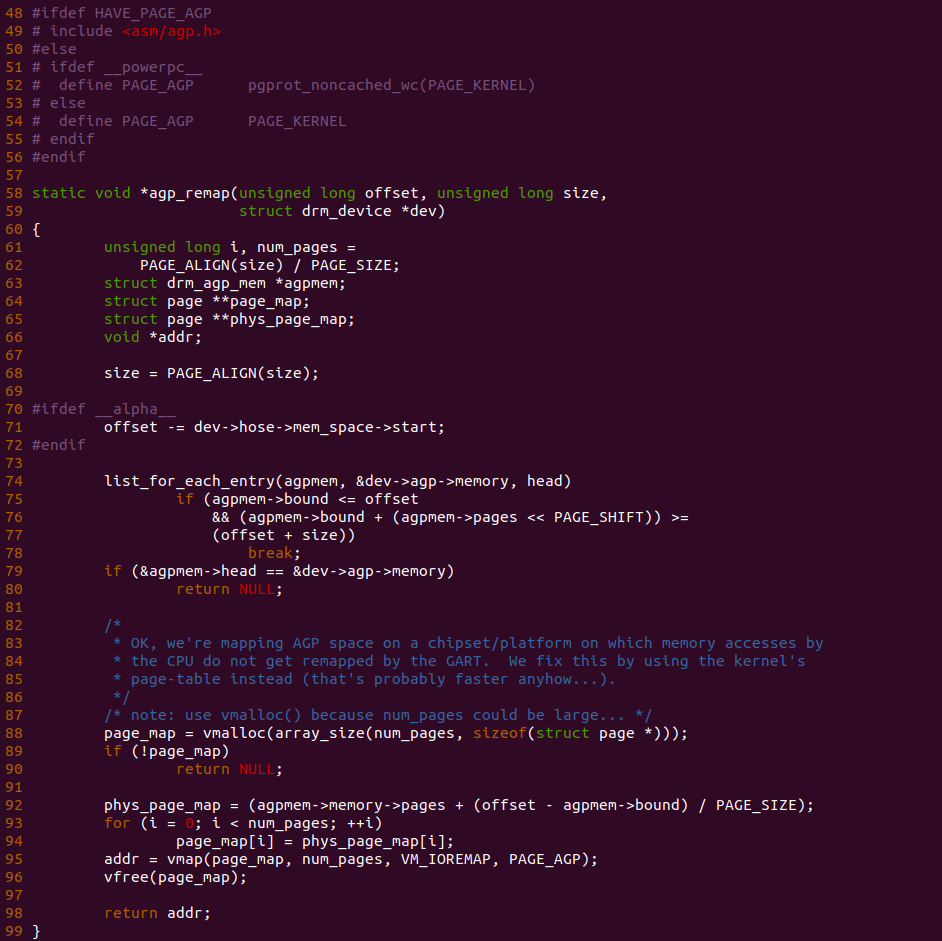

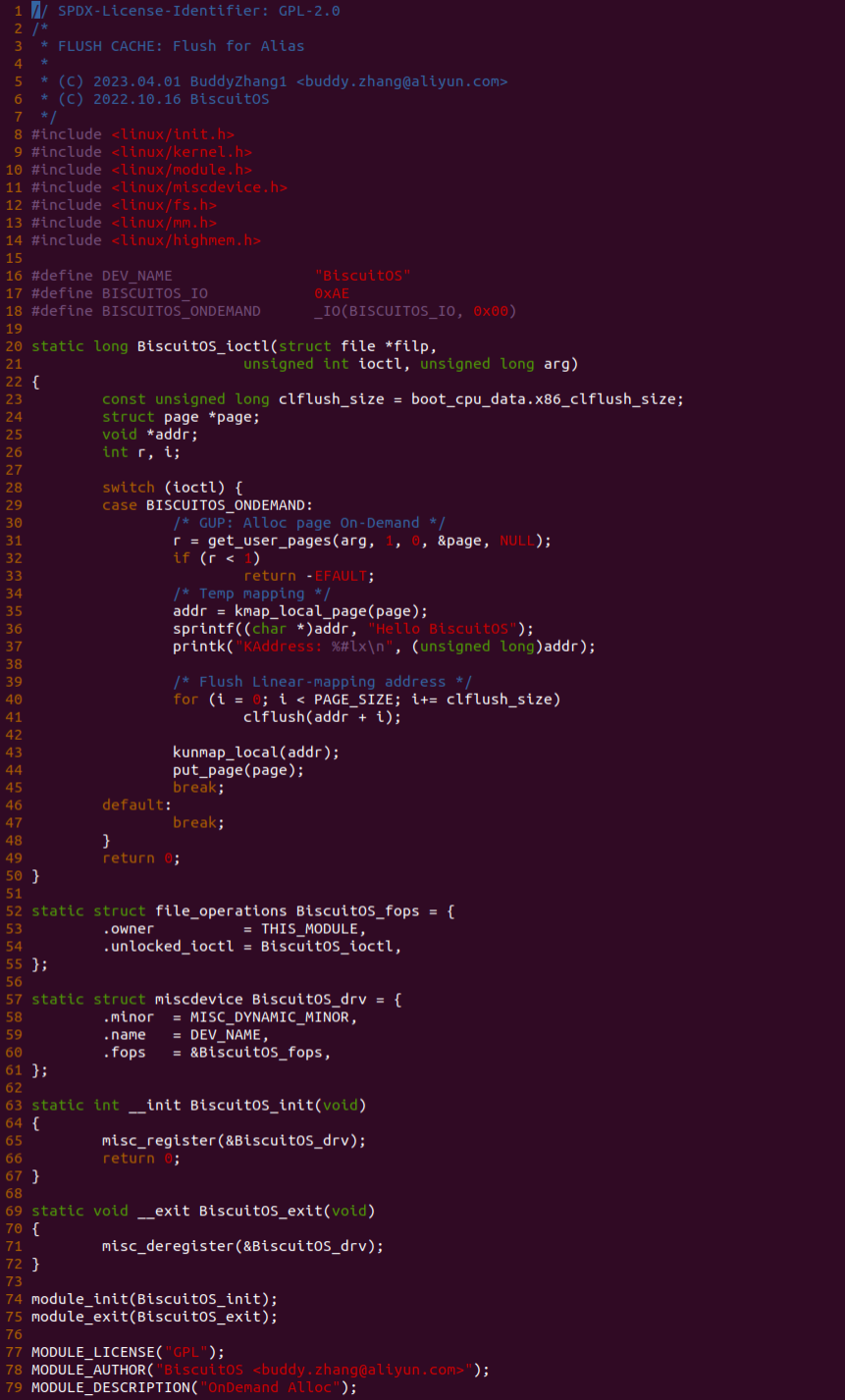

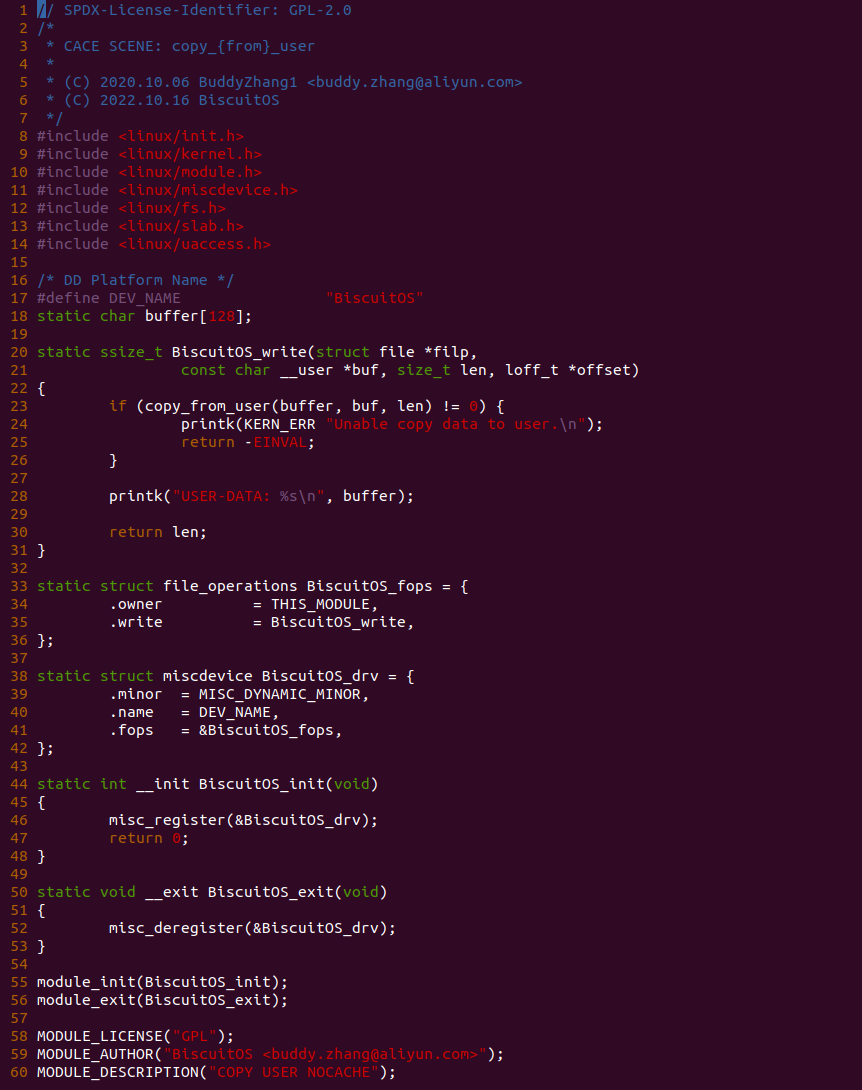

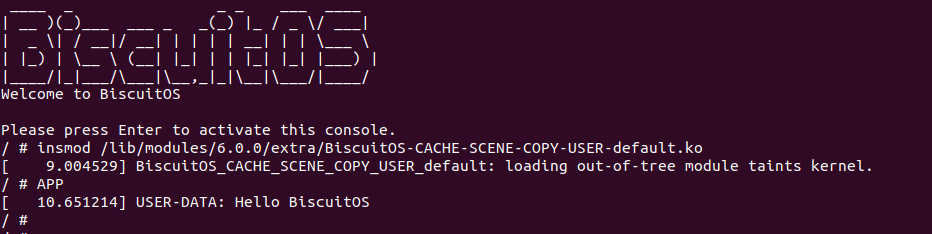

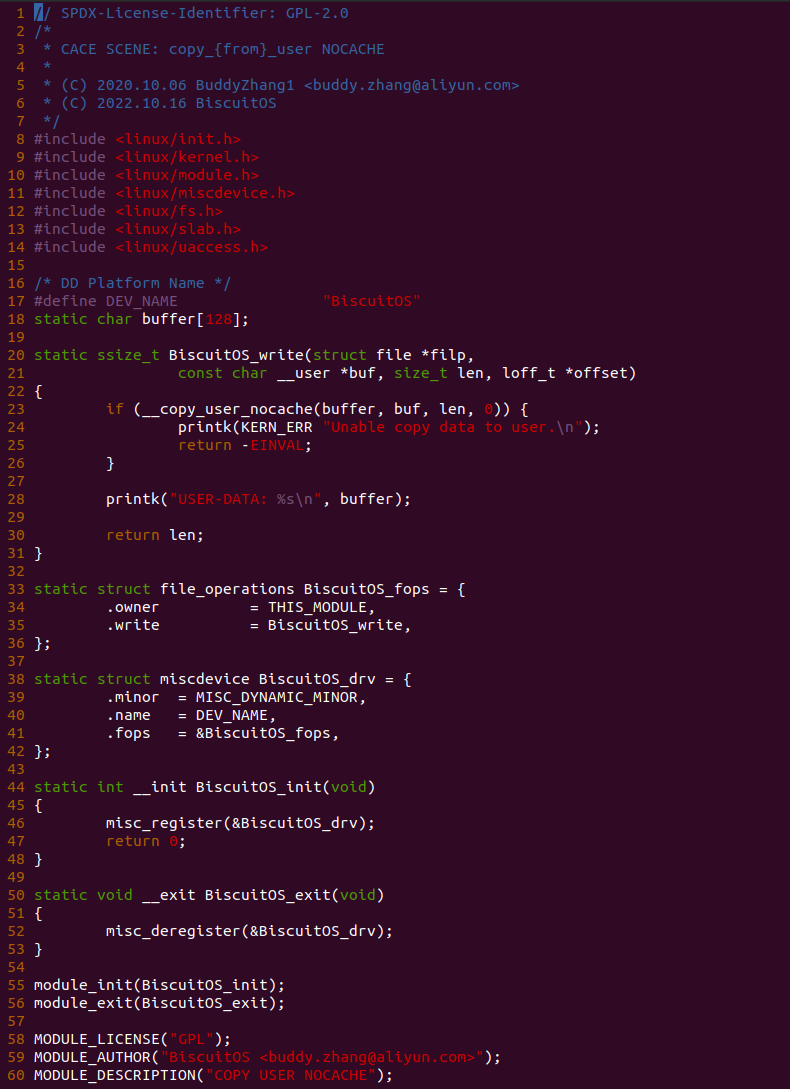

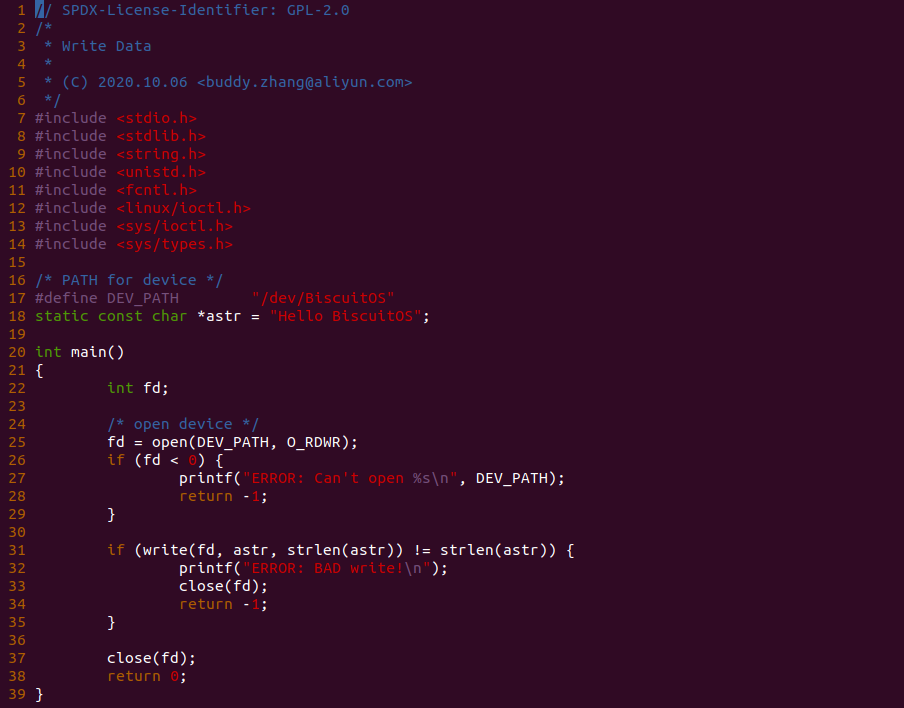

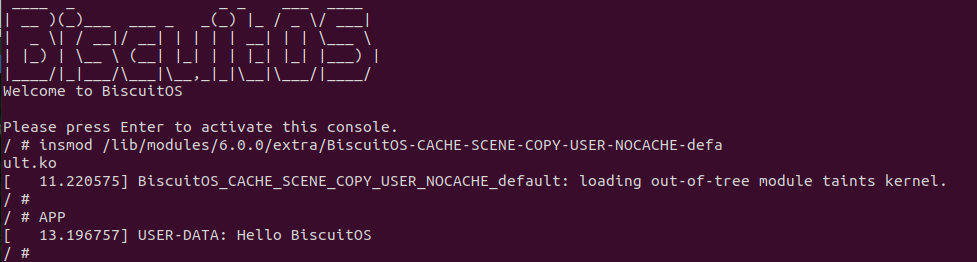

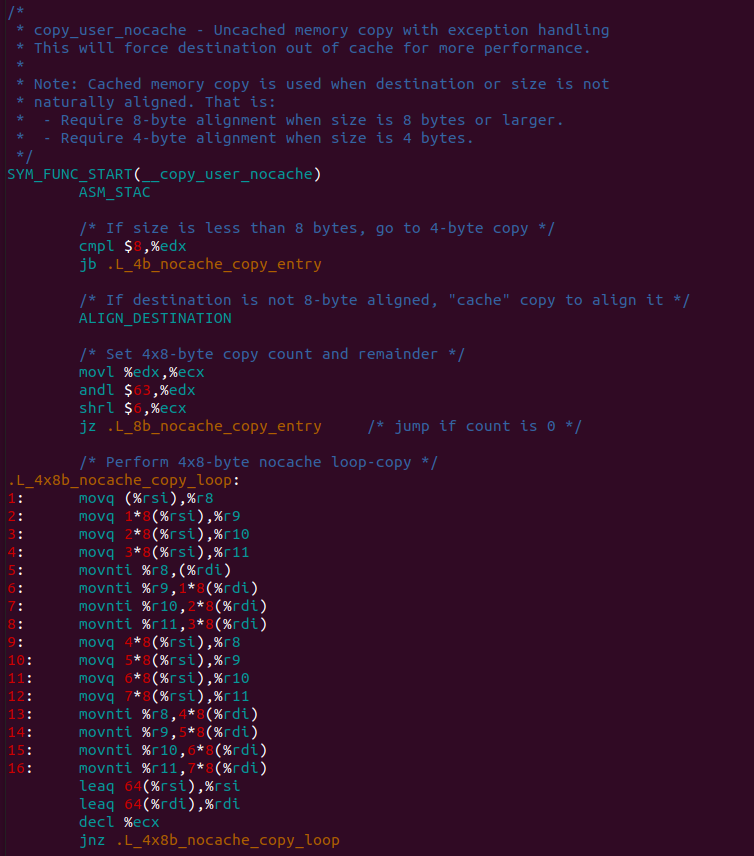

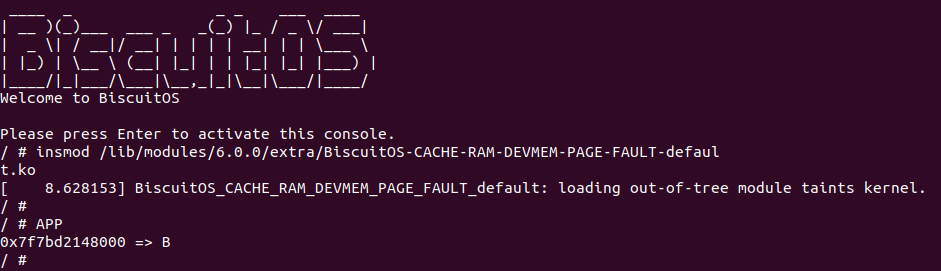

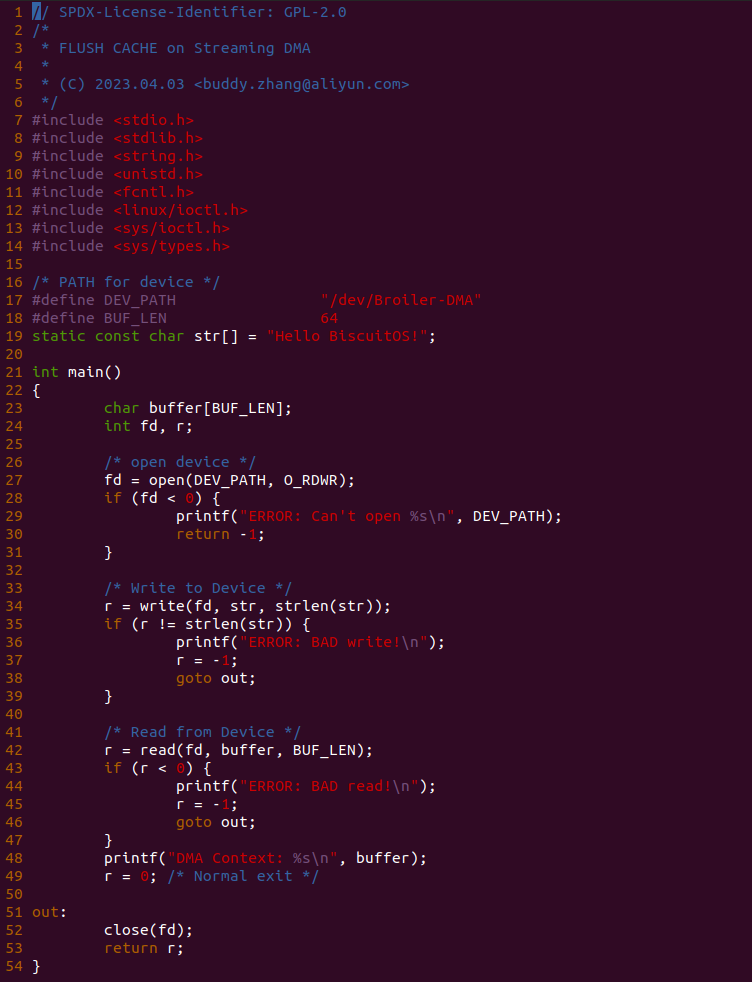

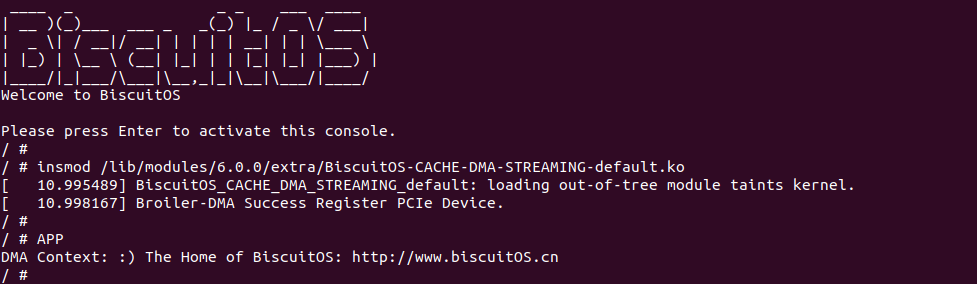

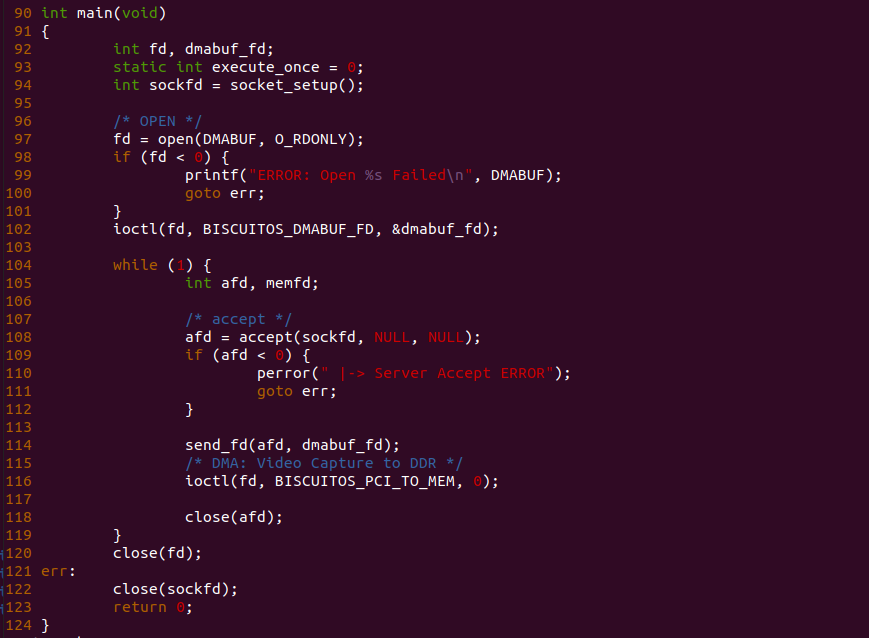

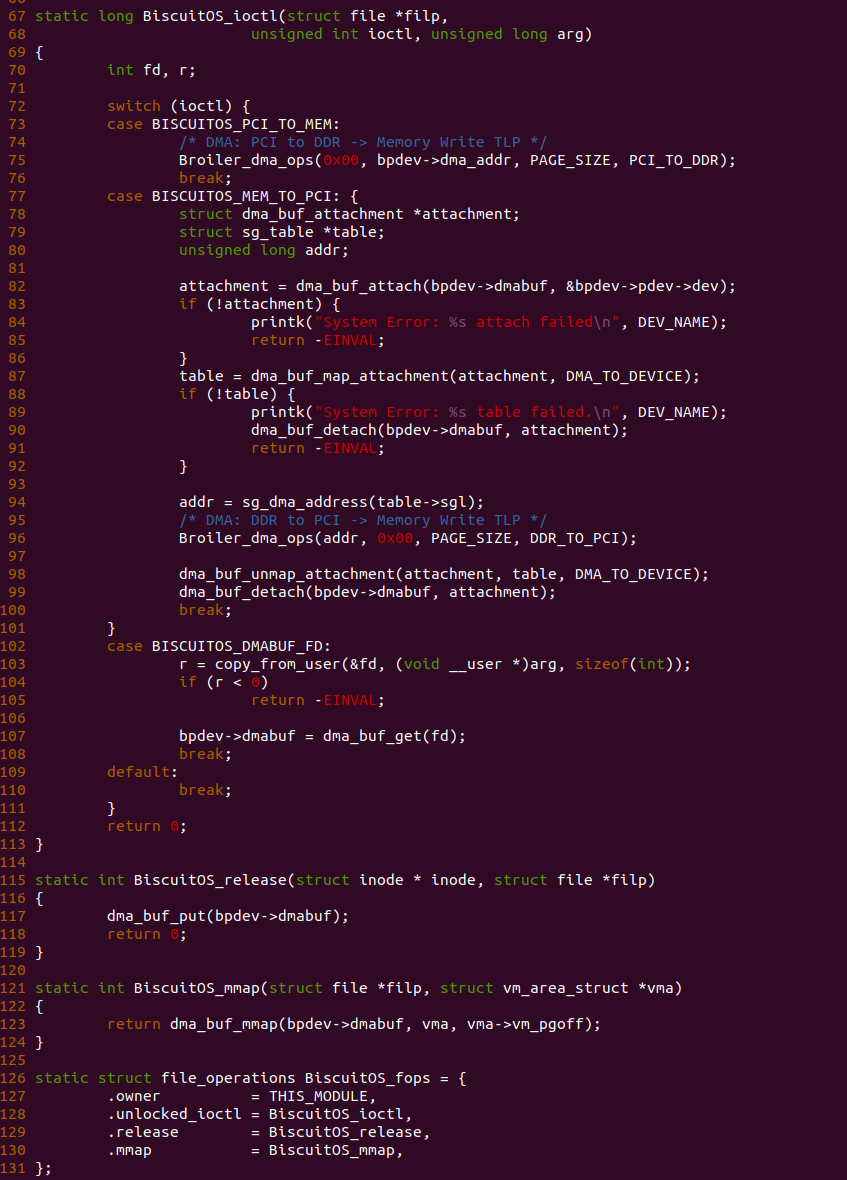

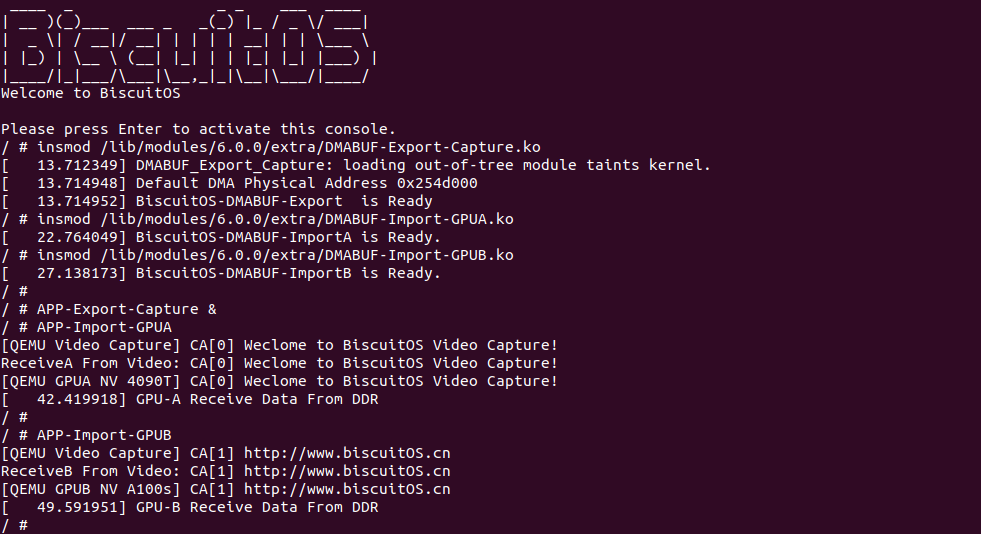

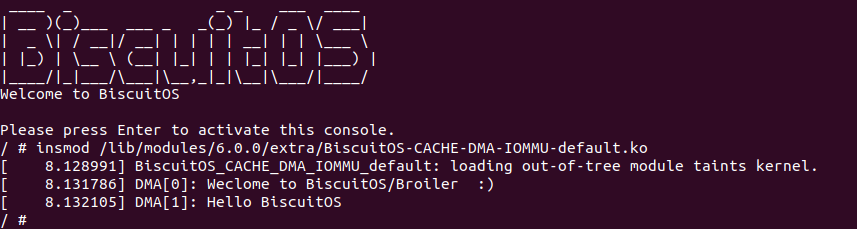

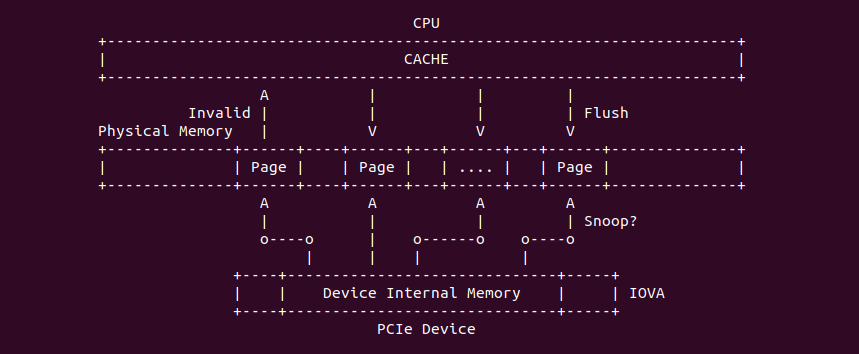

源码通过一个内核模块进行展示,模块有两部分组成,第一部分是 20-35 行,模块向系统资源总线注册了一段 MMIO,这段 MMIO 起始物理地址是 BROILER_MMIO_BASE, 长度为 BROILER_MMIO_LEN, 注册完毕之后可以在系统启动之后,通过 ‘/proc/iomem’ 接口查看到该段信息; 第二部分是 38-46 行,模块在 38 行调用 ioremap_uc() 函数将 BROILER_MMIO_BASE 开始且长度为 BROILER_MMIO_LEN 的 MMIO 区域,映射为 Uncached 的 memory type, 映射完毕之后函数在 46 行对 MMIO 进行访问,此时并不会触发缺页,因为 ioremap_uc() 函数已为 MMIO 分配了对应的虚拟地址并建立了页表,因此模块可以直接访问 MMIO. 最后在 BiscuitOS 上实践模块,由于需要一段真实的 MMIO 才能运行模块,因此可使用 Broiler 模拟一段 MMIO,其起始物理地址为 0xF0000000(Broiler 已经模拟好硬件),开发者直接在源码目录执行 make broiler 即可:

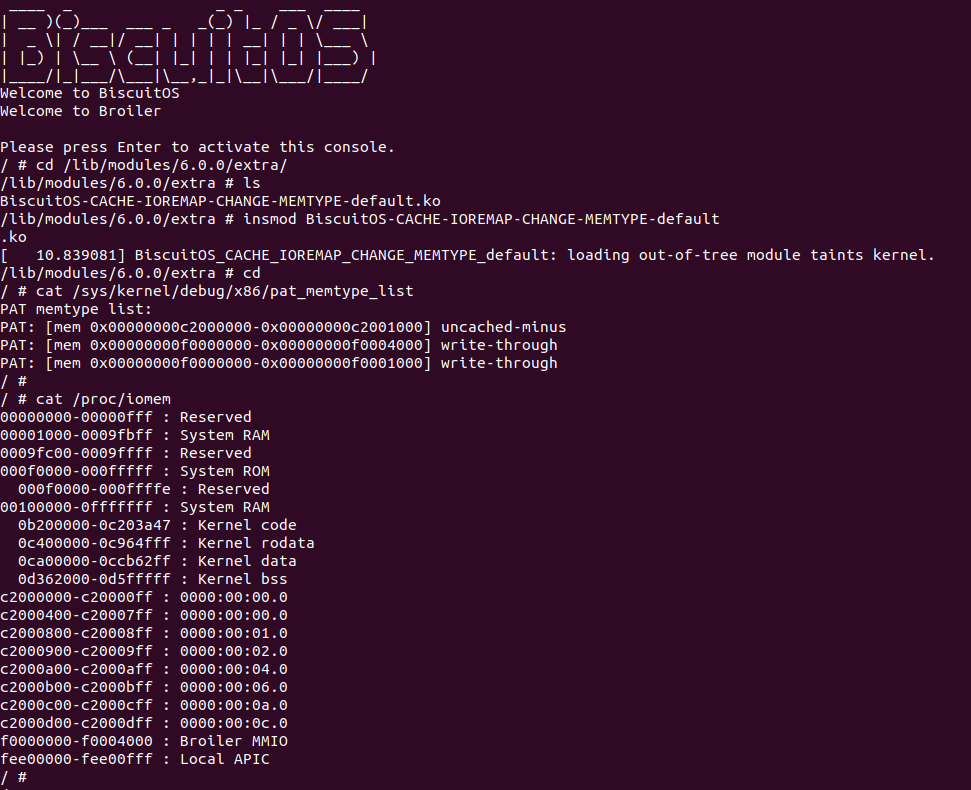

BiscuitOS 运行之后,加载 BiscuitOS-CACHE-UNCACHE-MMIO-KERNEL-default.ko 模块之后,从打印的内核信息可以看出模块已经映射了 MMIO,并且向 MMIO 写入 0x88520 之后可以读出正确的数据,最后查看 ‘/sys/kernel/debug/x86/pat_memtype_list’ 节点查看系统 MMIO memory_type 信息,可以看到模块映射的 MMIO [0xF0000000, 0xF0001000] 为 uncached, 另外查看 ‘/proc/iomem’ 节点查看物理地址空间信息,可以看到 [0xF0000000, 0xF0001000) 为 Broiler MMIO 区域, 实践符合预期. 接下来一个实践案例用于介绍如何将用户空间虚拟地址映射成 UC 的 MMIO,BiscuitOS 部署逻辑如下:

用户空间虚拟地址映射 UC MMIO

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support BiscuitOS Hardware Emulate

[*] CACHE --->

[*] UNCACHE(UC): Mapping UC MMIO on Userspace --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-UNCACHE-MMIO-USERSPACE-default

# 部署源码

make download

# 在 BiscuitOS/Broiler 中实践

make broilerBiscuitOS-CACHE-UNCACHE-MMIO-USERSPACE-default Source Code on Gitee

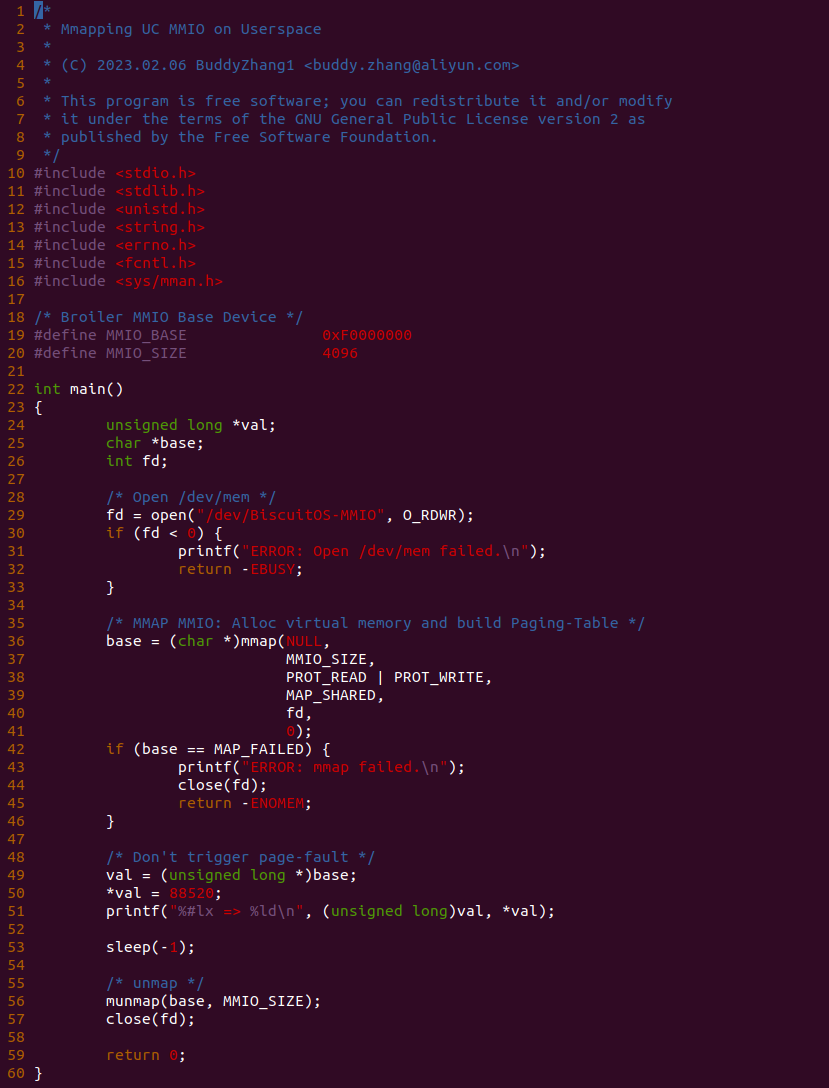

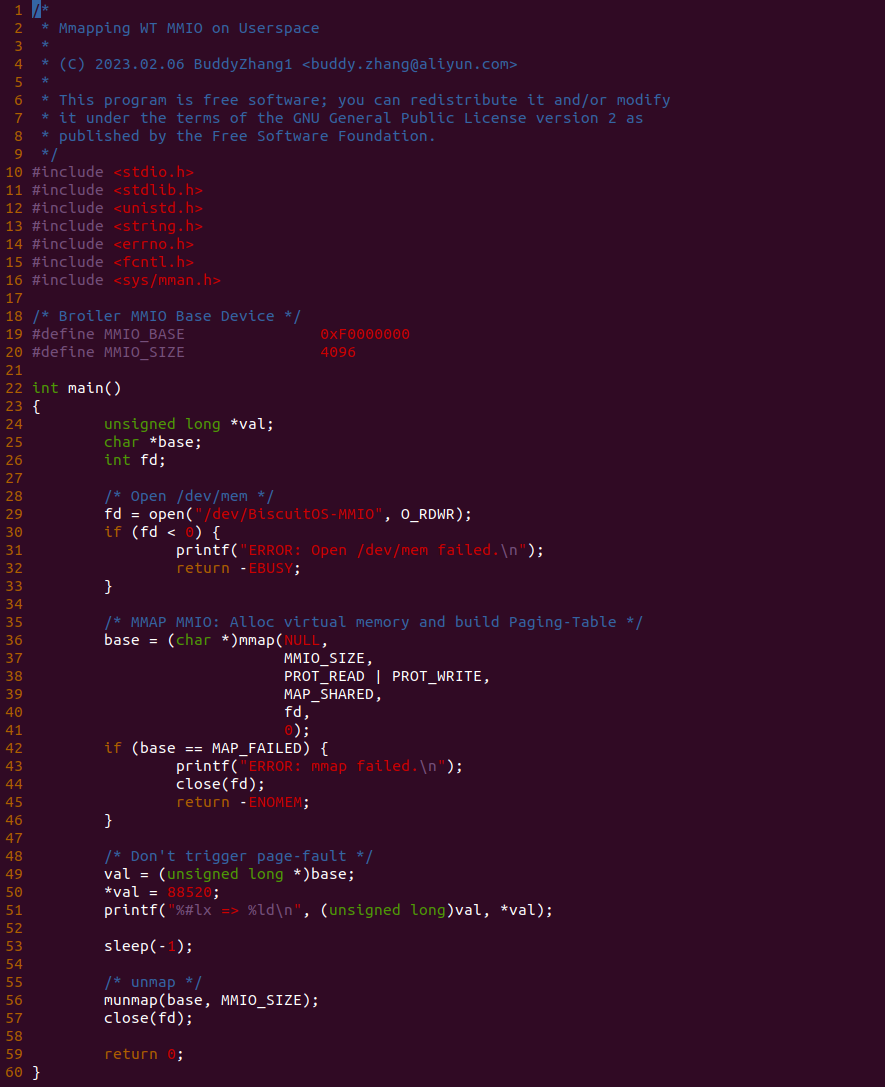

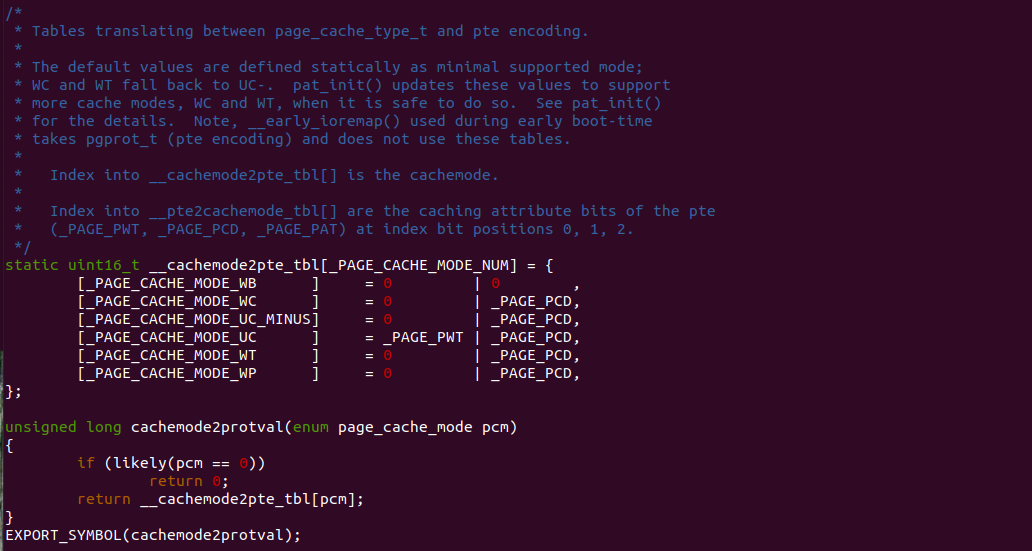

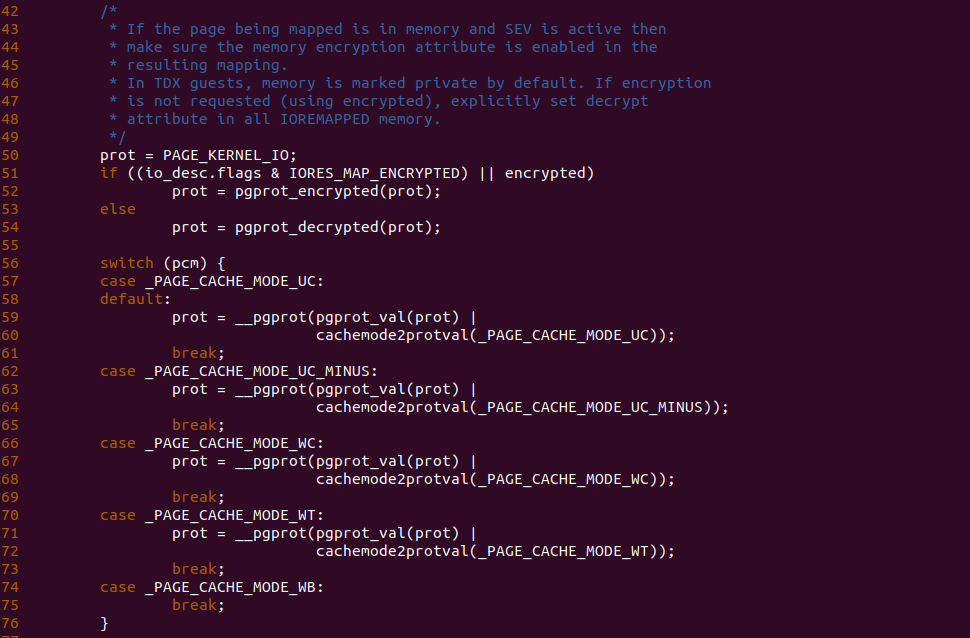

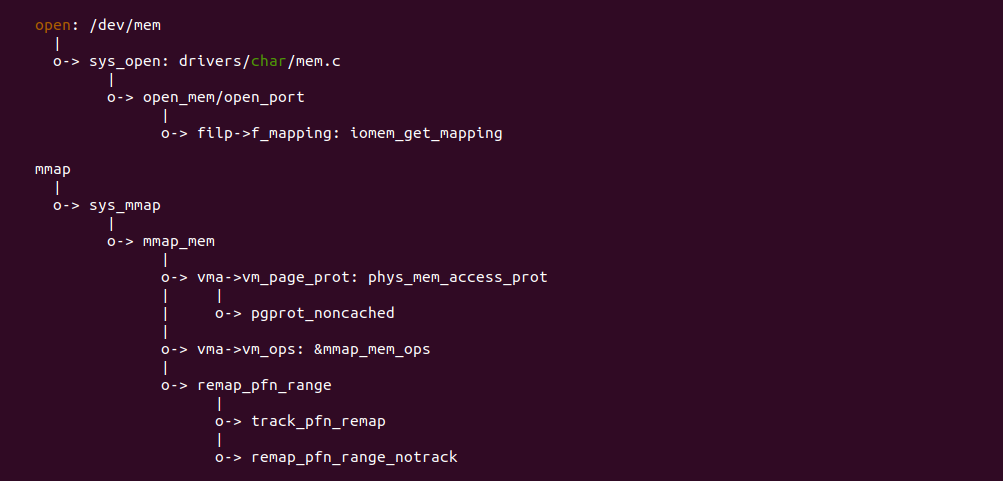

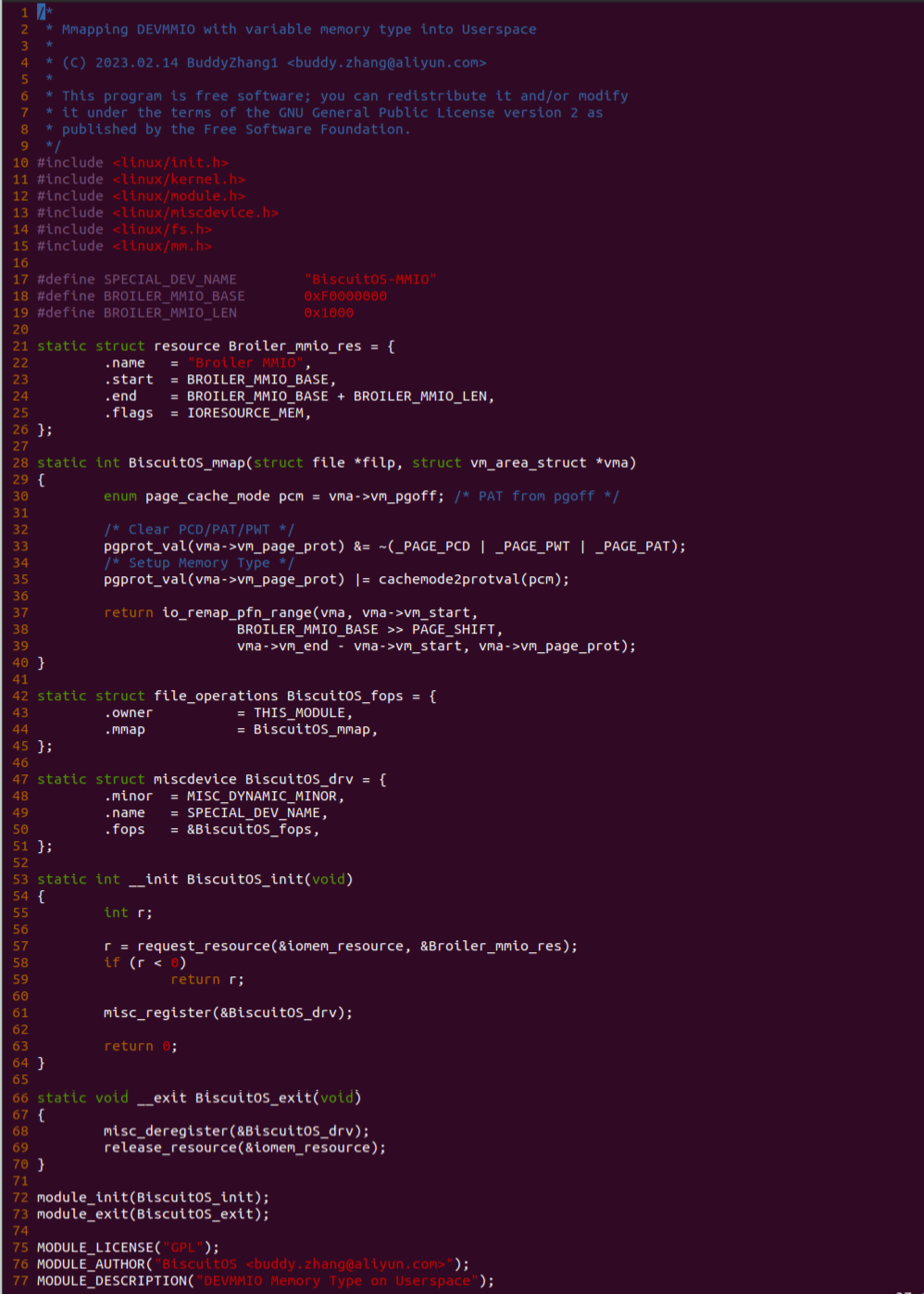

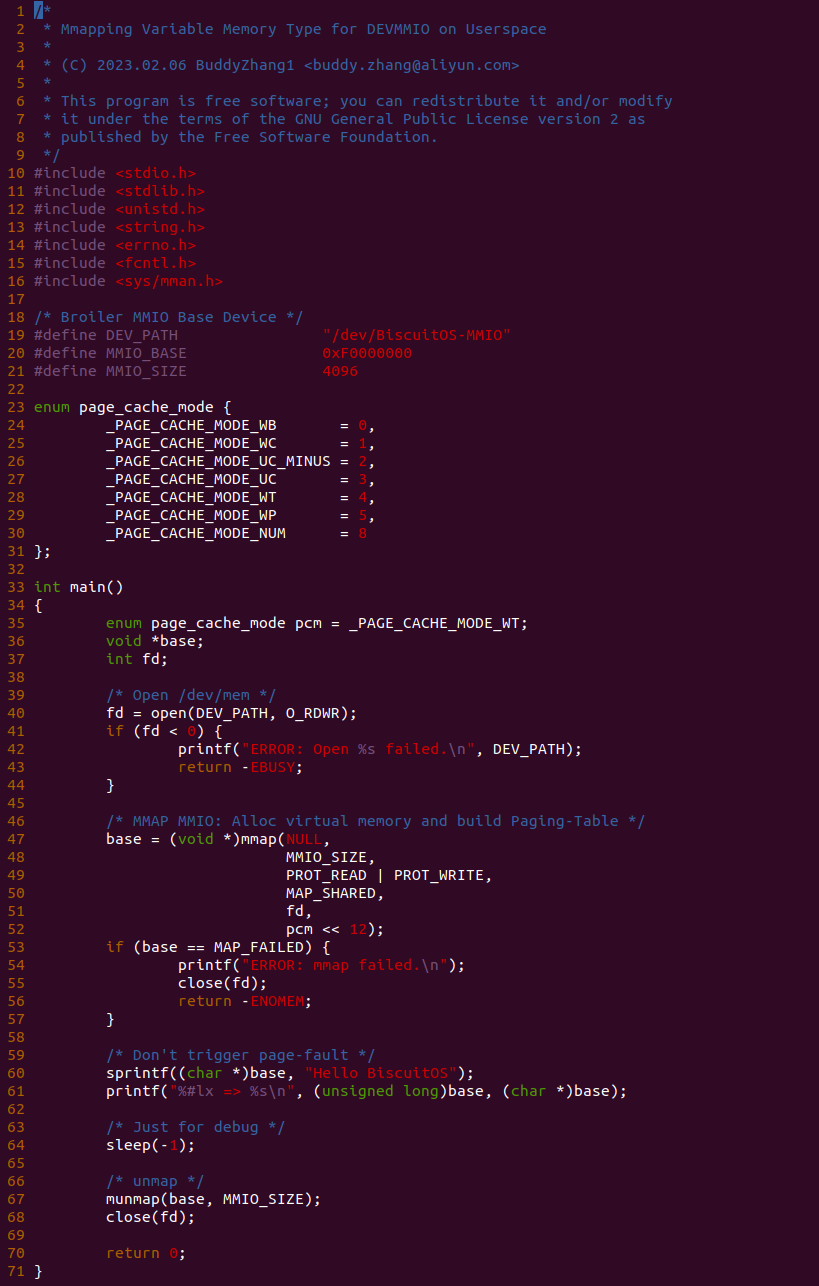

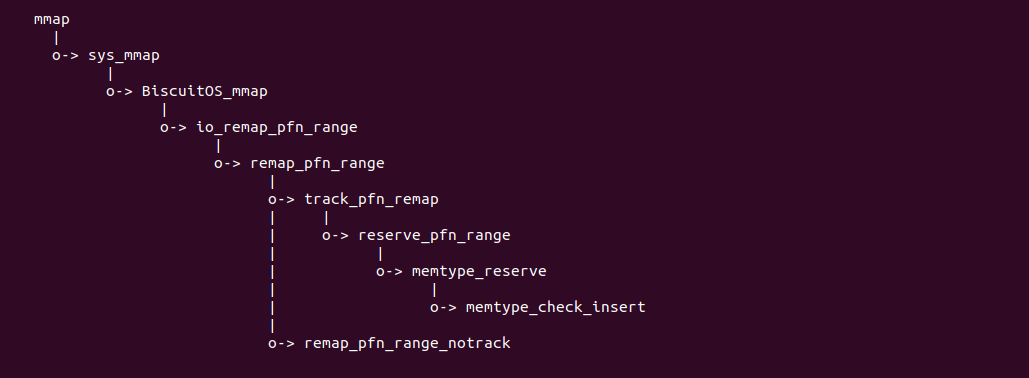

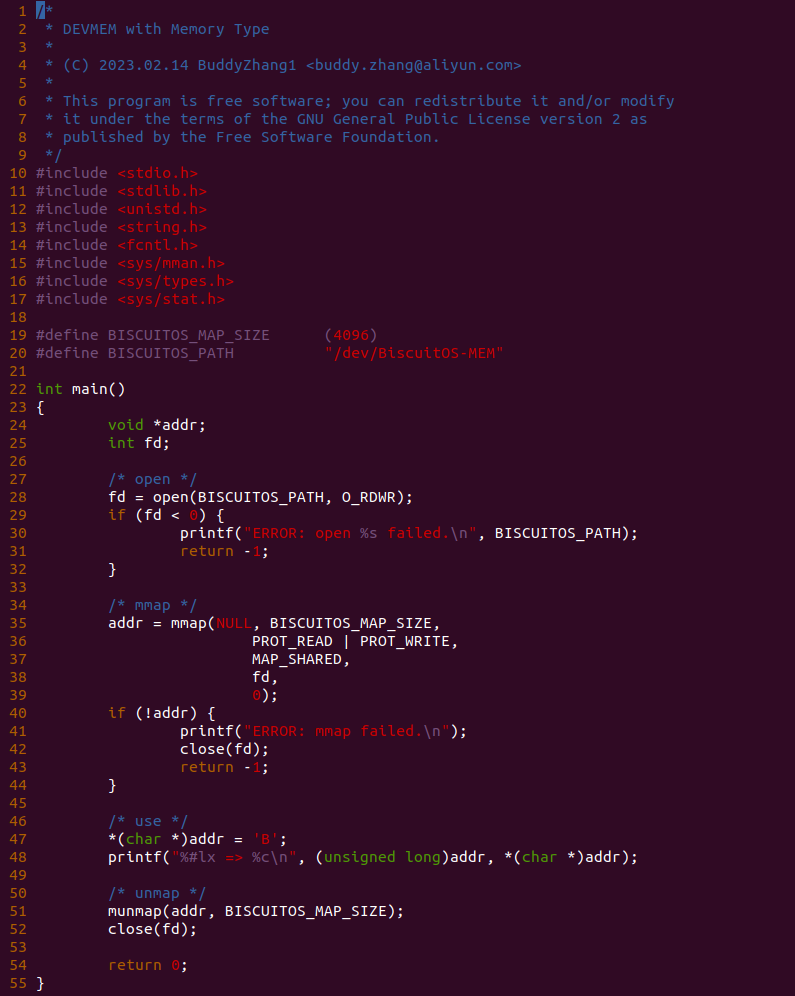

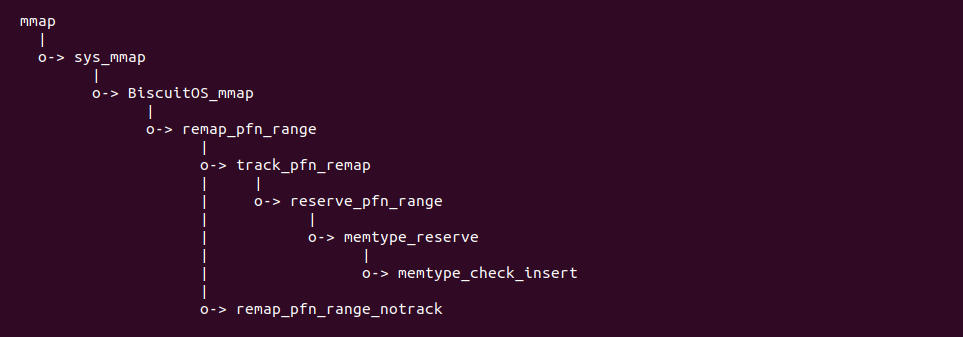

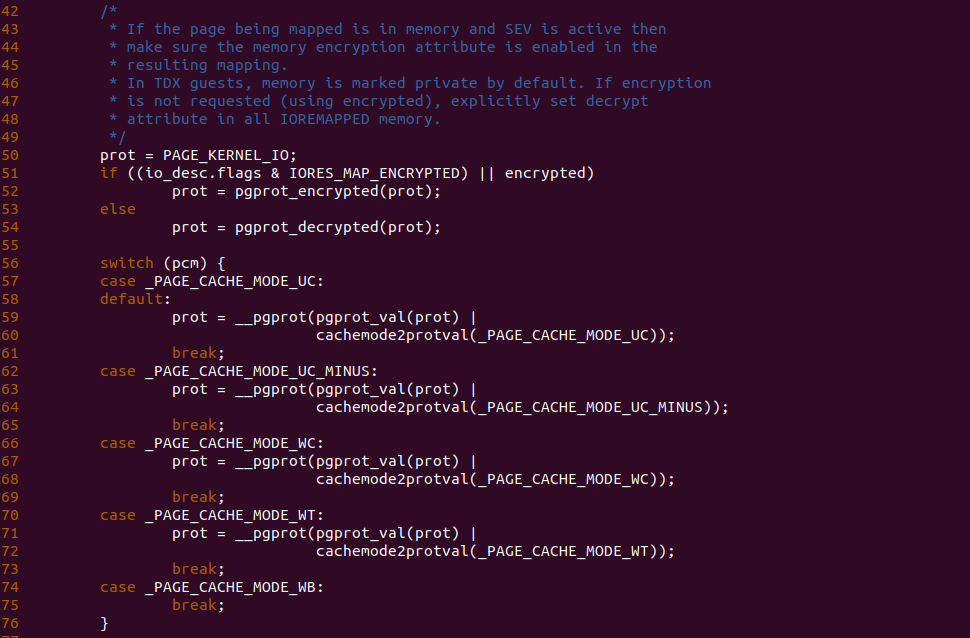

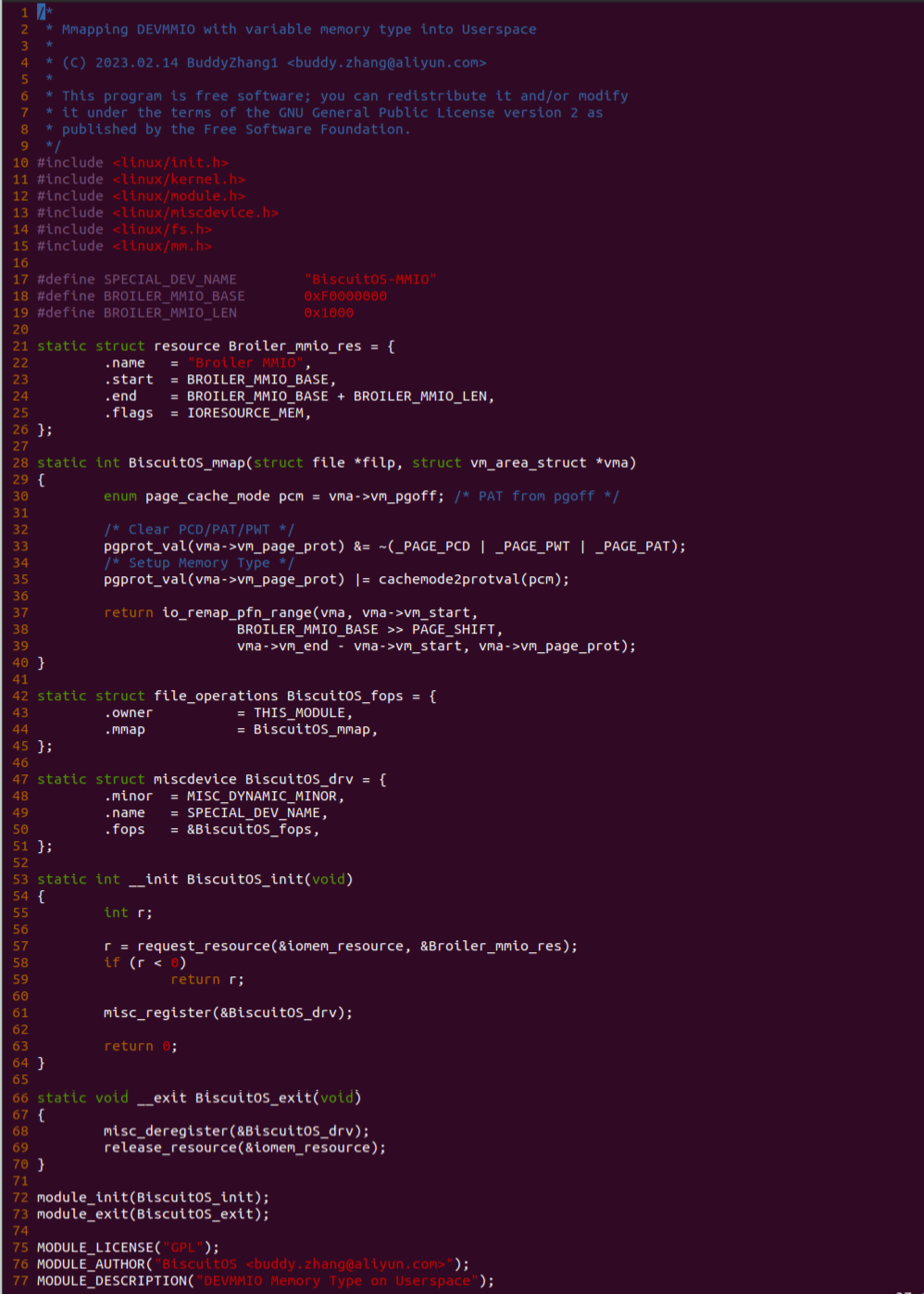

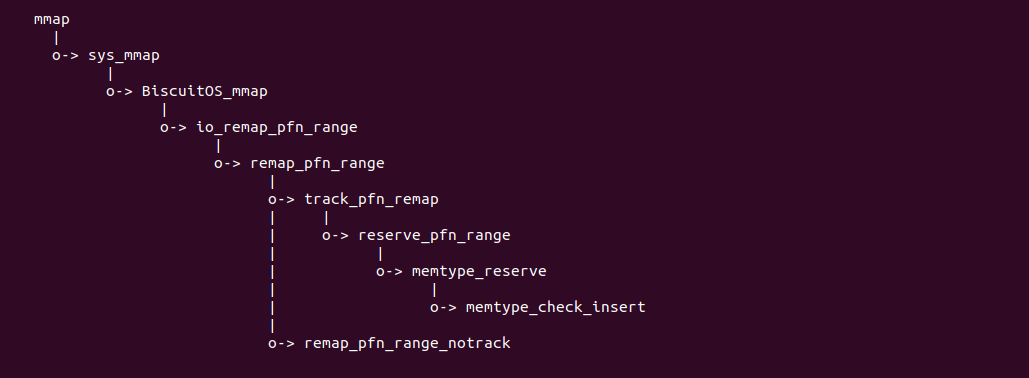

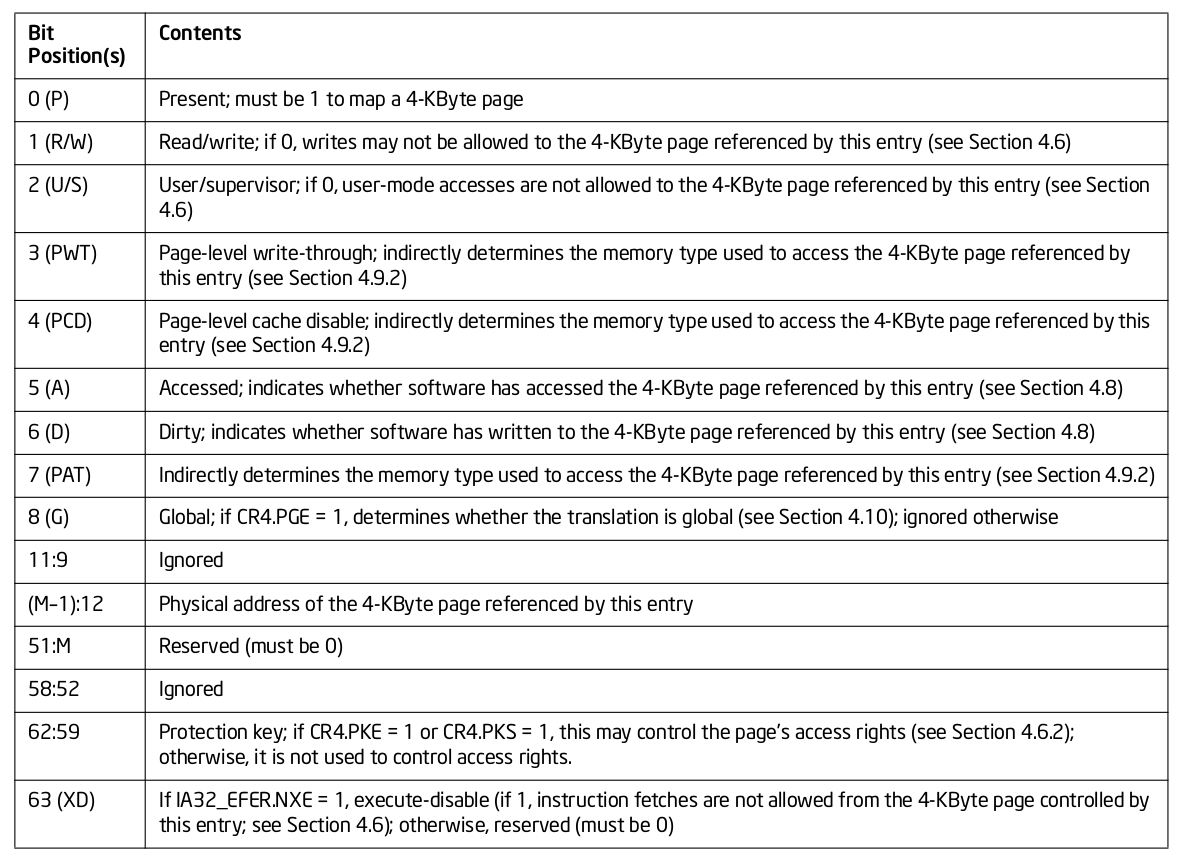

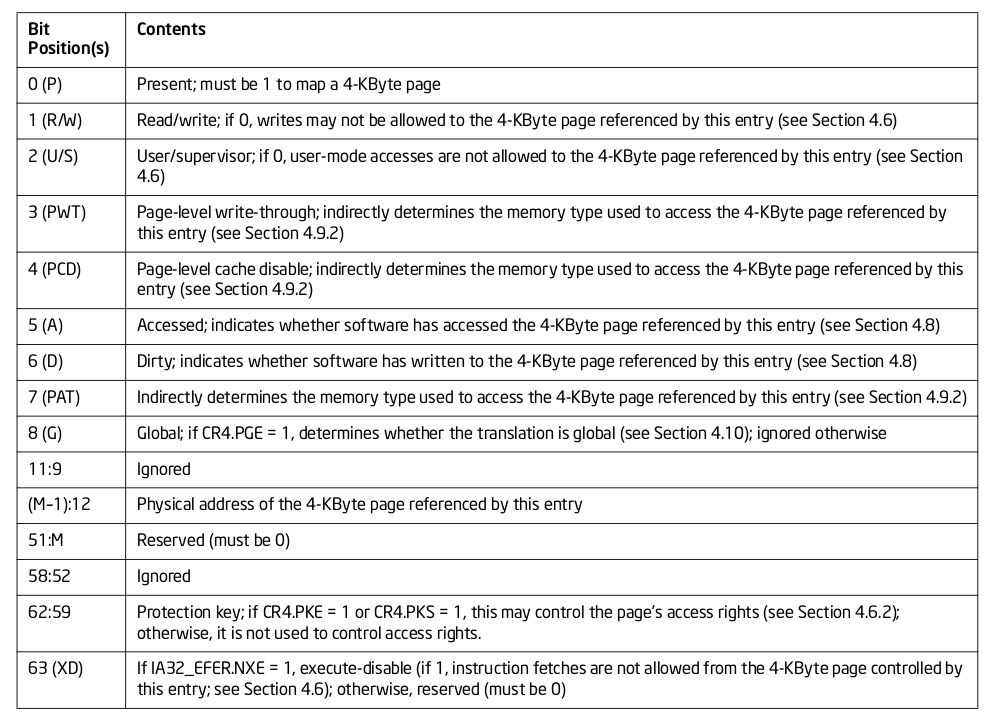

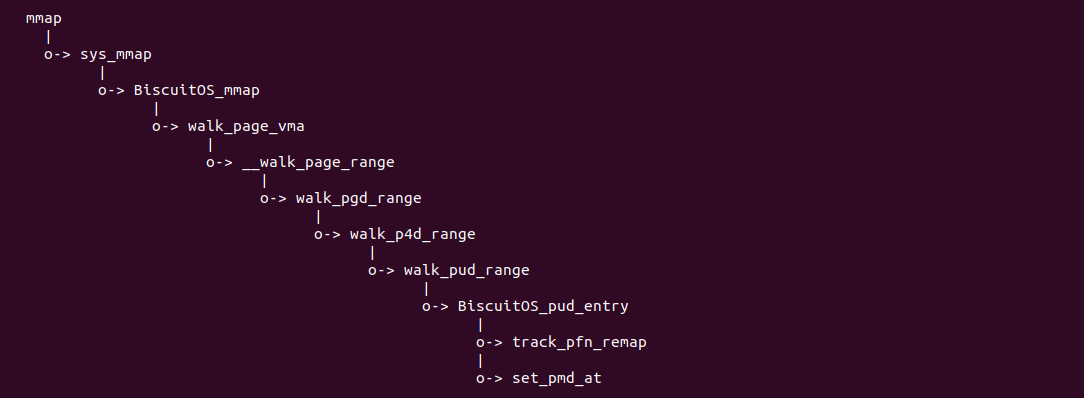

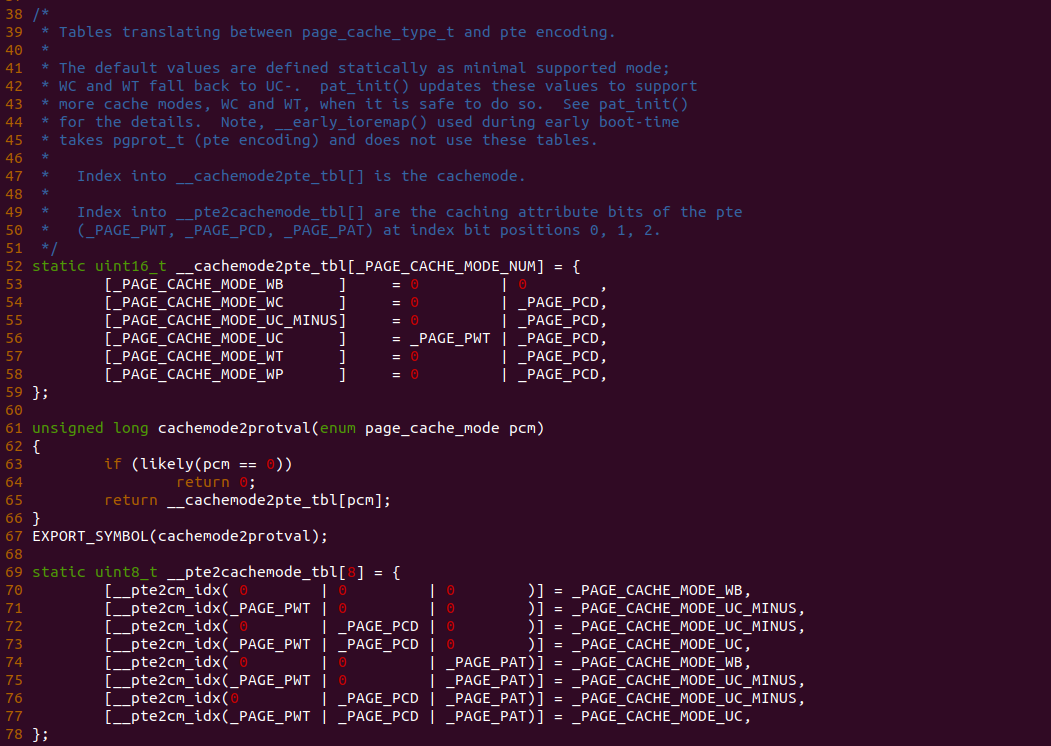

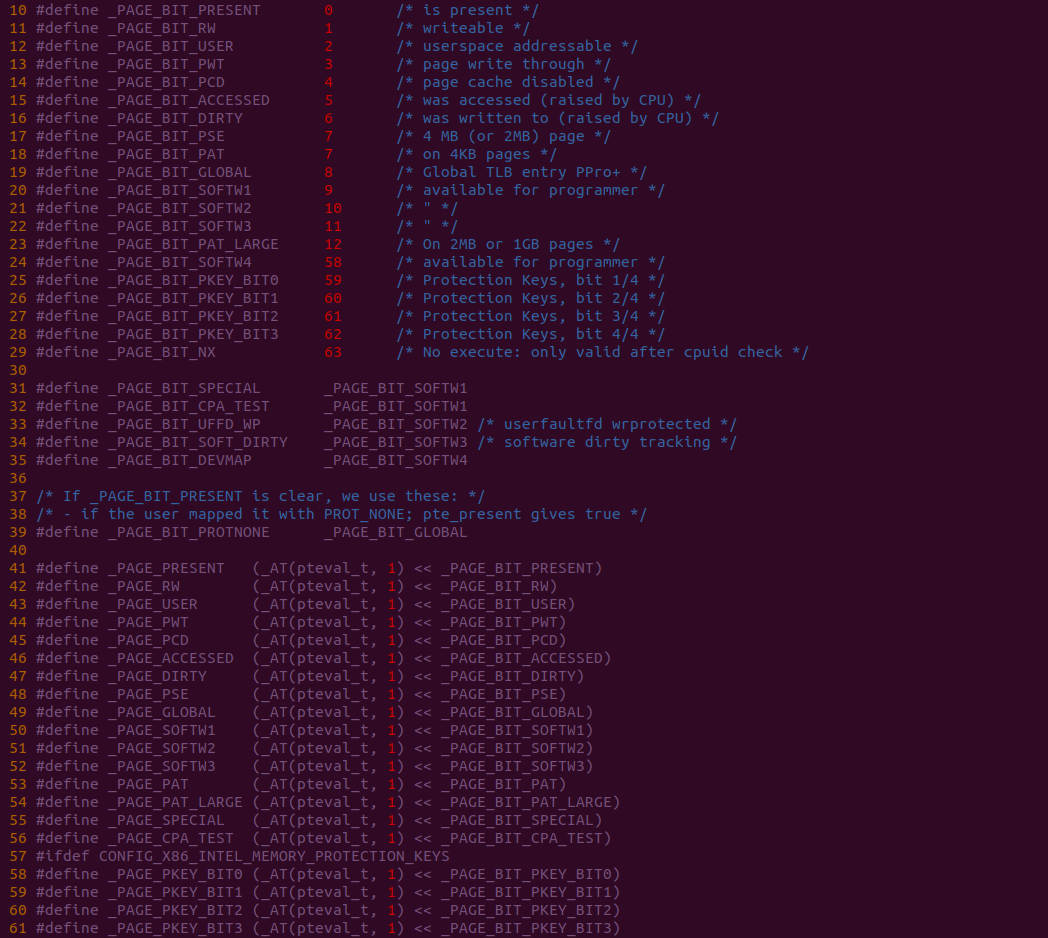

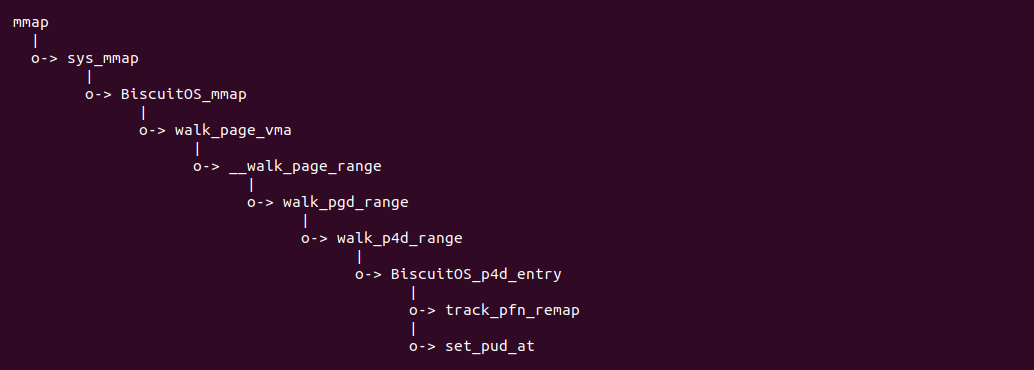

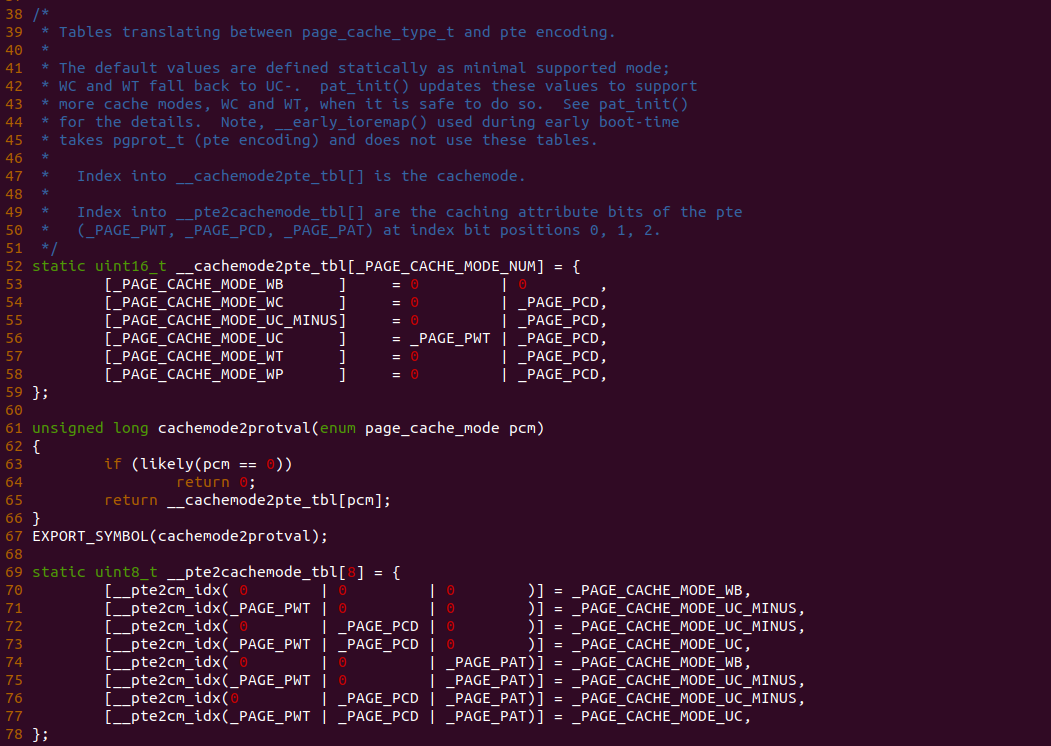

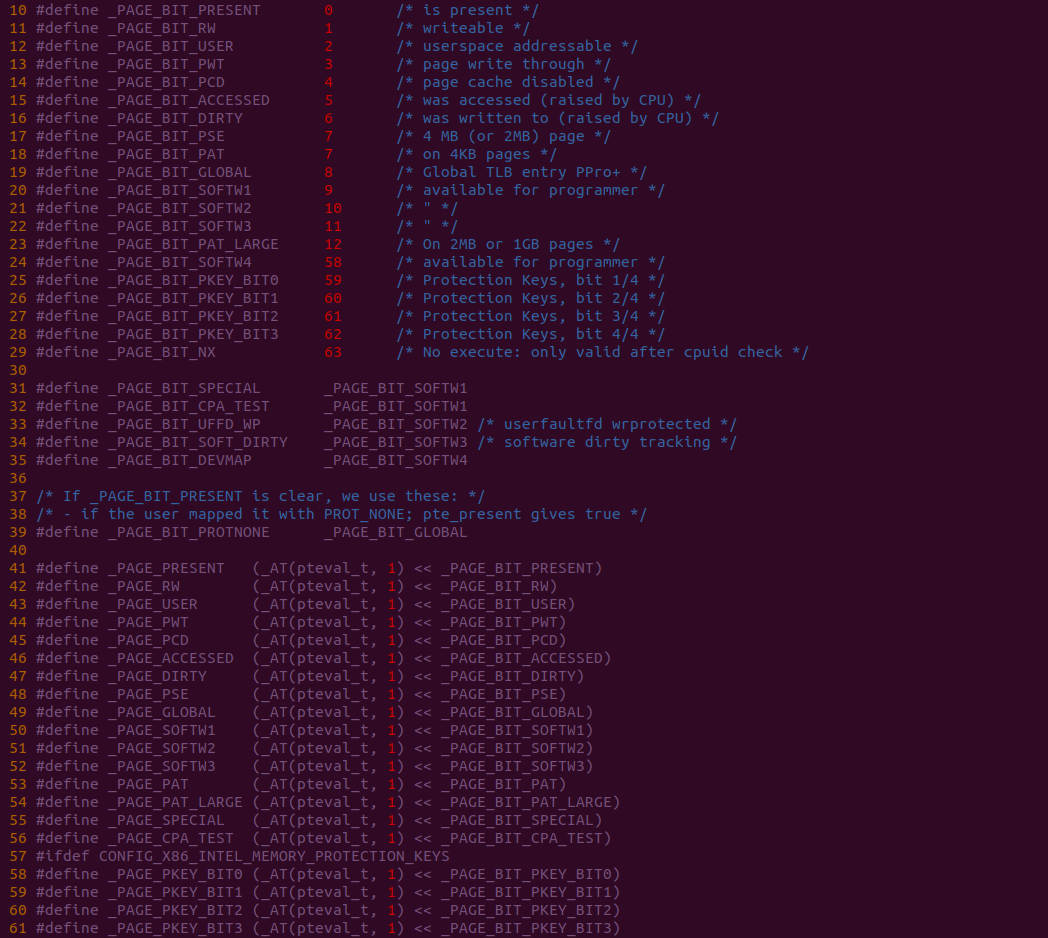

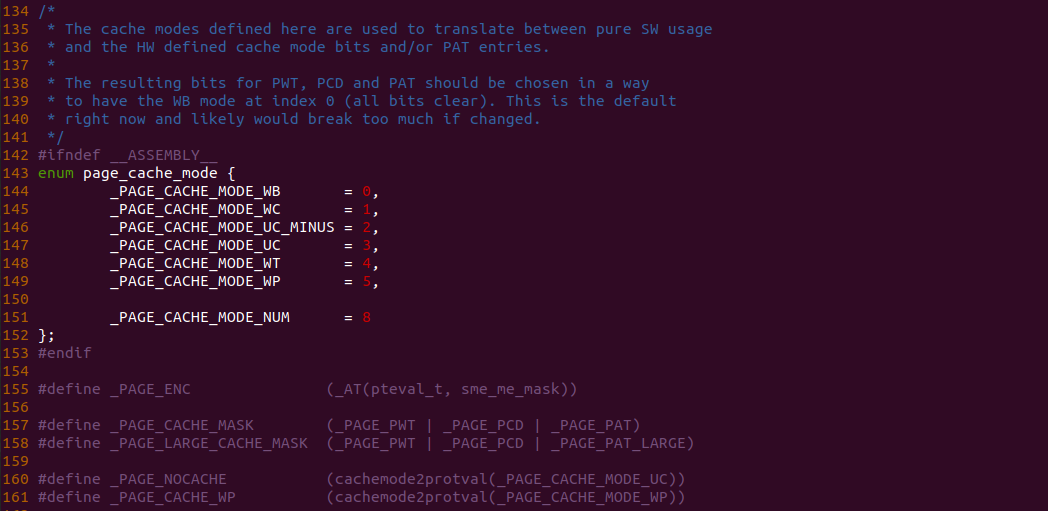

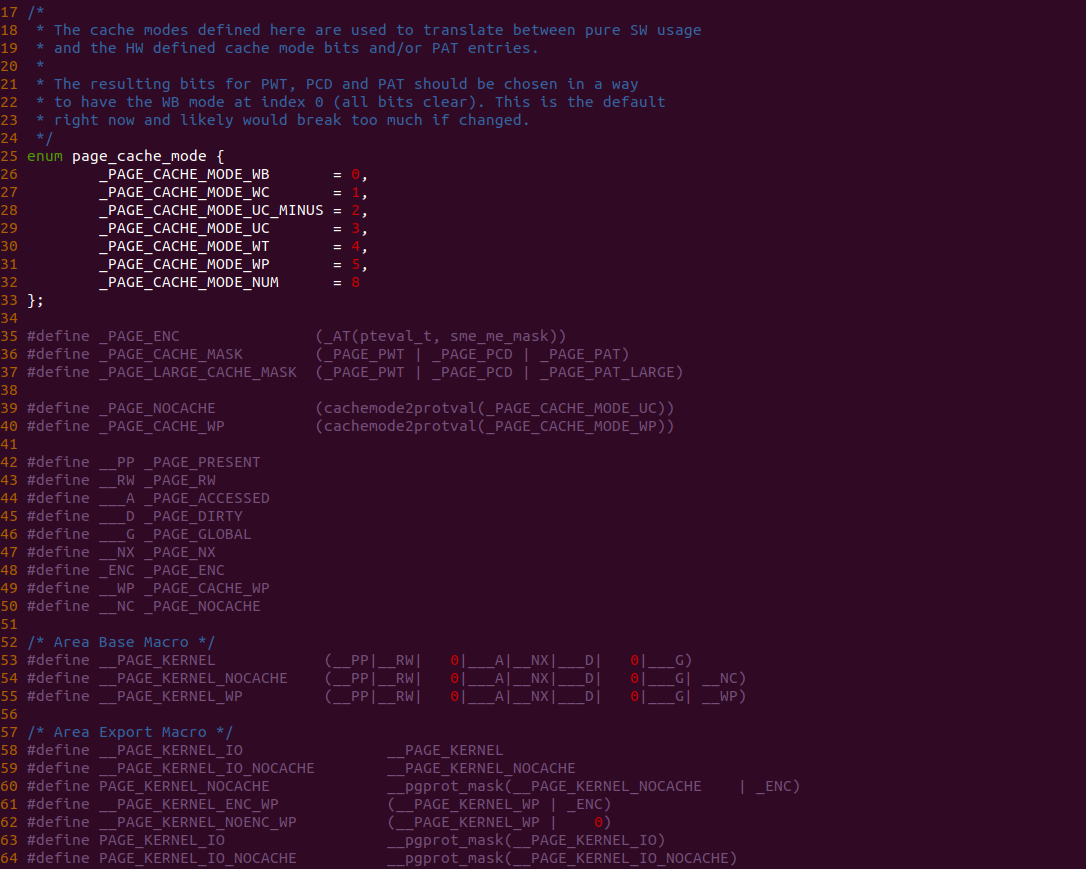

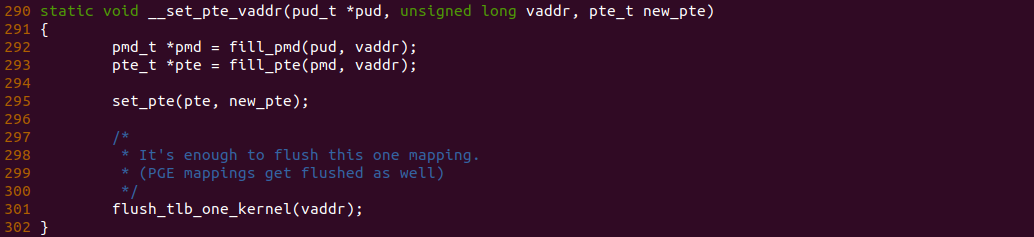

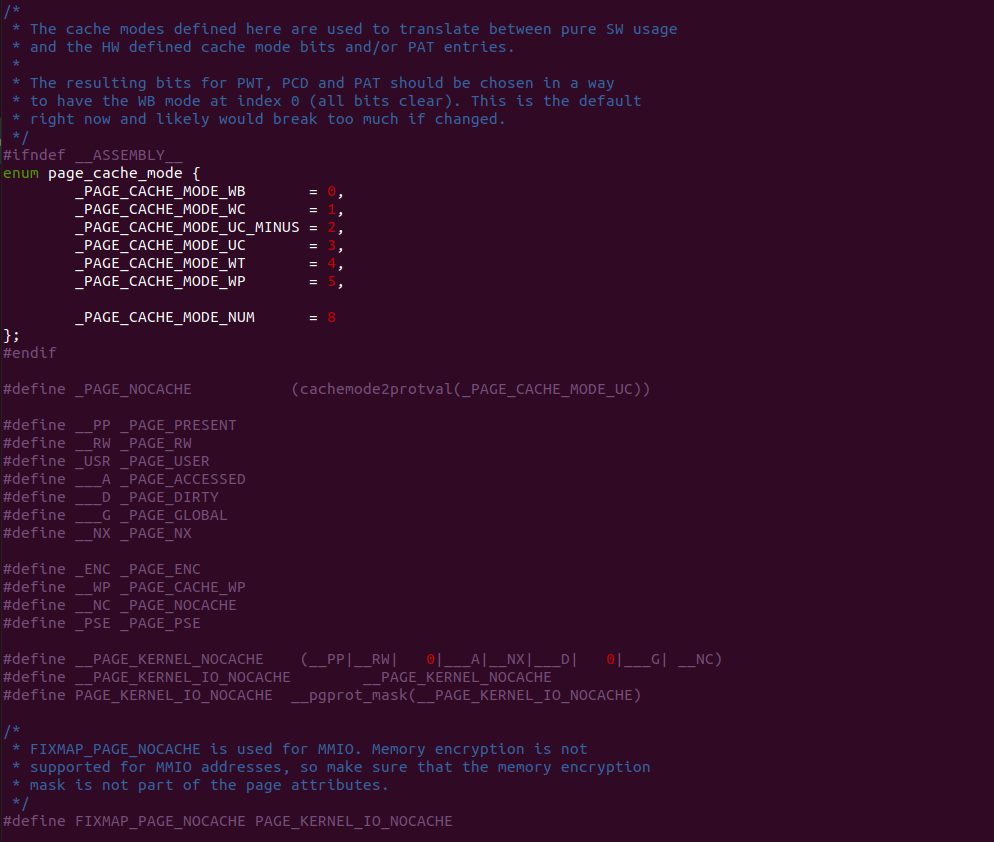

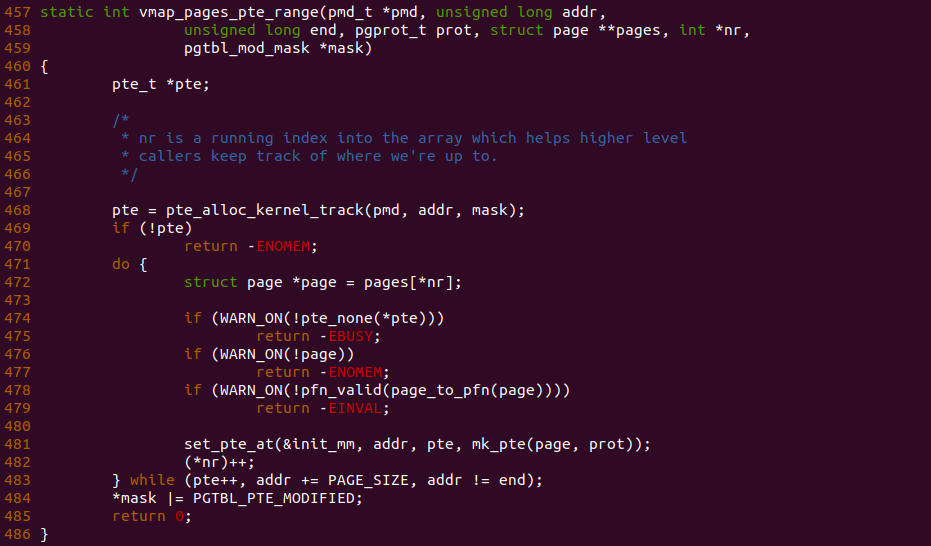

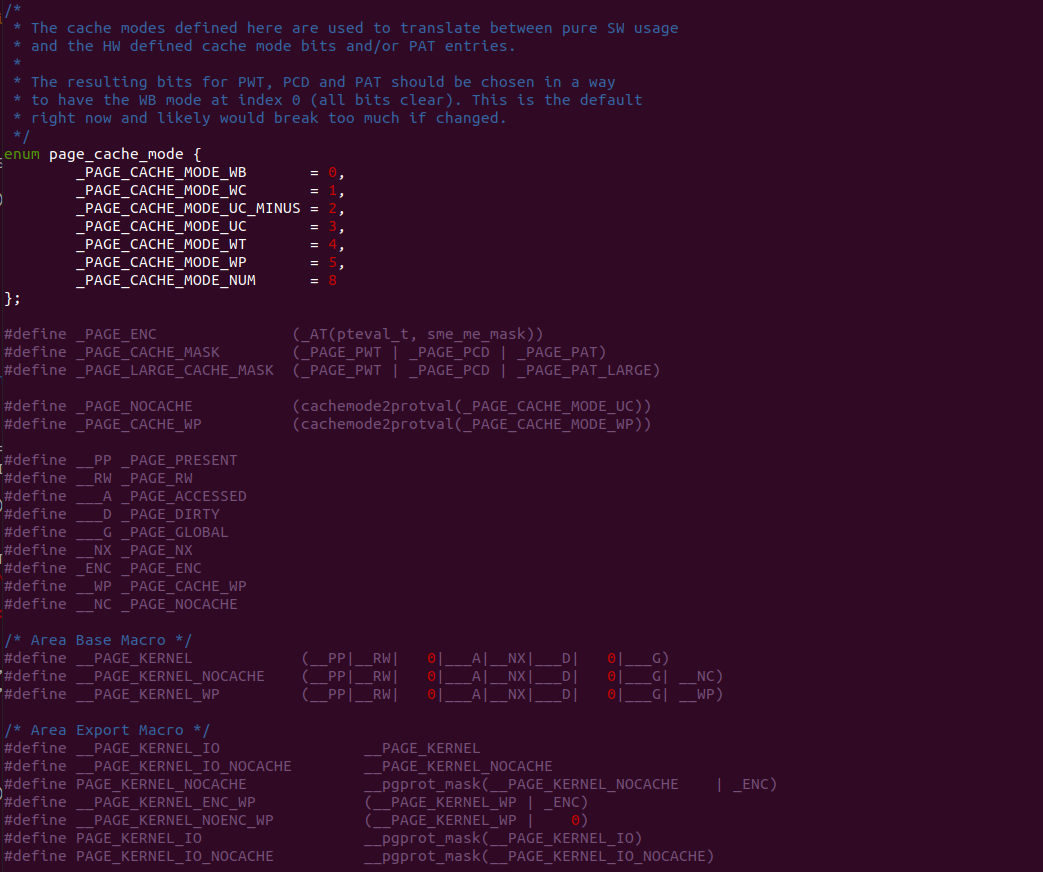

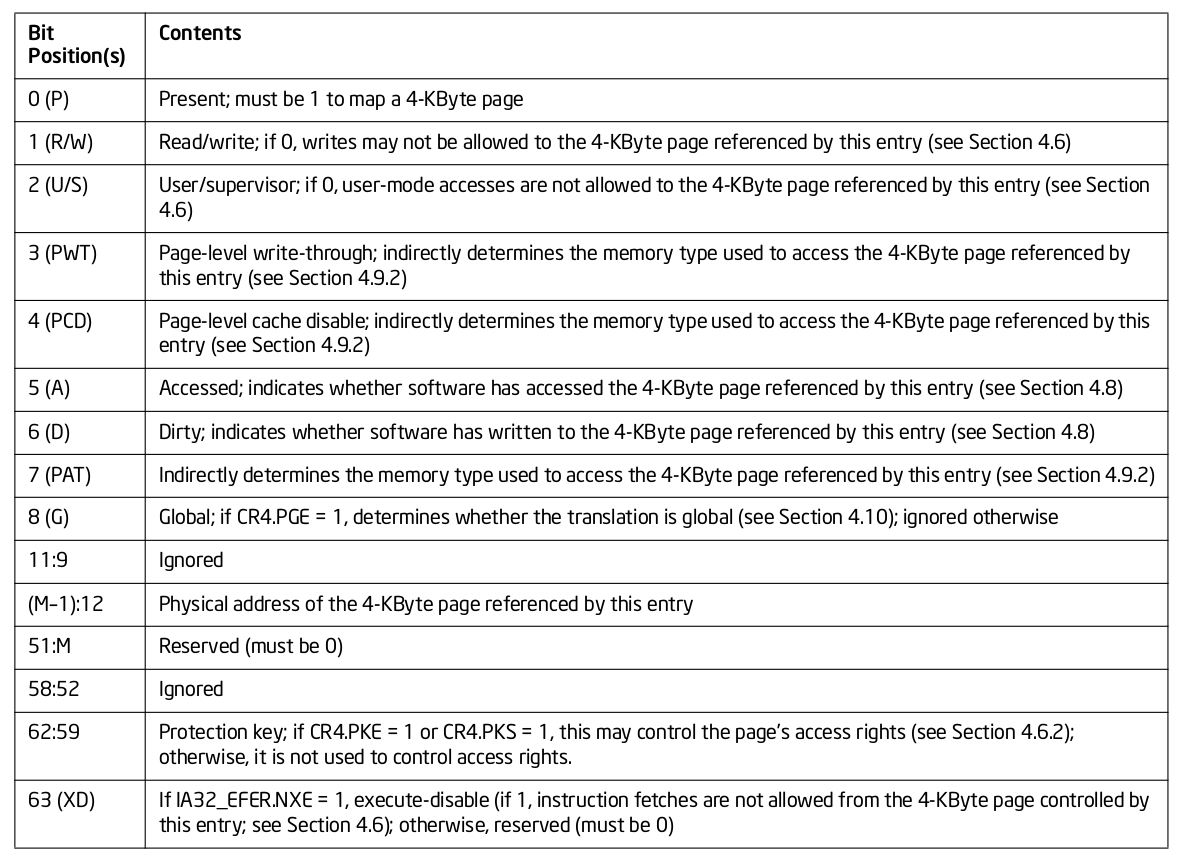

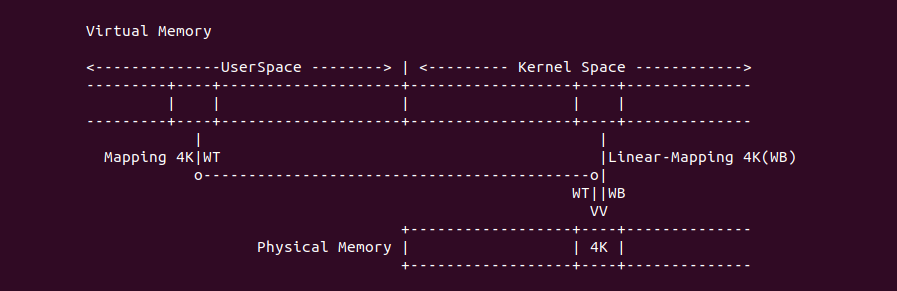

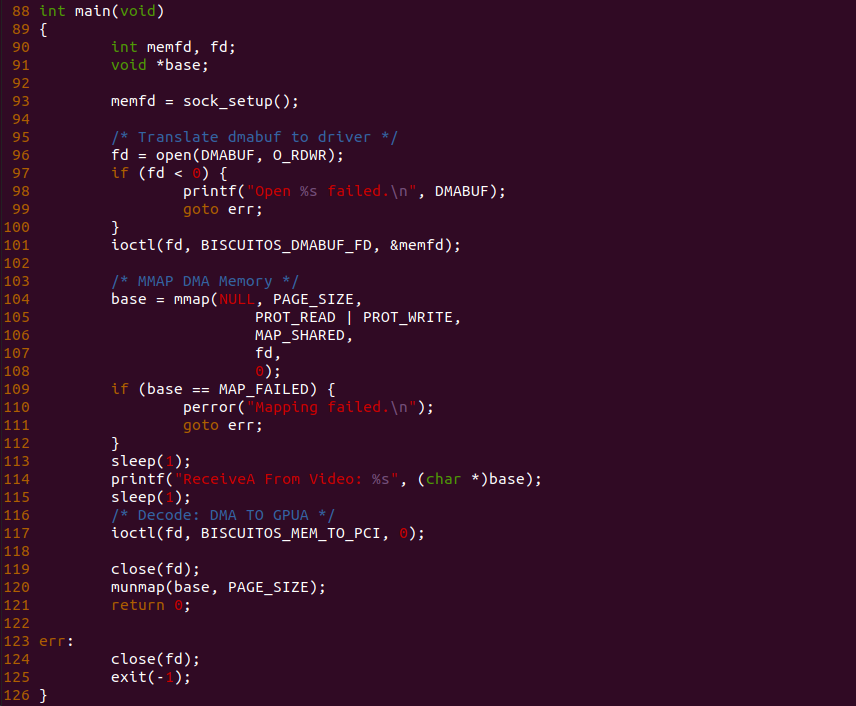

实践案例由两个部分组成,main.c 为内核模块部分,负责映射 MMIO 的底层逻辑。模块首先在 22-26 行定义了 MMIO 区域的信息,然后在 56-57 行通过调用 request_resource() 函数将 MMIO 区域添加到系统物理地址空间树里。模块通过注册一个 MISC 驱动,向用户空间提供 “/dev/BiscuitOS-MMIO” 接口,用户空间程序打开该接口,并调用 mmap() 映射 MMIO 时会调用到模块的 BiscuitOS_mmap() 函数,该函数首先在 32 行将虚拟地址对应的页表属性里的 _PAGE_PAT、_PAGE_PCD 和 _PAGE_PWT 标志清除,然后在 34 行调用 cachemode2protval() 函数,结合 _PAGE_CACHE_MODE_UC 将相关的 PAT 页表属性赋值到 vm_page_prot 成员里,接下来调用 io_remap_pfn_range() 函数进行虚拟地址到 MMIO 的映射工作。映射完毕之后用户空间虚拟地址就可以以 UC 方式访问 MMIO.

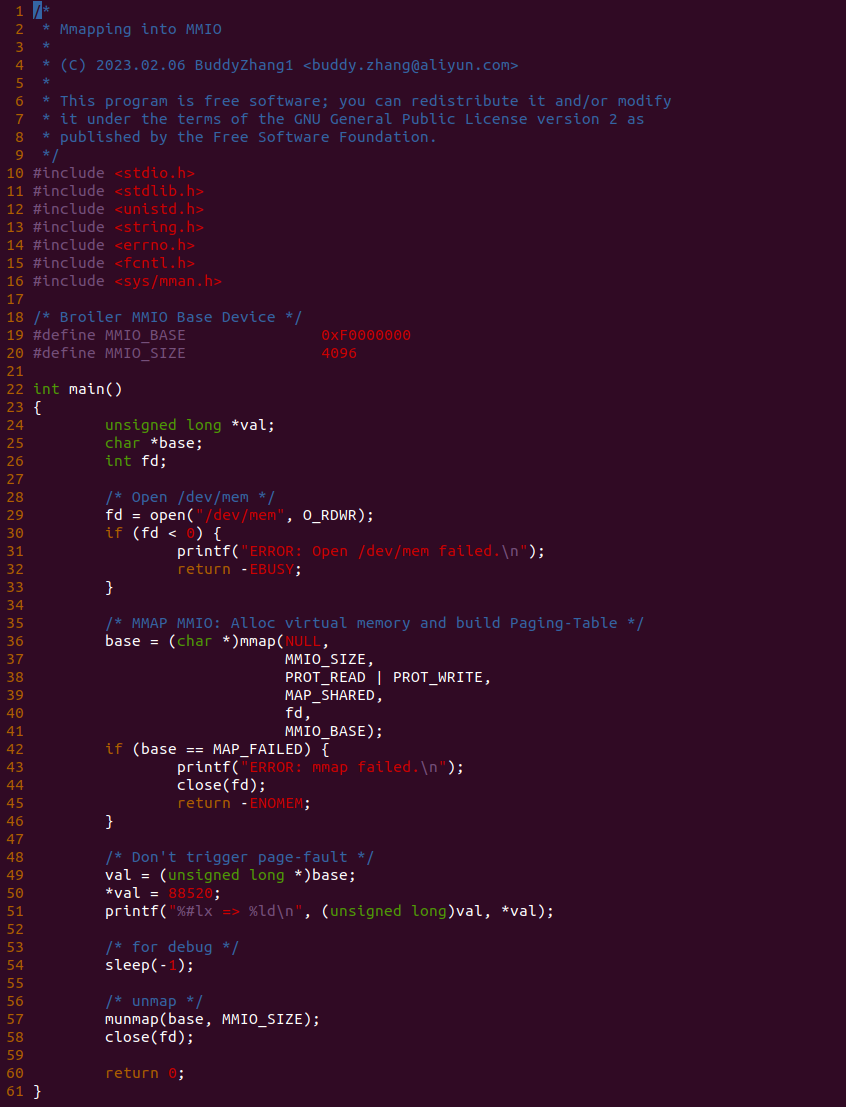

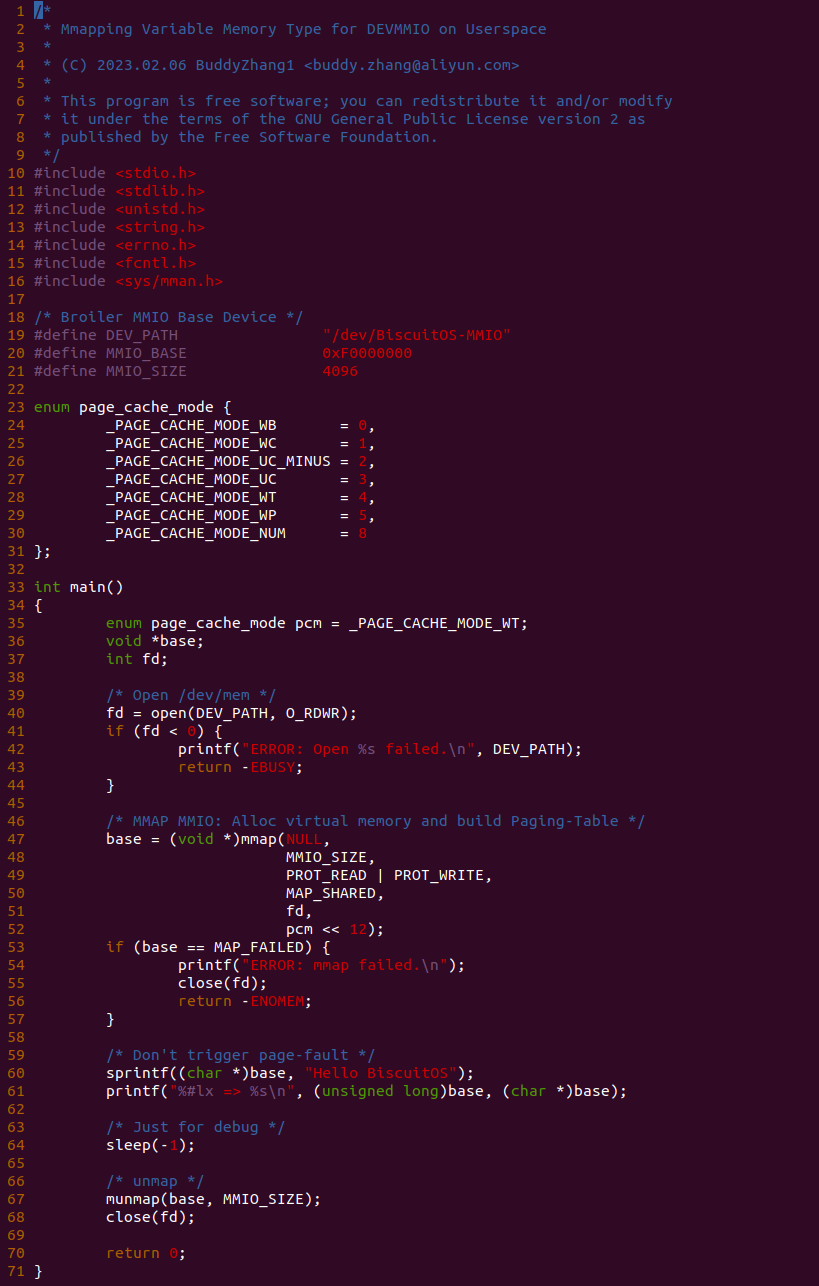

实践案例的另外一部分位于 app.c 内,其为用户空间程序,用于映射虚拟地址到 MMIO 并进行访问. 程序首先在 29 行通过 open() 函数打开 “/dev/BiscuitOS-MMIO” 节点,然后在 36-46 通过 mmap() 函数将进程地址空间的虚拟地址映射到 MMIO,接下来在 49-51 行对映射之后对 MMIO 进行访问,最后在 56-57 行释放相应的资源. 源码分析完毕之后在 BiscuitOS 进行实践,由于 MMIO 绑定在具体的硬件上,此时可以使用 Broiler 进行模块,直接使用 “make broiler” 命令进行实践:

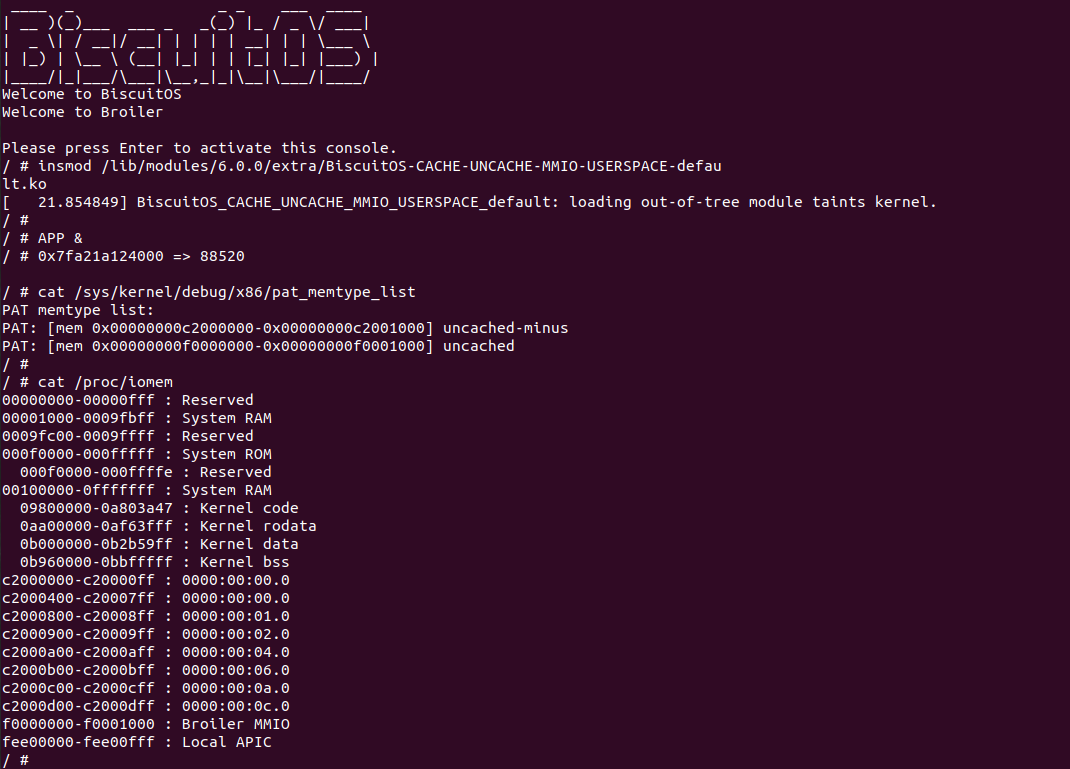

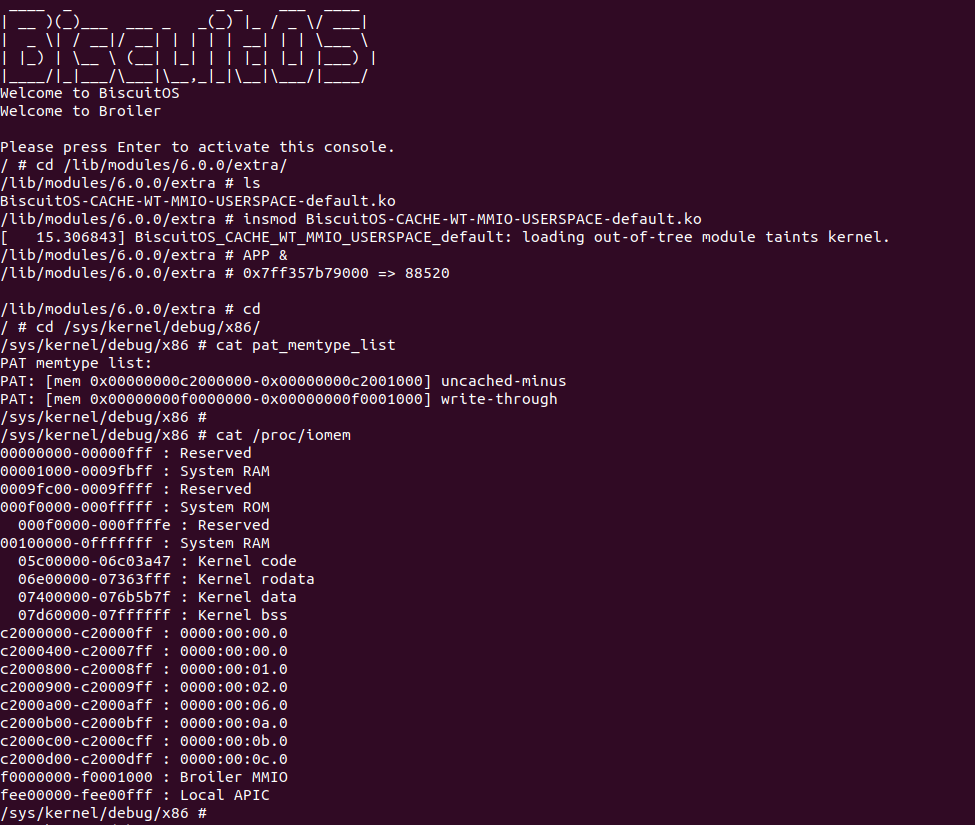

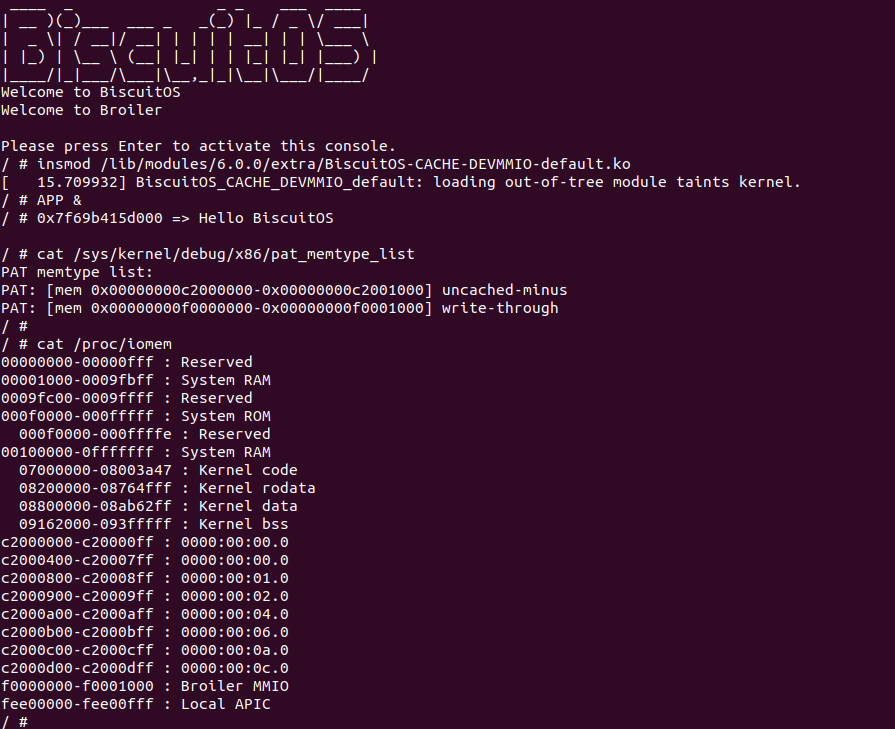

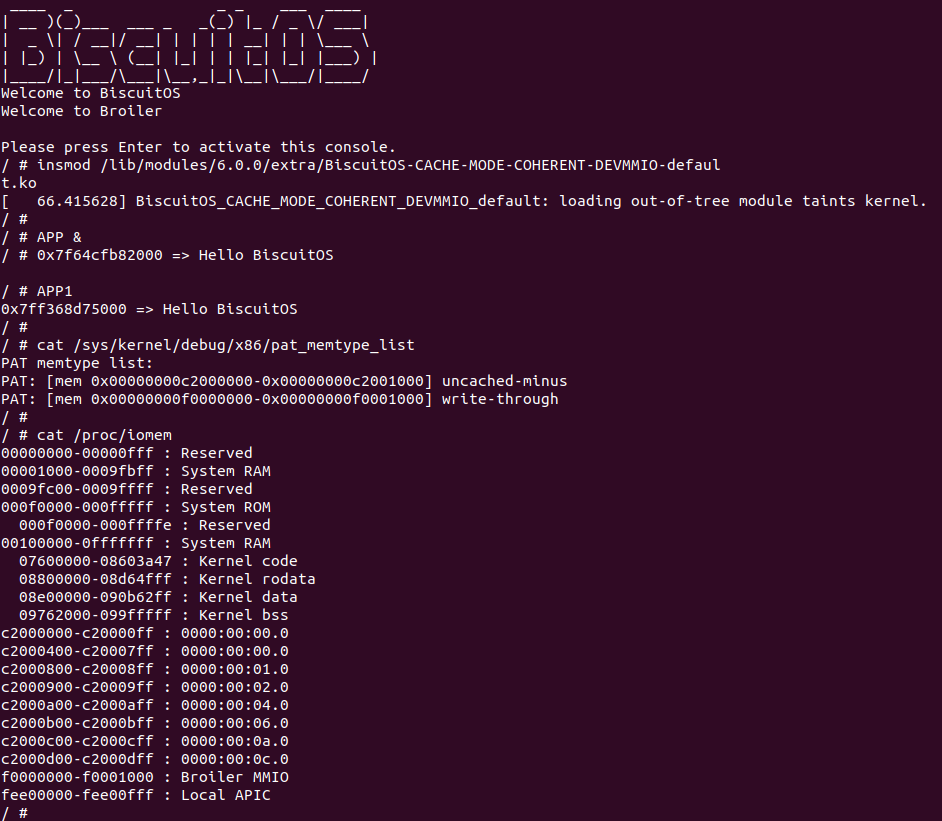

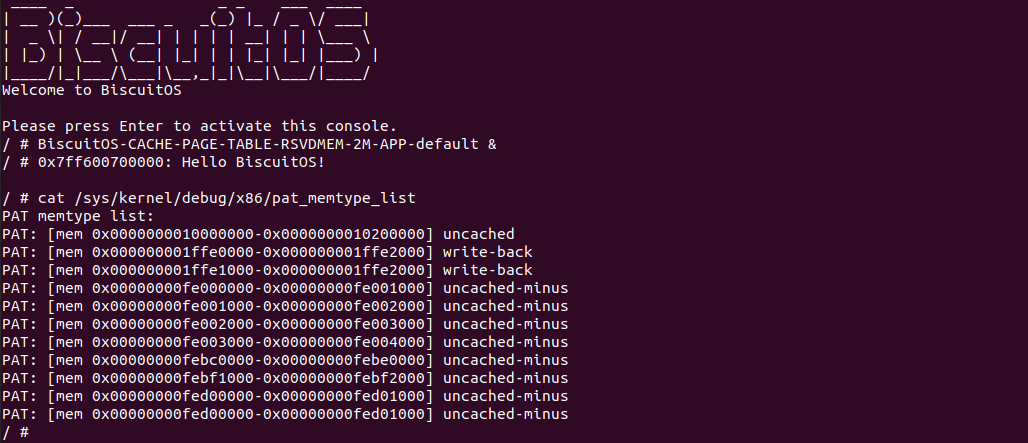

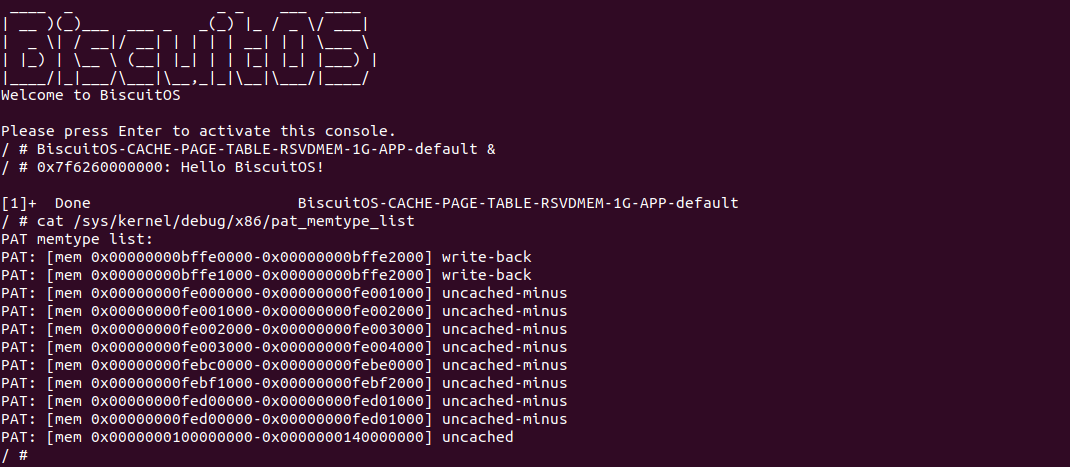

BiscuitOS Broiler 运行之后加载 BiscuitOS-CACHE-UNCACHE-MMIO-USERSPACE-default.ko, 接着运行用户态程序 APP,这里以后台方式运行,因此查看其他有用信息,运行之后可以看到正常访问 MMIO。接下来查看 /sys/kernel/debug/x86/pat_memtype_list 节点,可以看到 [0xF0000000, 0xF0001000) 区域映射为 uncached,最后查看 /proc/iomem 系统物理地址空间,可以看到 Broiler MMIO 对应的区域正好是 [0xF0000000, 0xF0001000)。实践结果符合预期,那么接下来对普通物理内存映射为 UC 场景进行实践:

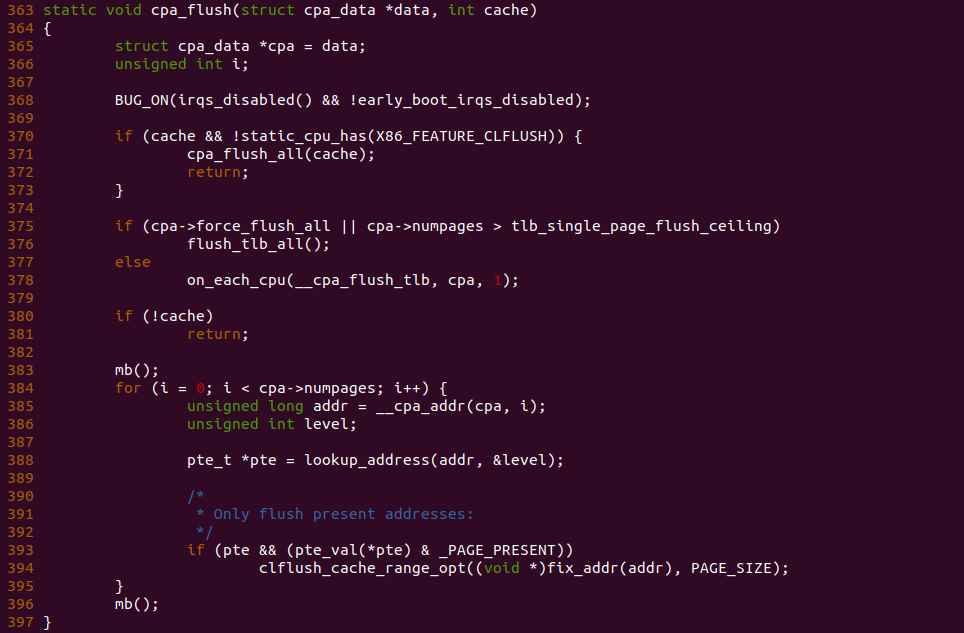

用户空间虚拟内存映射 UC 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] UNCACHE(UC): Mapping UC Memory on Userspace --->

-*- CACHE User-Page for Kernel Stub (Basic) --->

# 进入源码目录

# Userspace: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-UNCACHE-MEM-USERSPACE-default/

# Kernel: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default/

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-UNCACHE-MEM-USERSPACE-default/

# 部署源码

make prepare

make download

# 在 BiscuitOS 中实践

make buildBiscuitOS-CACHE-UNCACHE-MEM-USERSPACE-default Source Code on Gitee

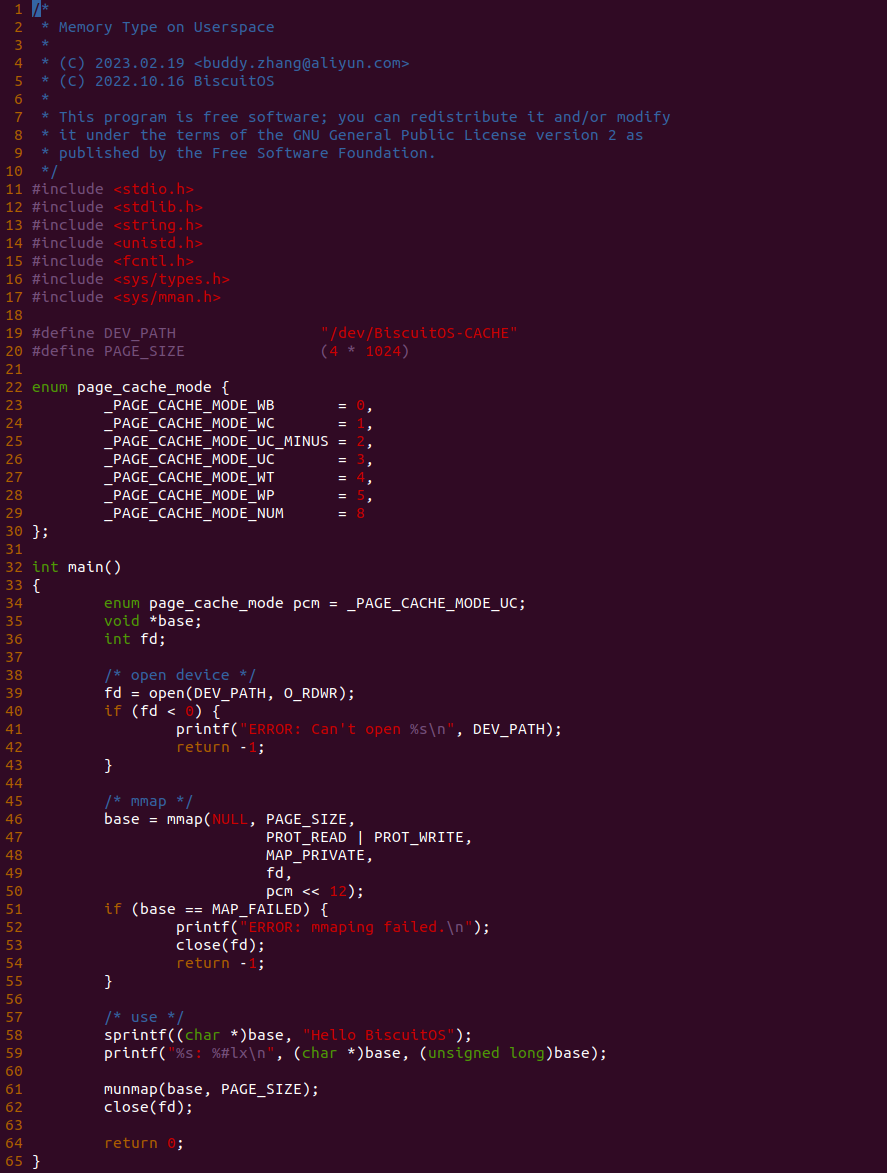

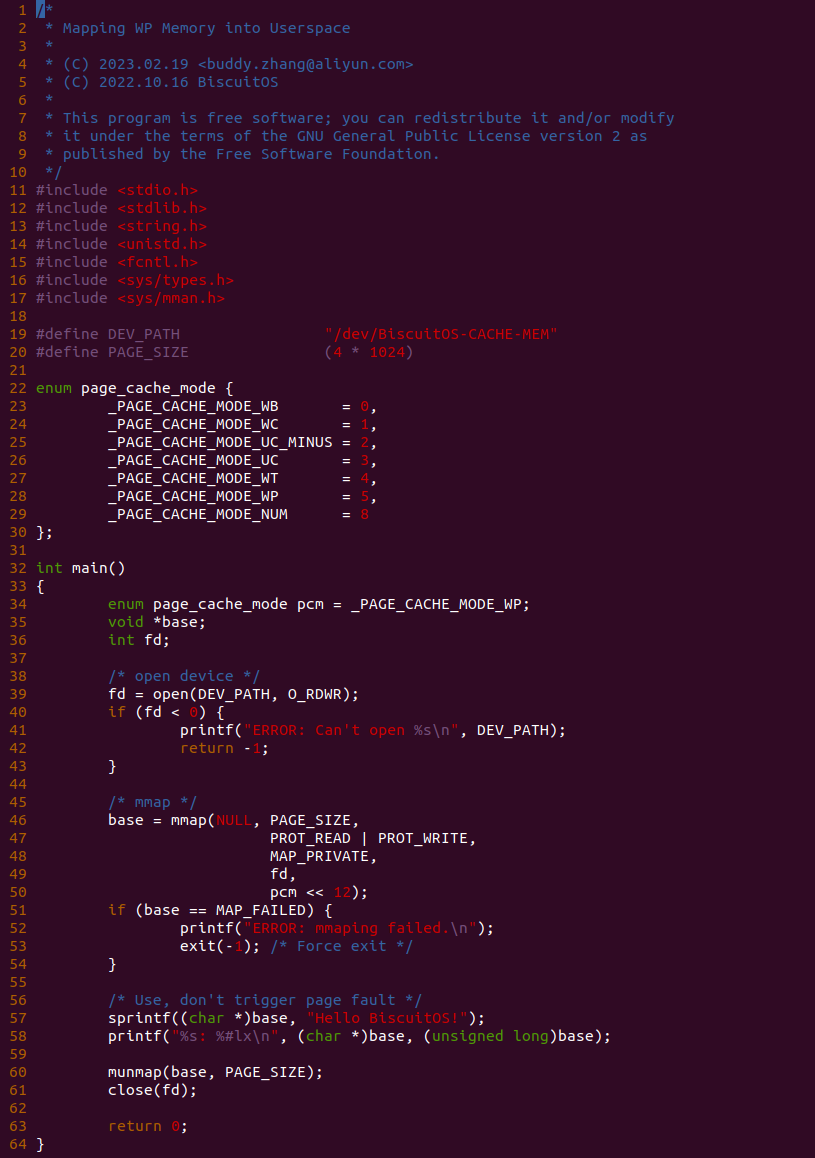

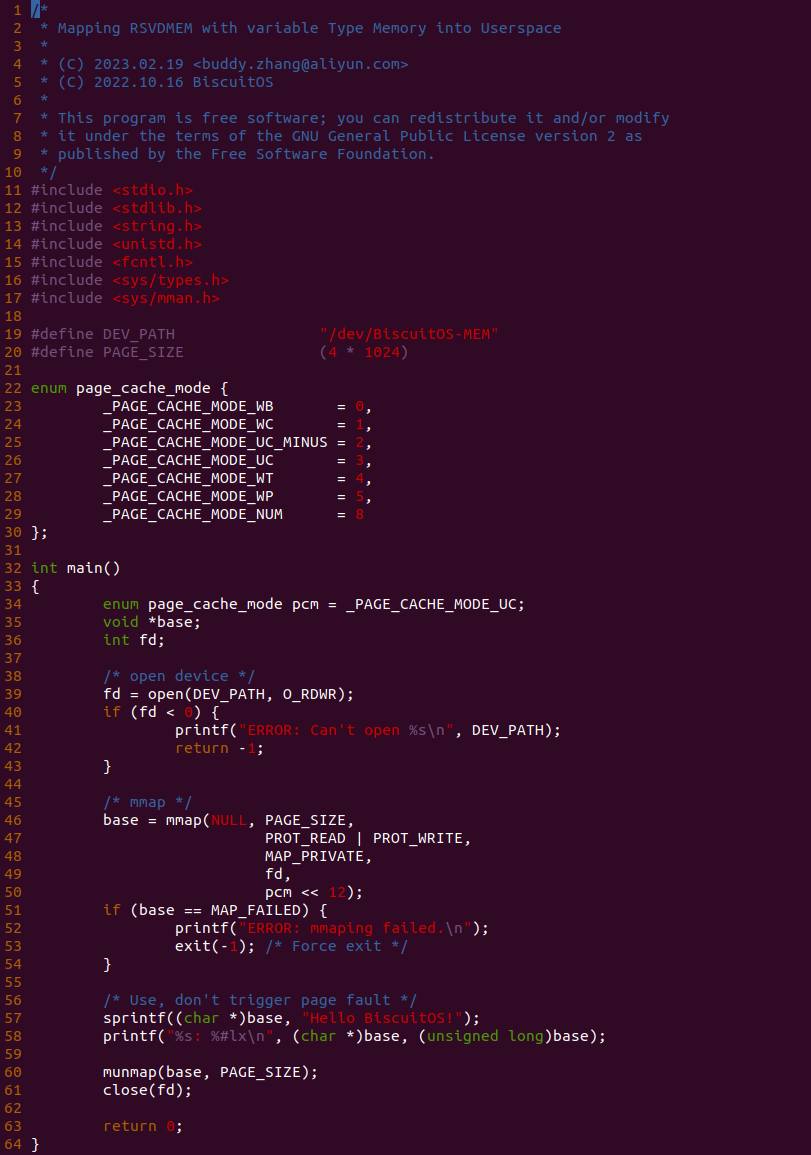

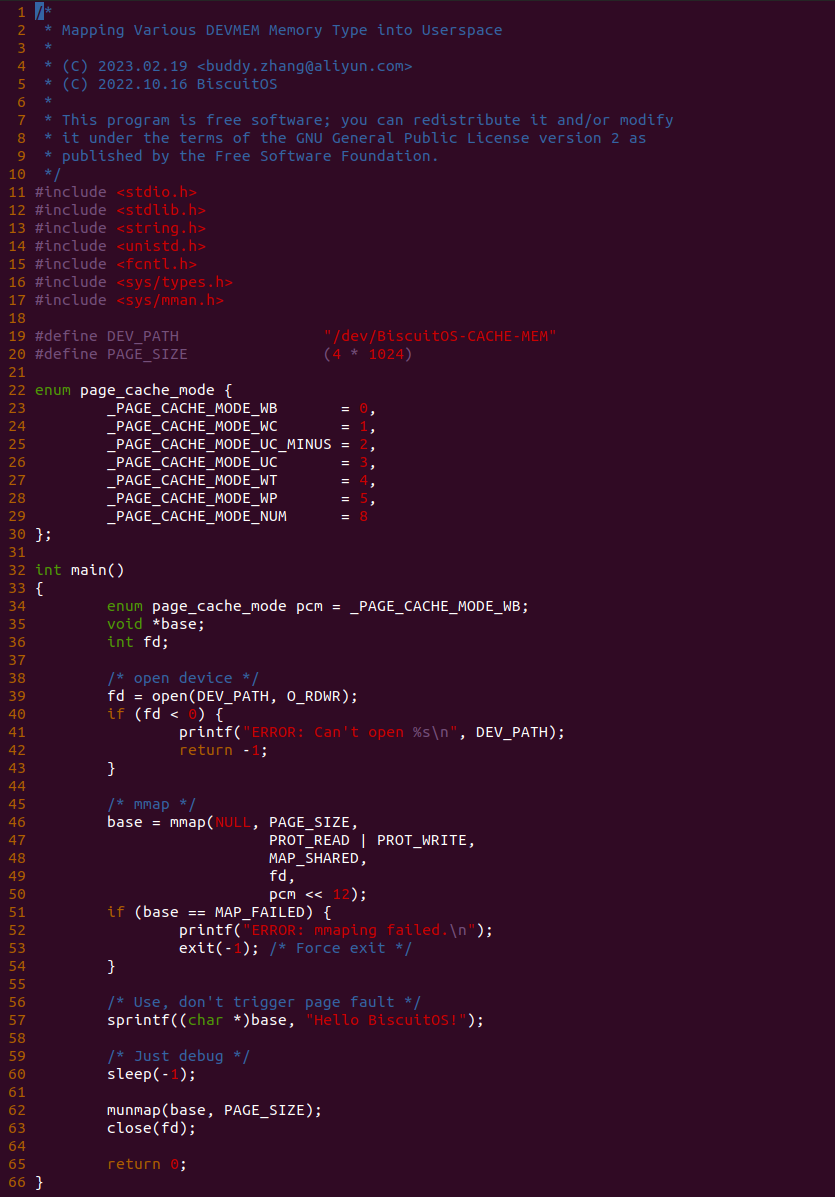

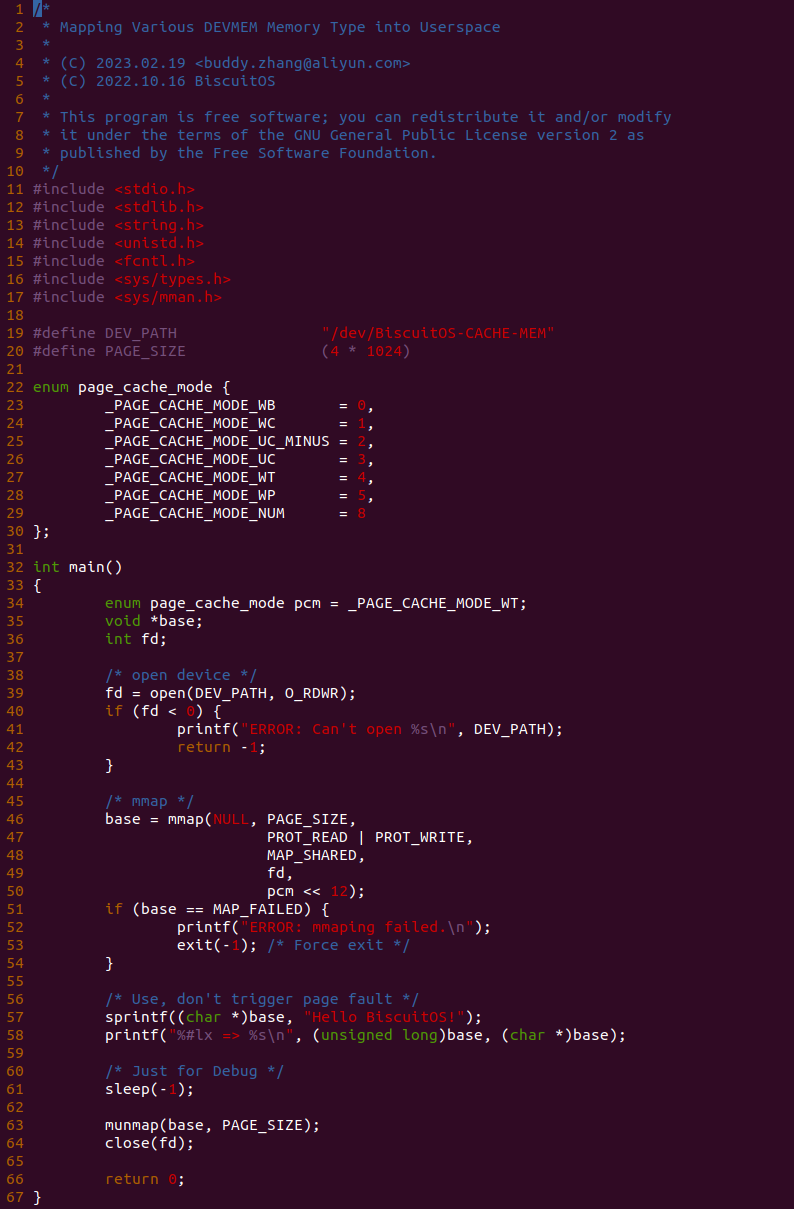

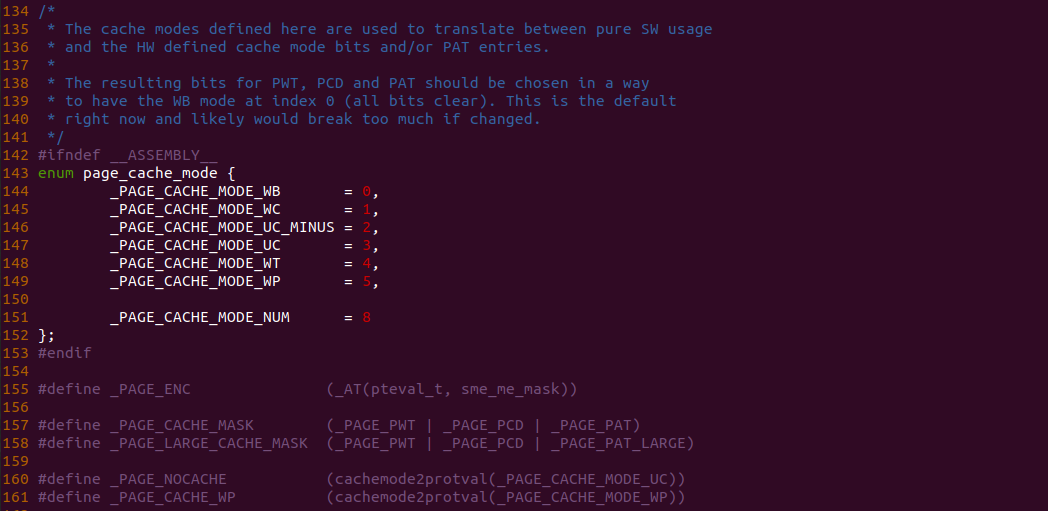

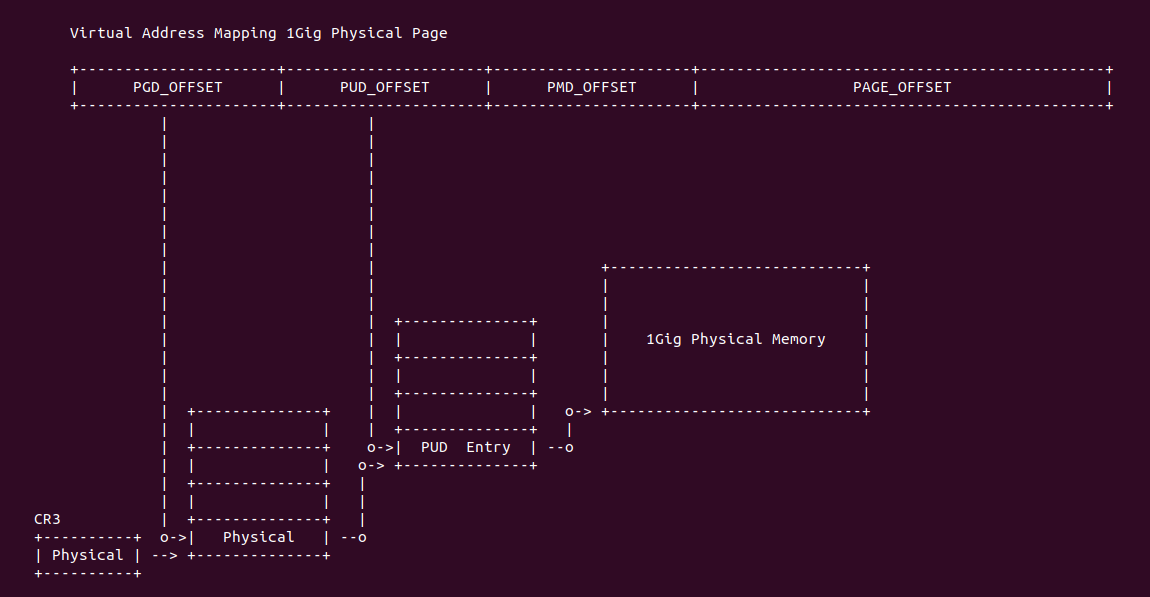

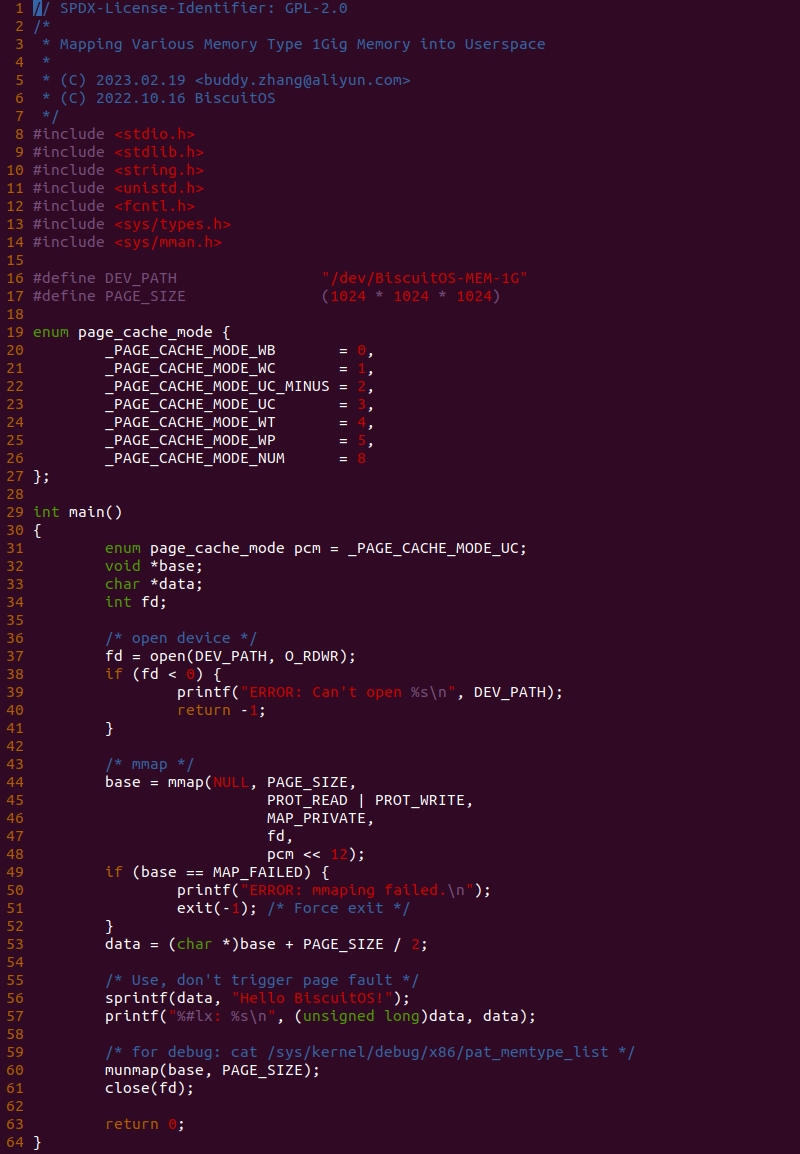

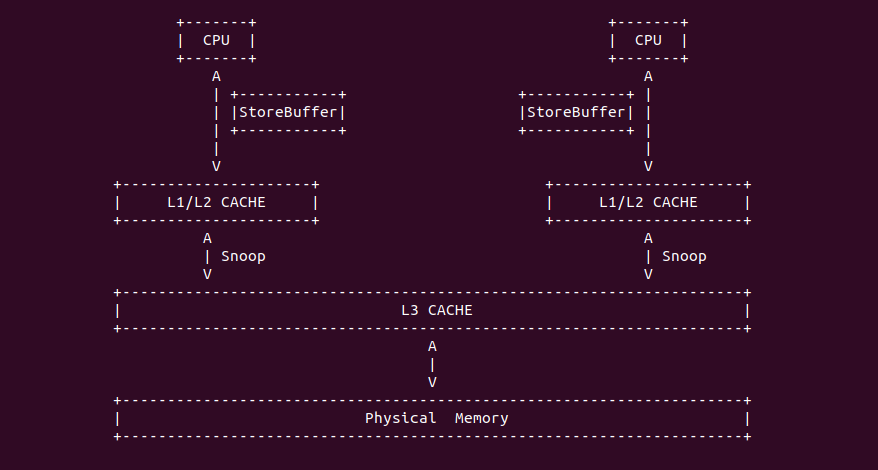

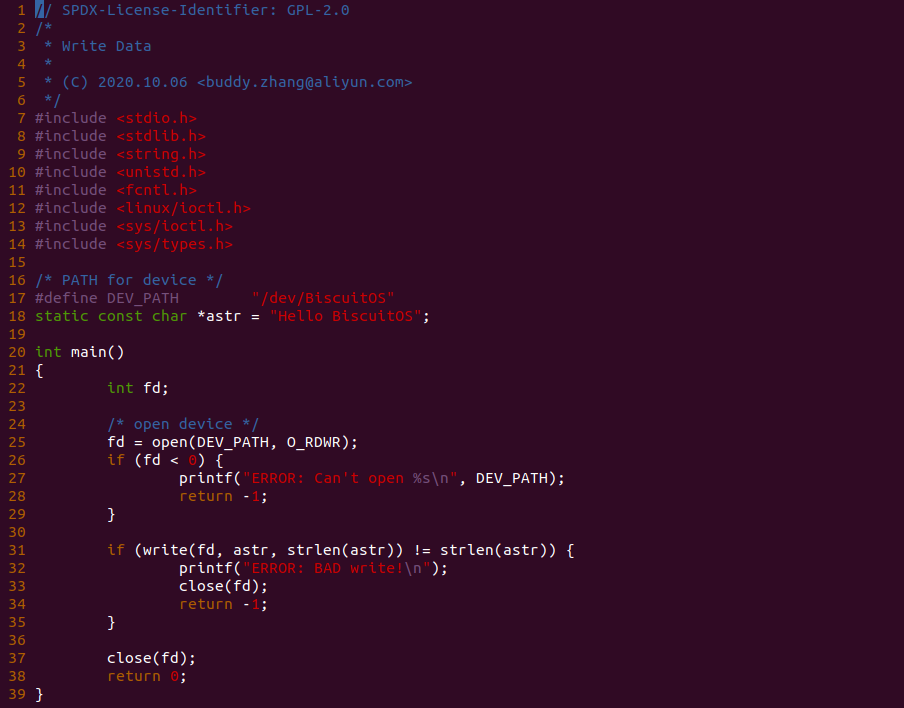

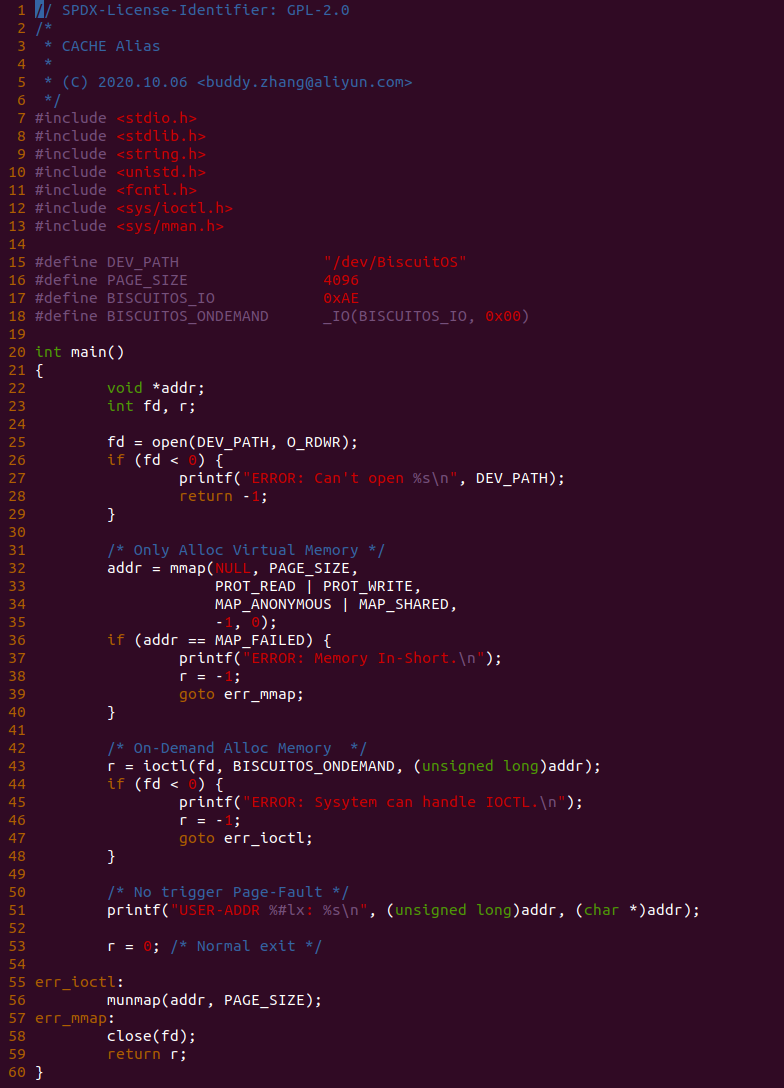

源码分成两部分,其中一部分为用户空间程序(上图所示), 用户空间代码的主要功能是映射一段虚拟内存,并将其缓存类型设置为 UC. 函数首先在 34 行将 pcm 变量设置为 _PAGE_CACHE_MODE_UC, 然后在 39 行打开 “/dev/BiscuitOS-CACHE” 节点,并基于该节点映射长度为 PAGE_SIZE 的虚拟内存,此时在函数 50 行将 pcm 传入到 mmap() 函数,映射完毕后函数在 58-59 行使用 UC 的内存,使用完毕在 61-62 行解除映射并关闭文件。

BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default Source Code on Gitee

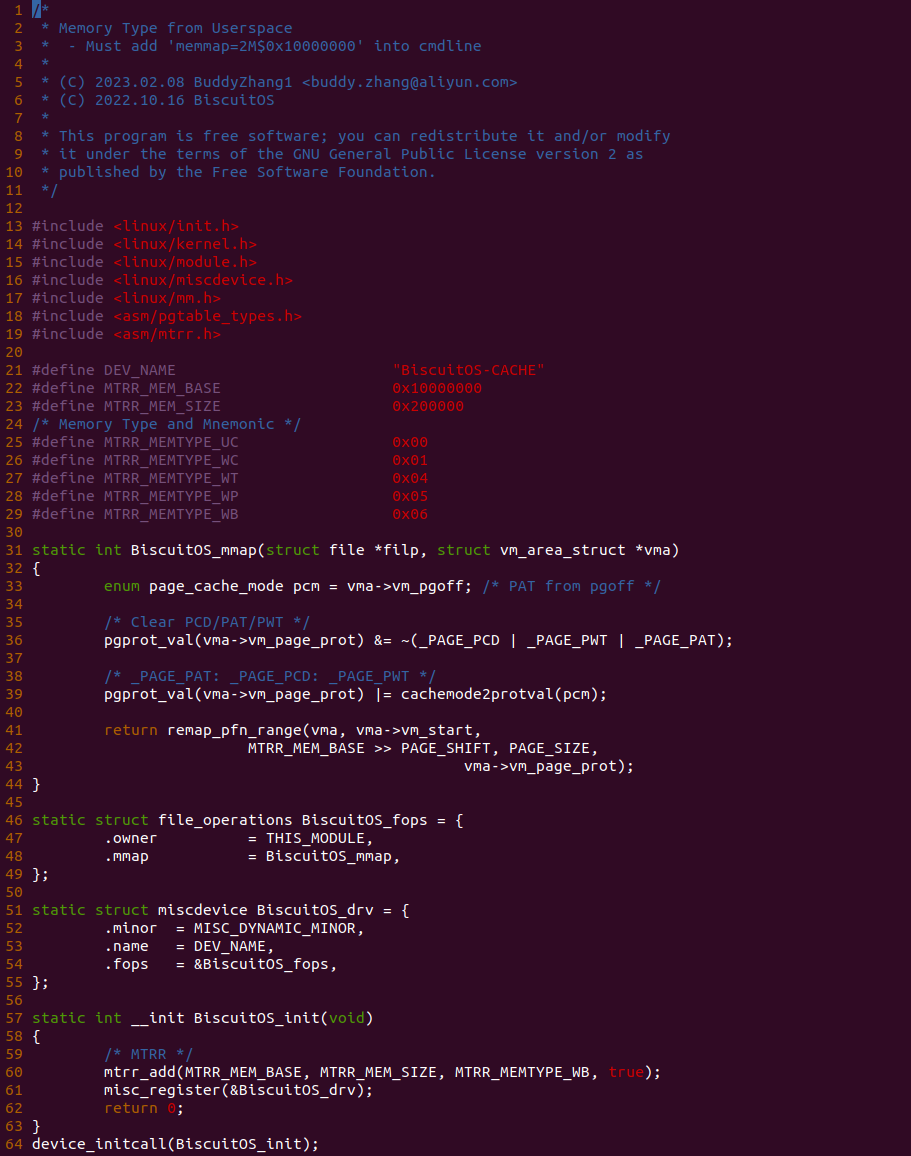

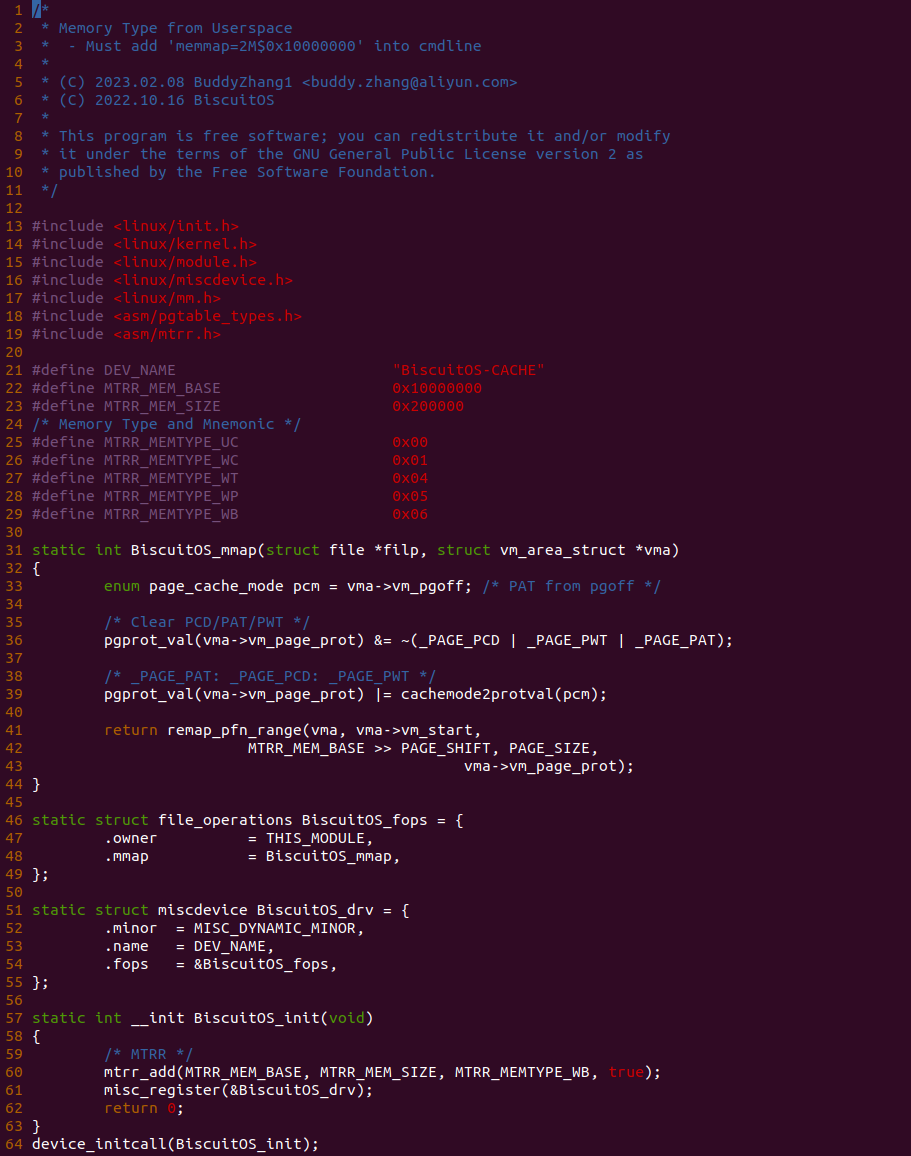

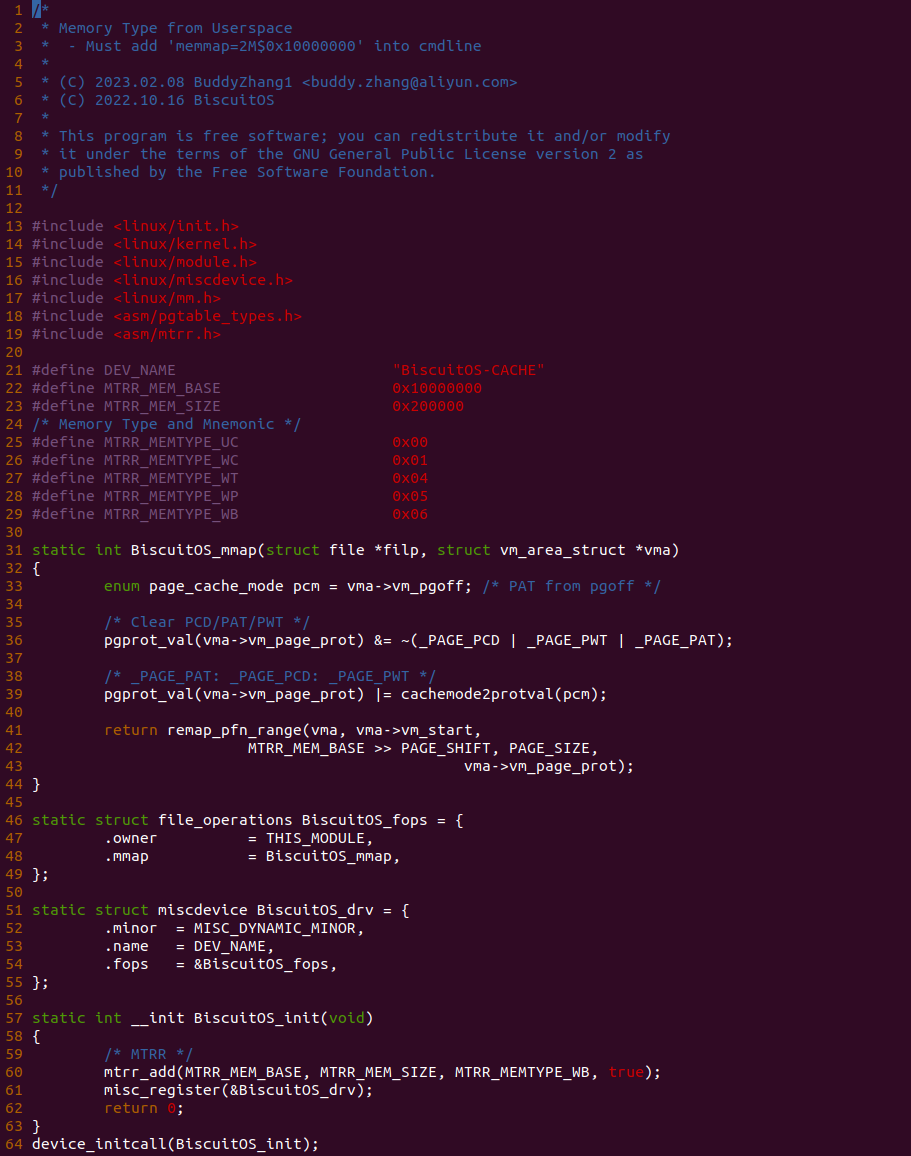

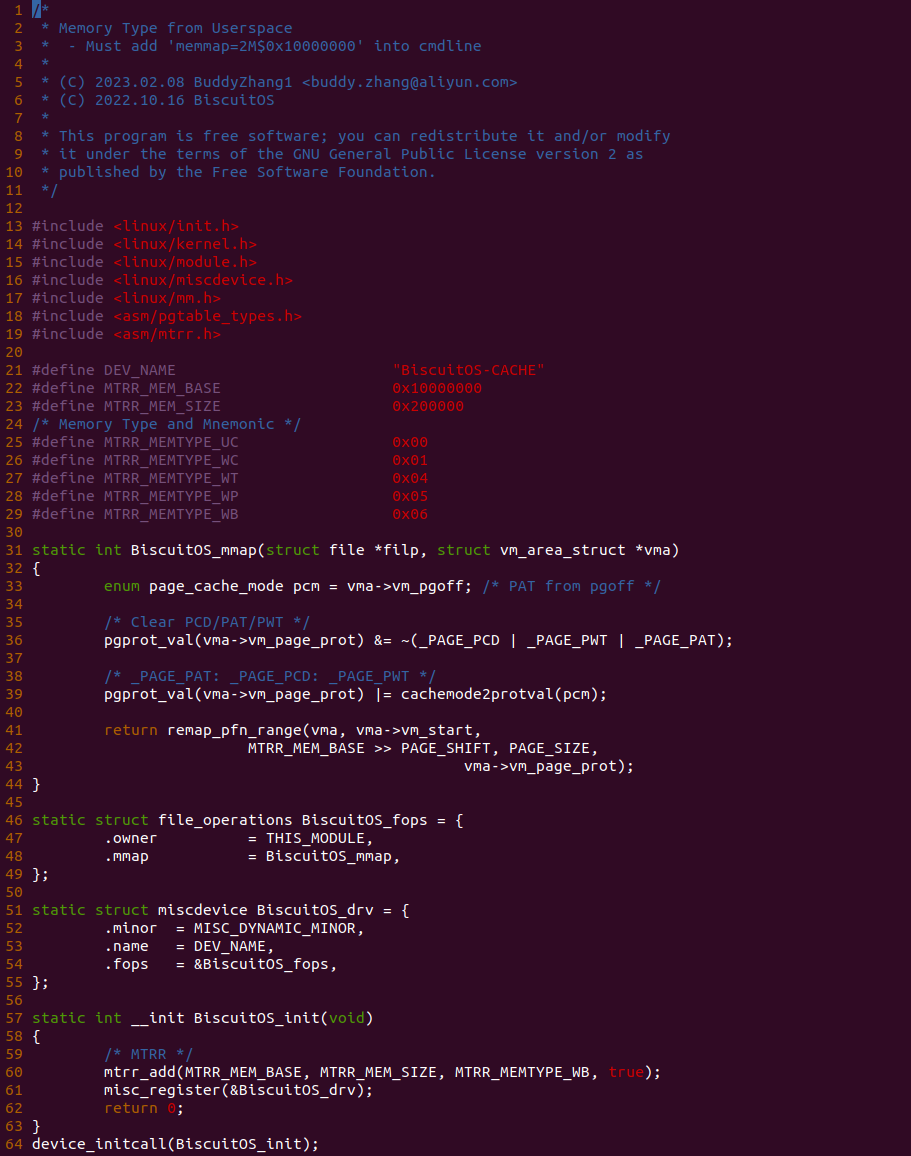

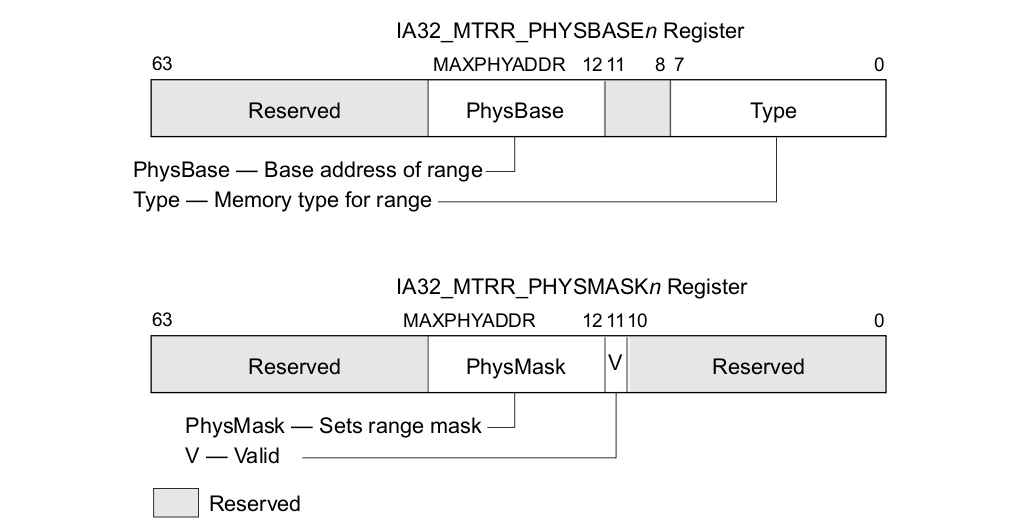

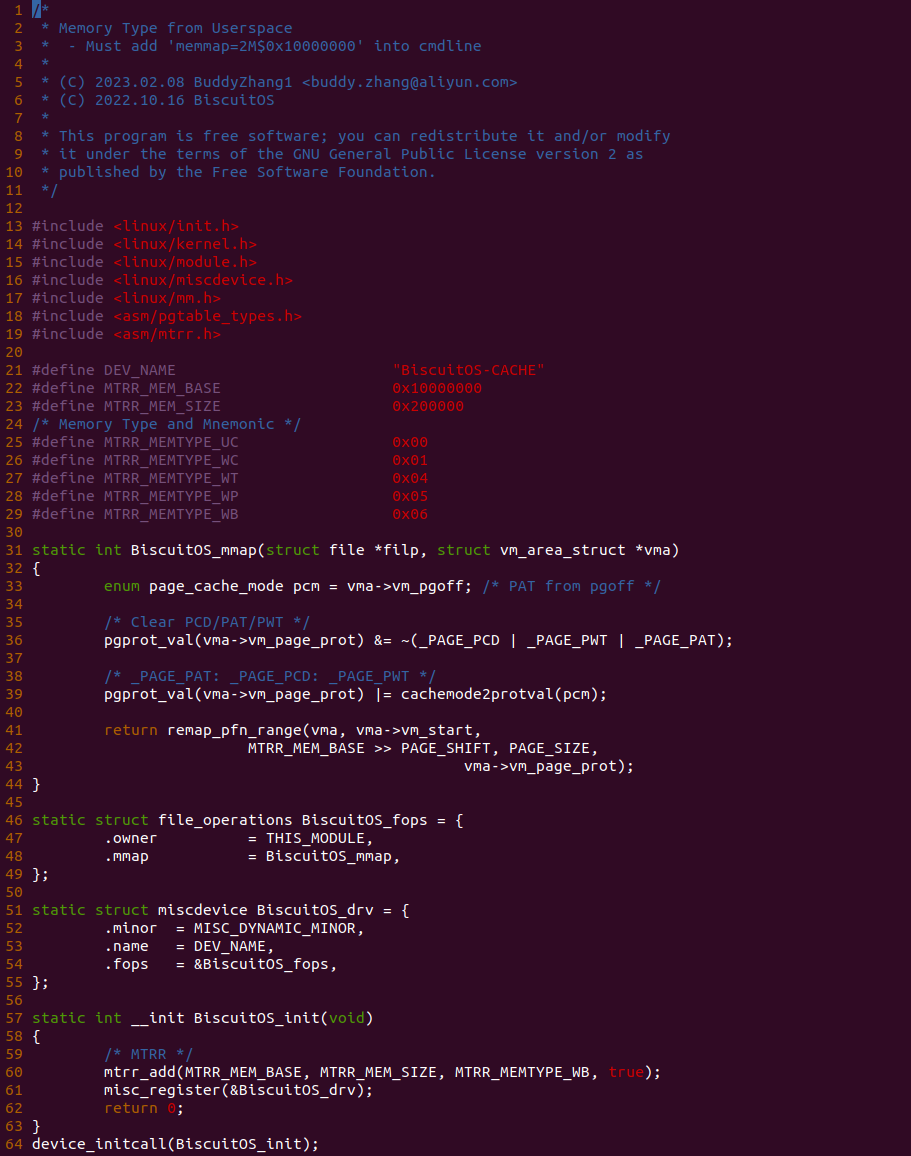

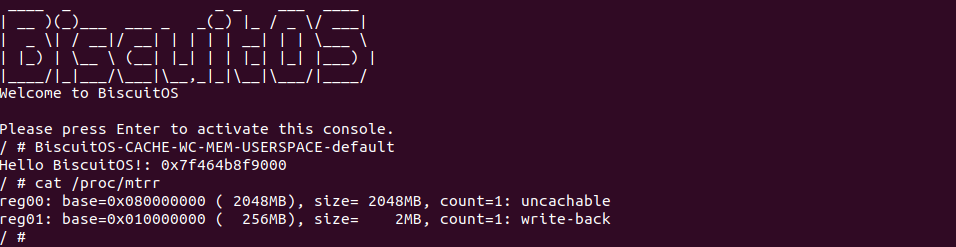

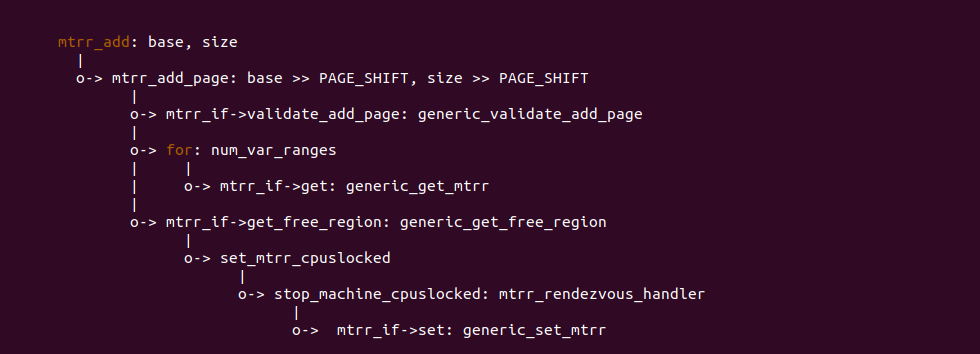

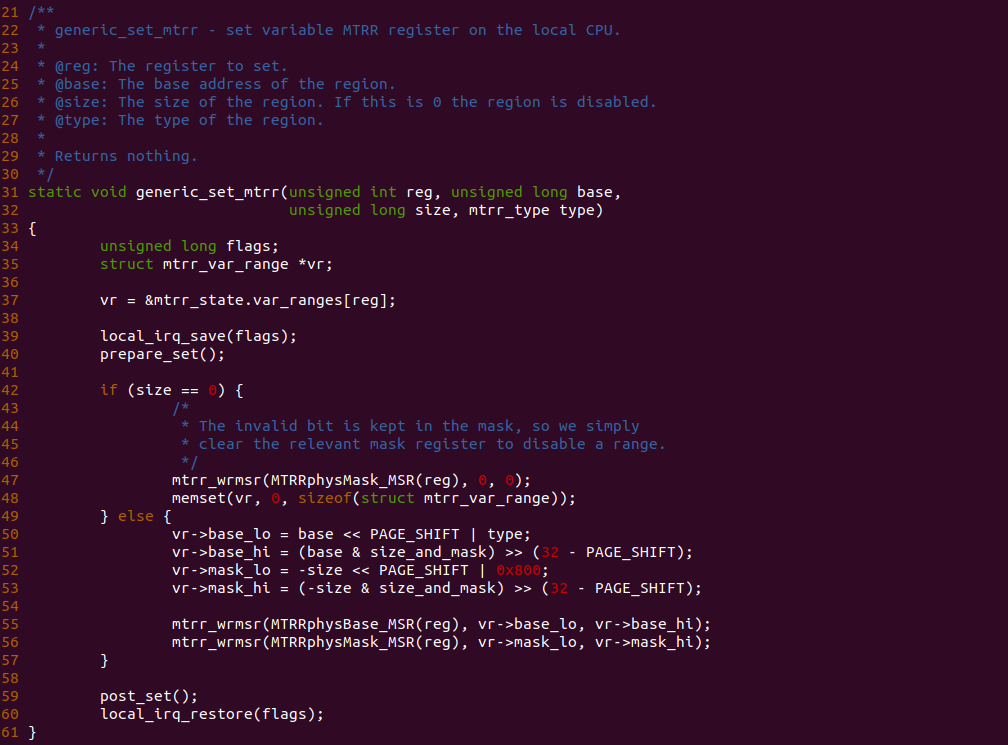

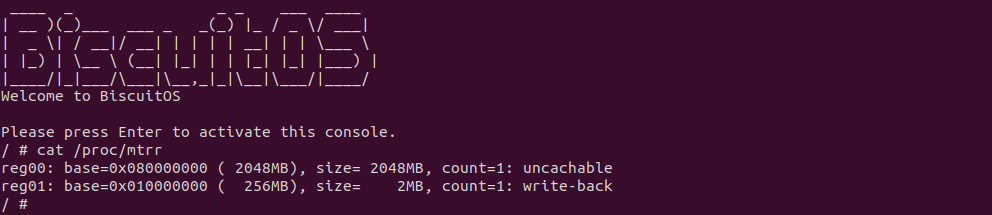

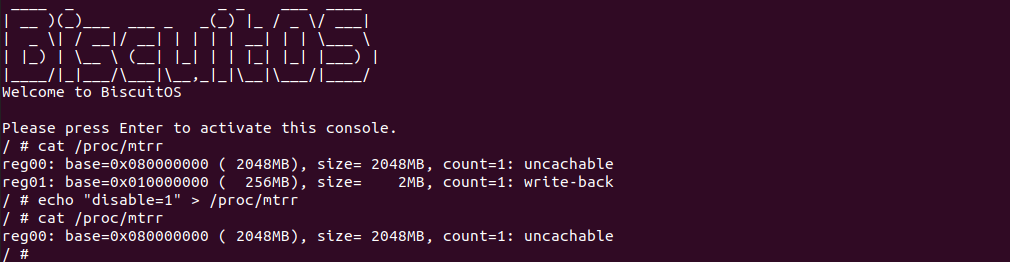

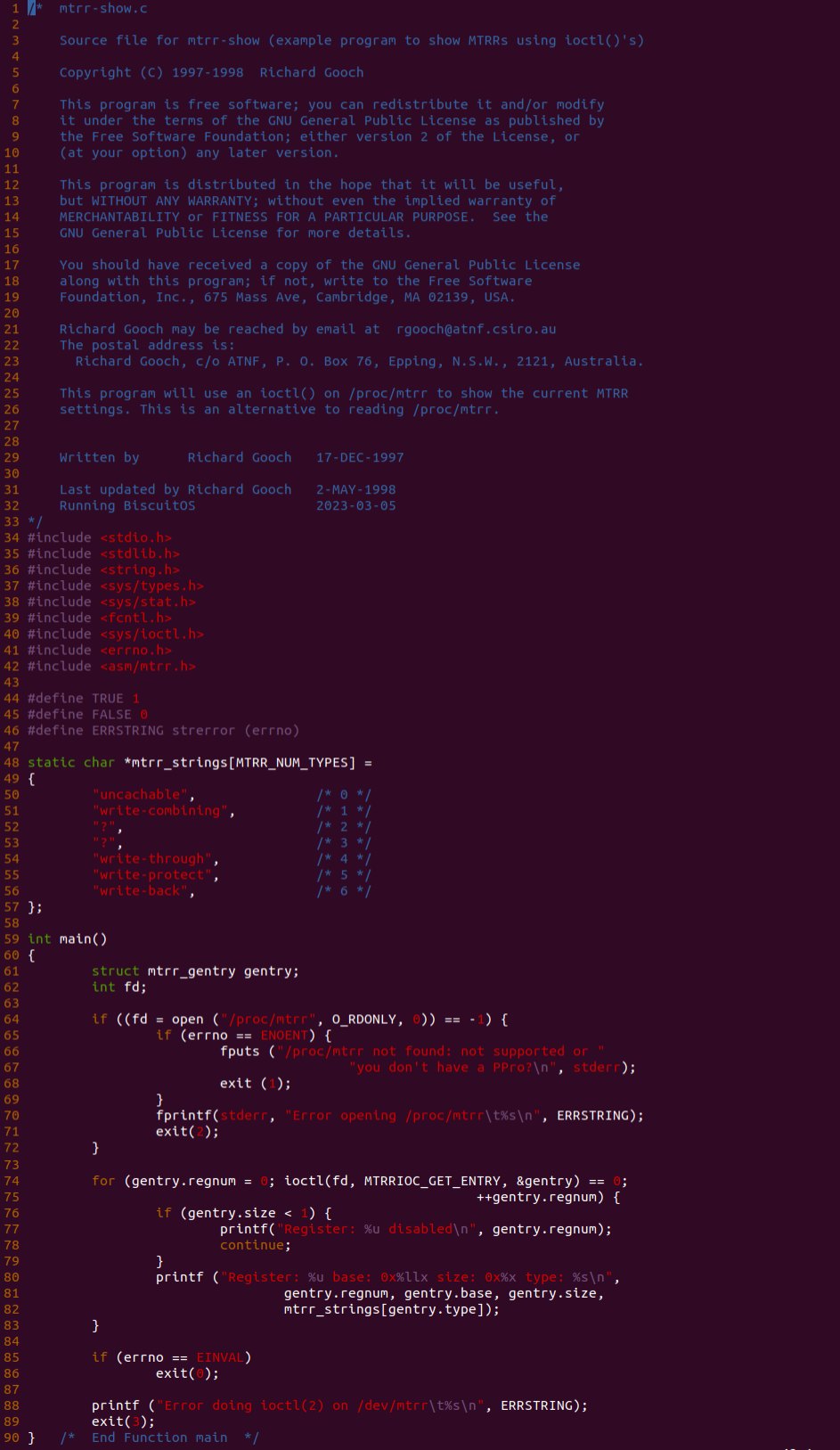

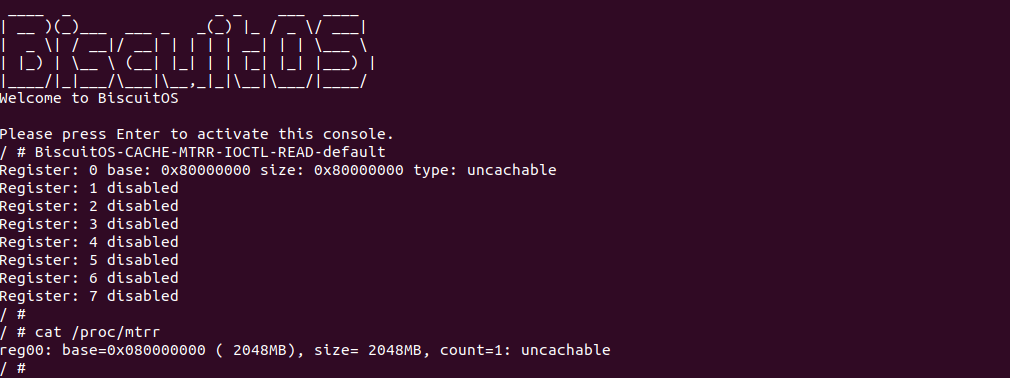

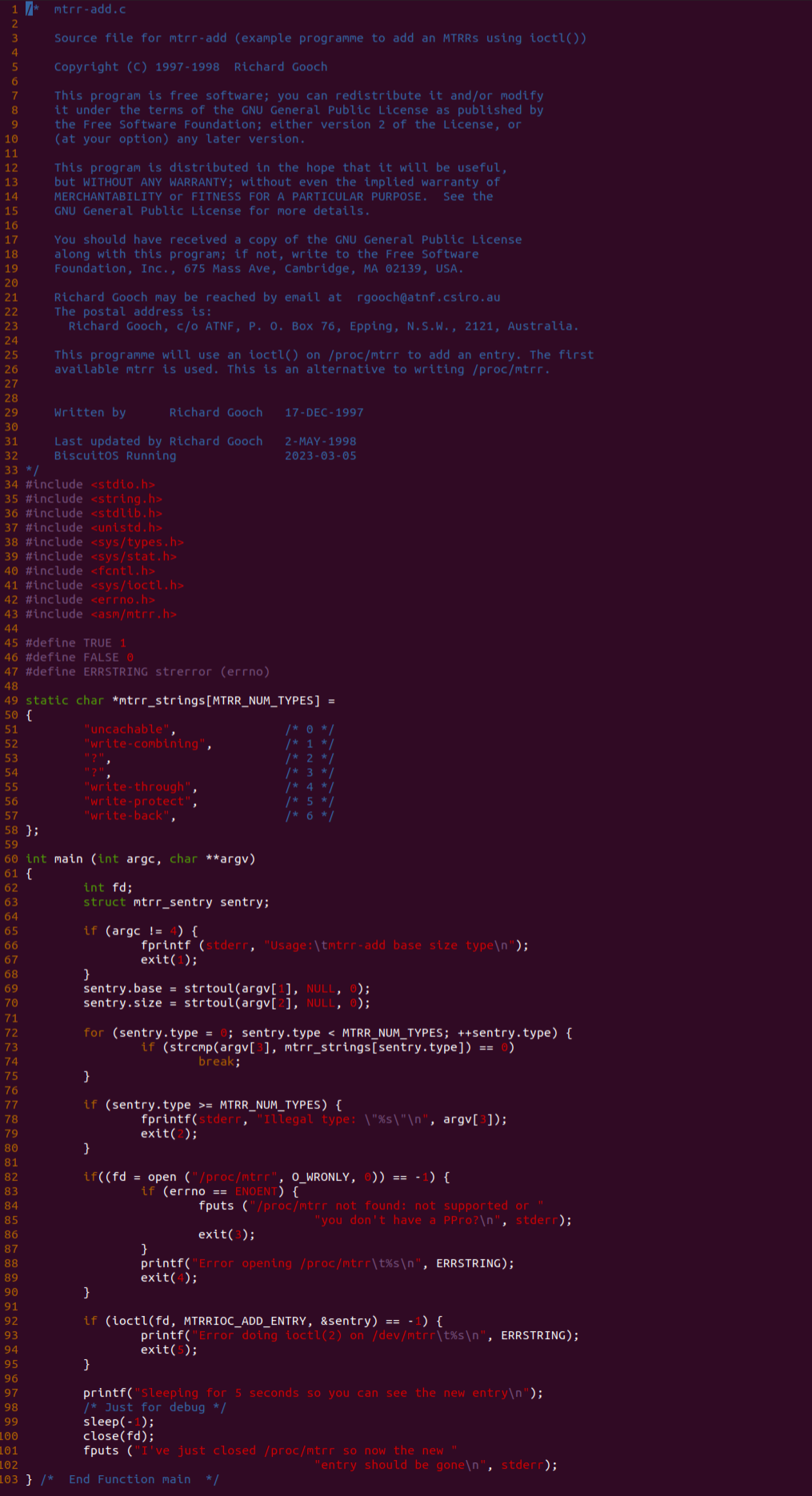

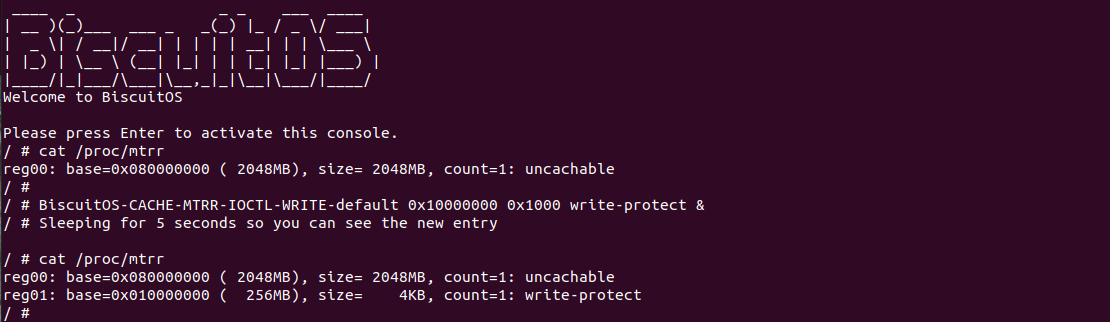

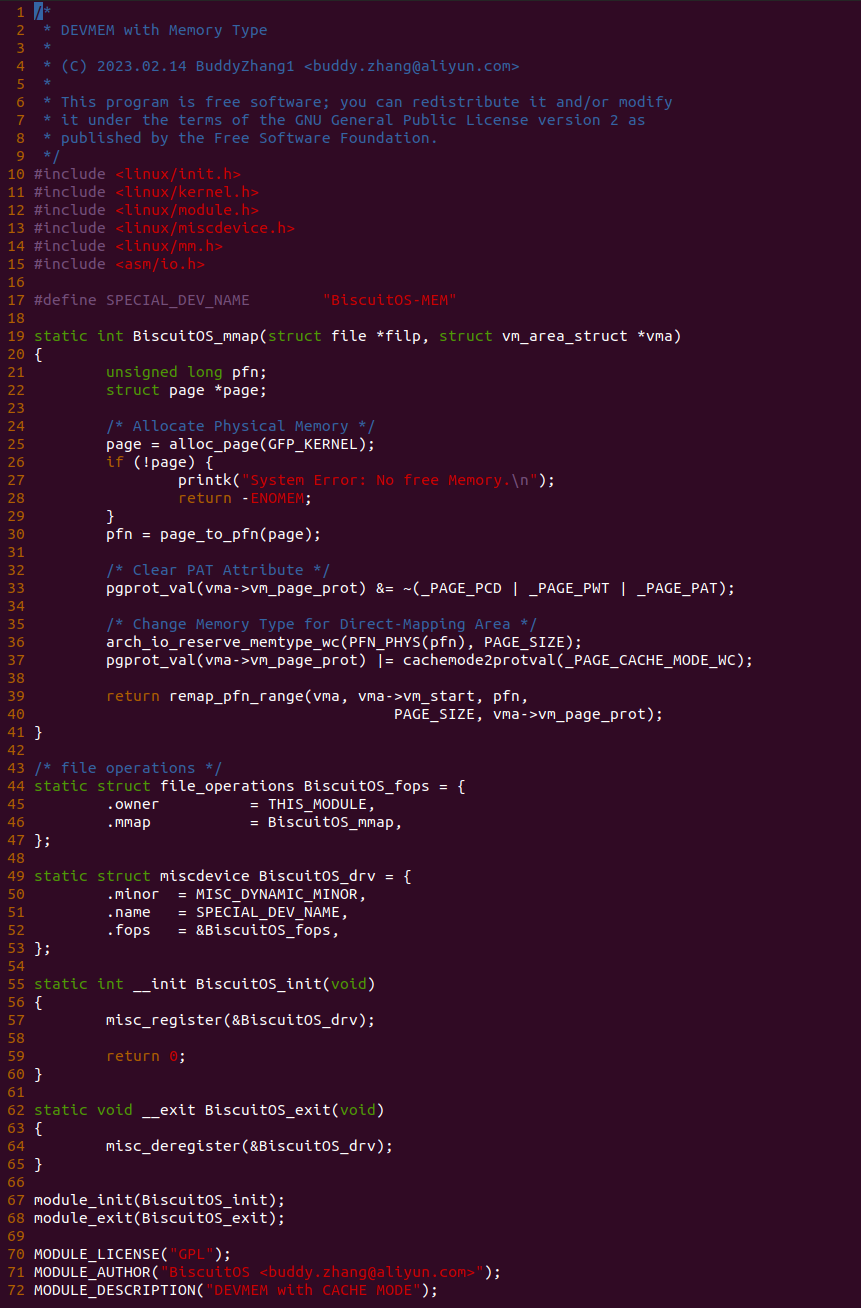

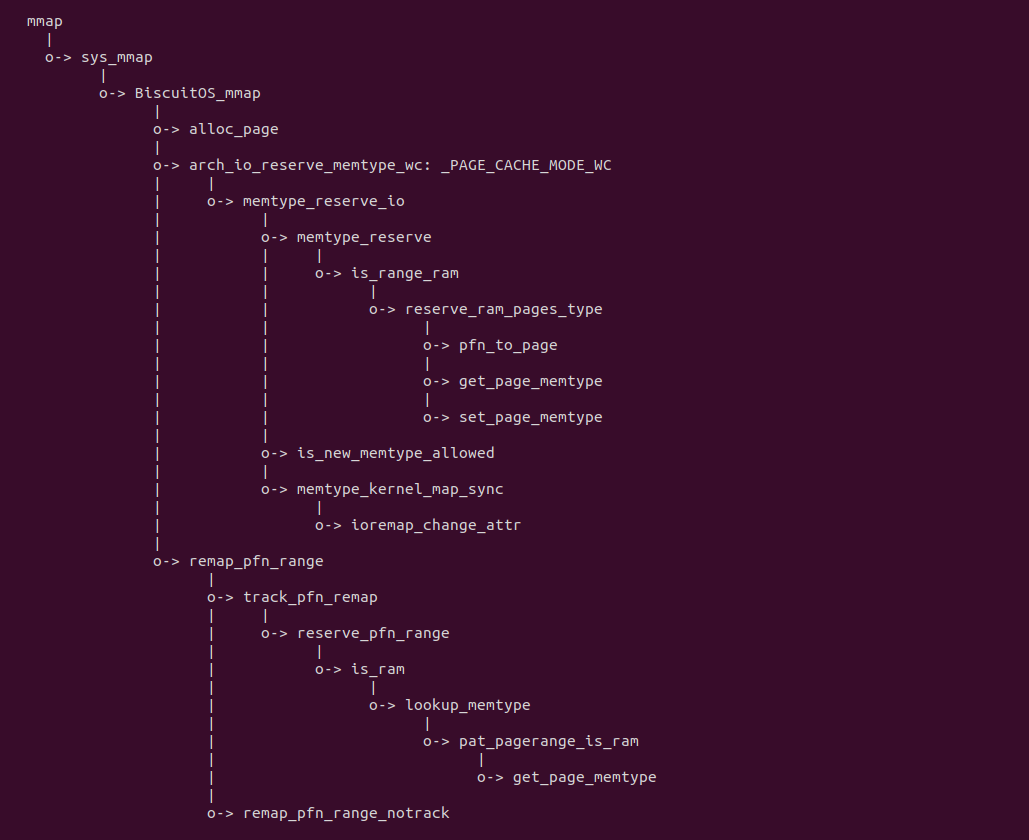

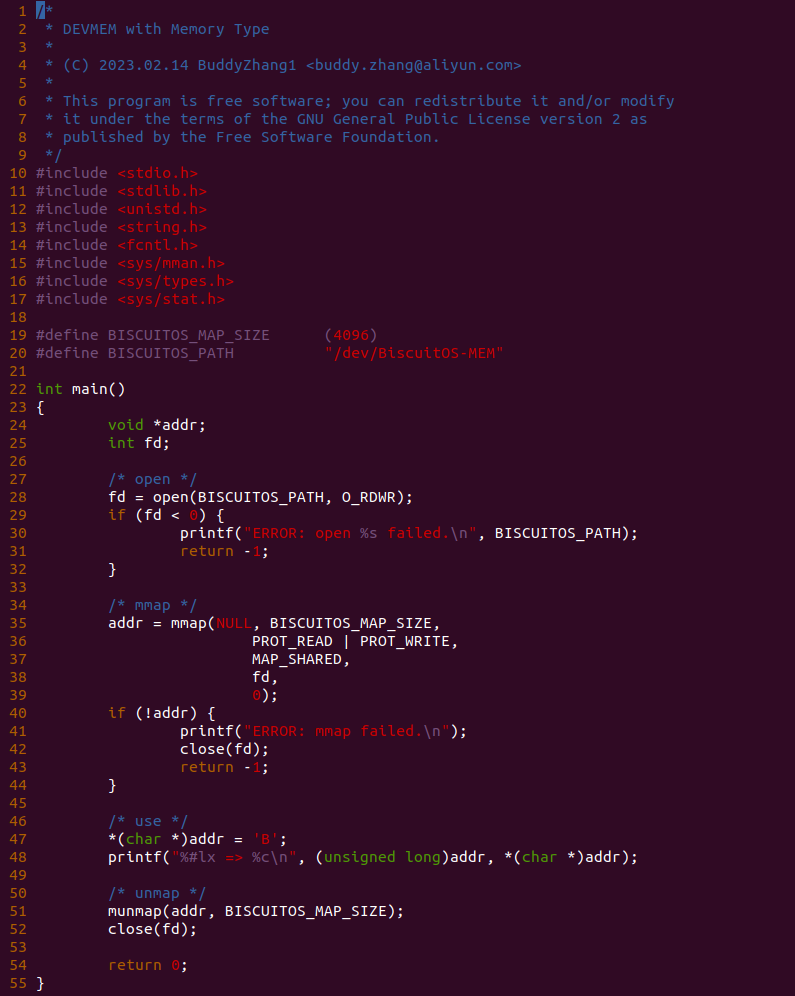

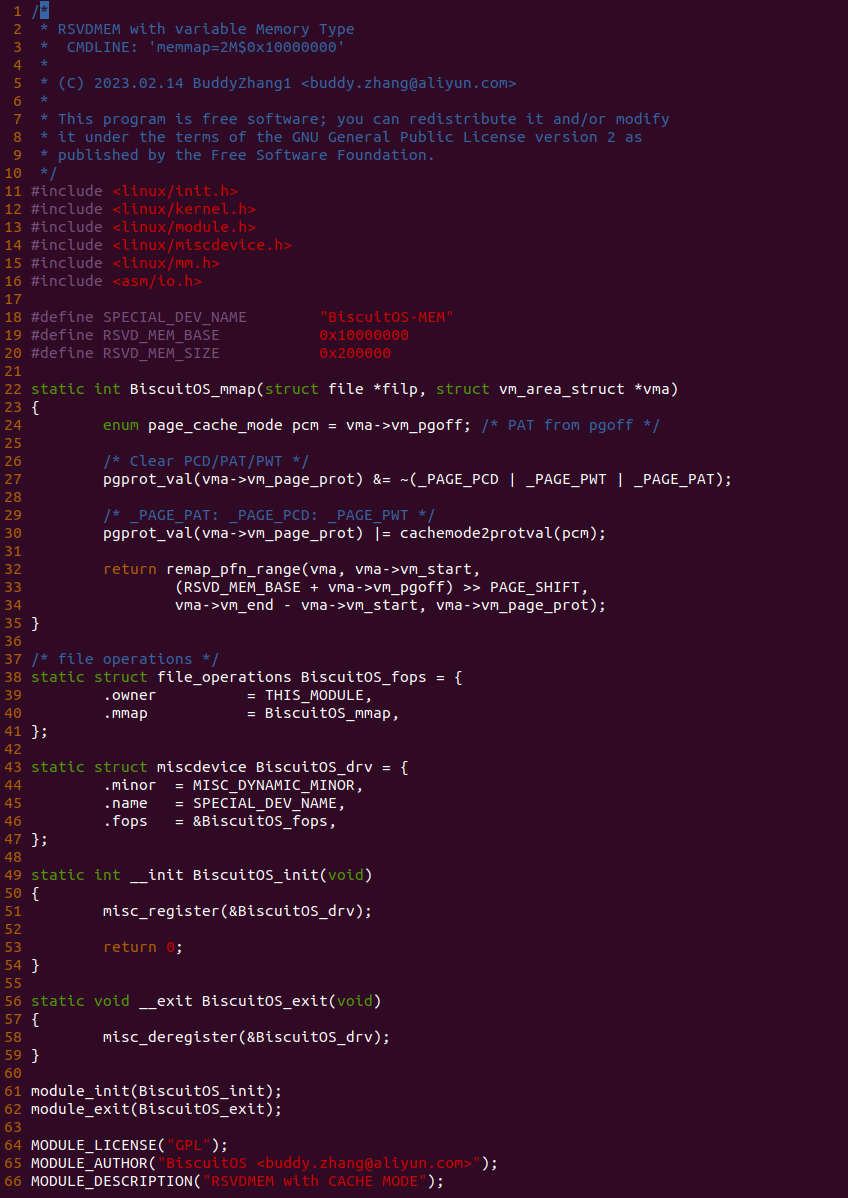

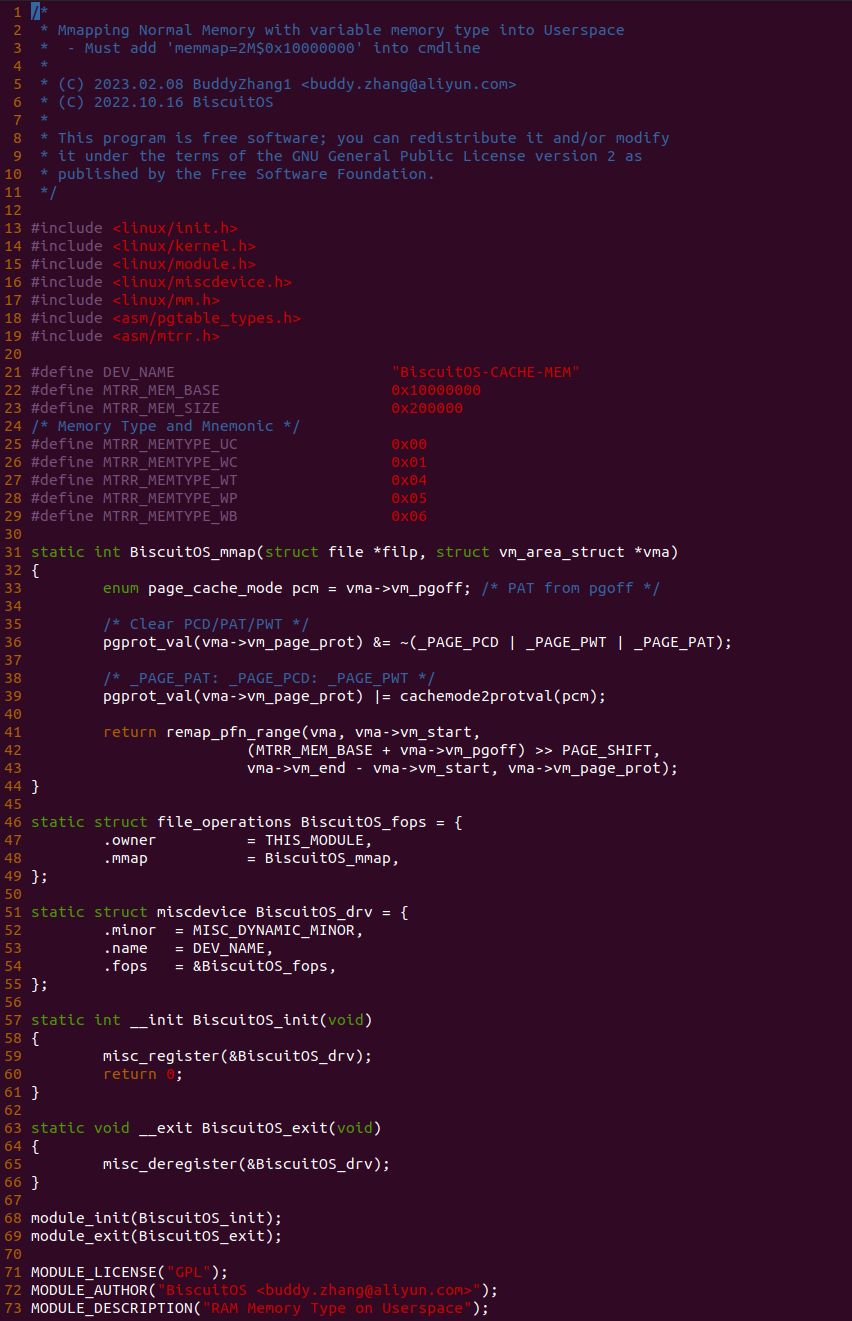

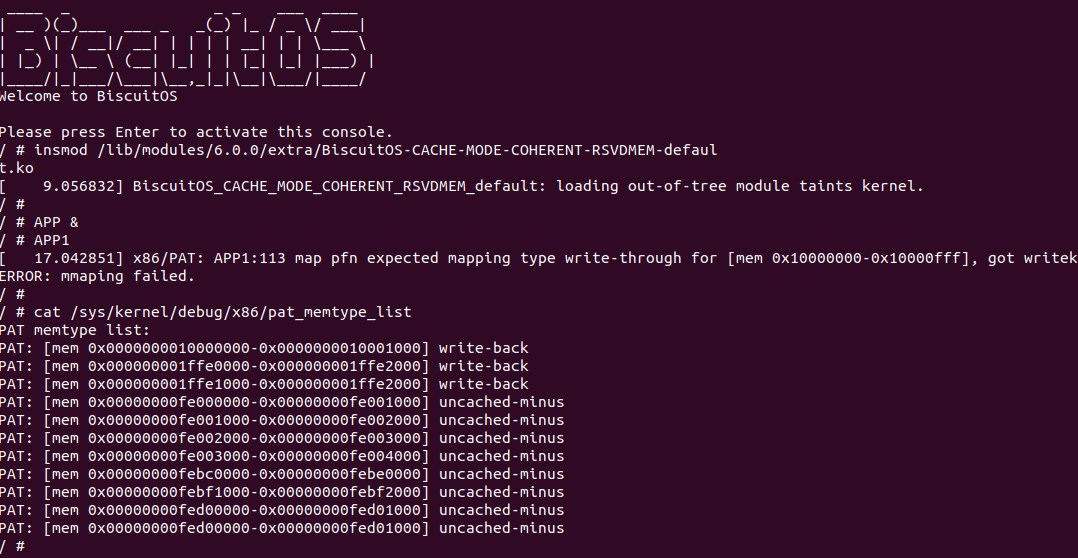

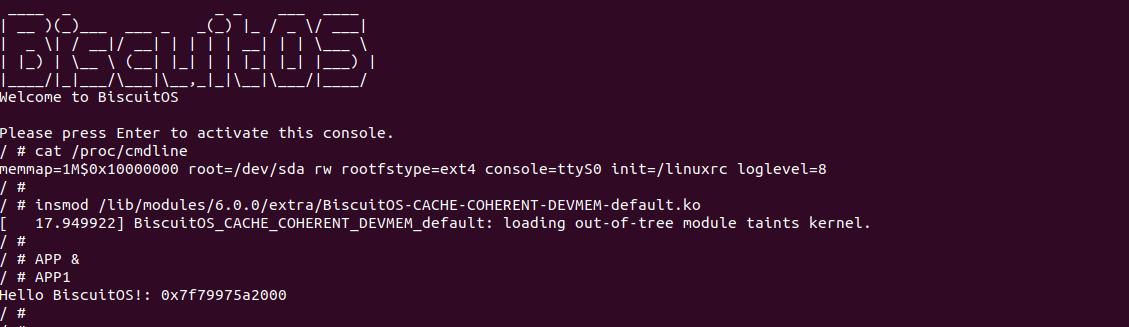

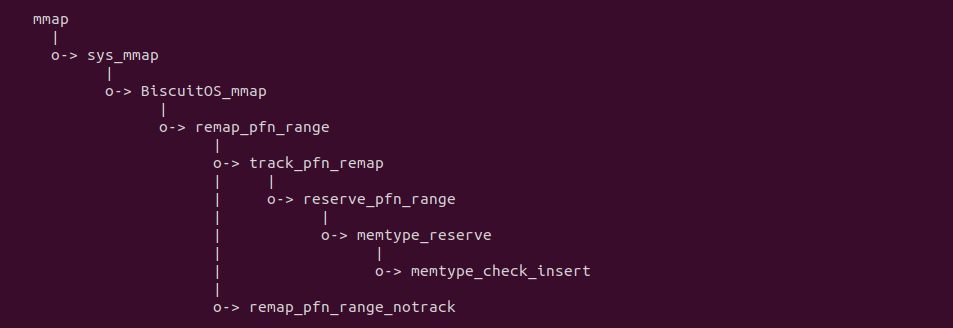

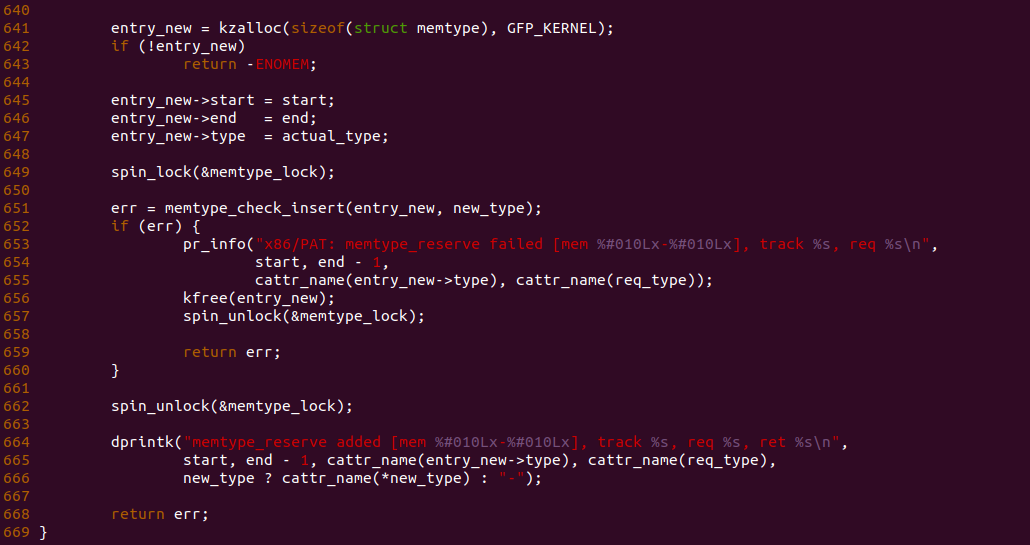

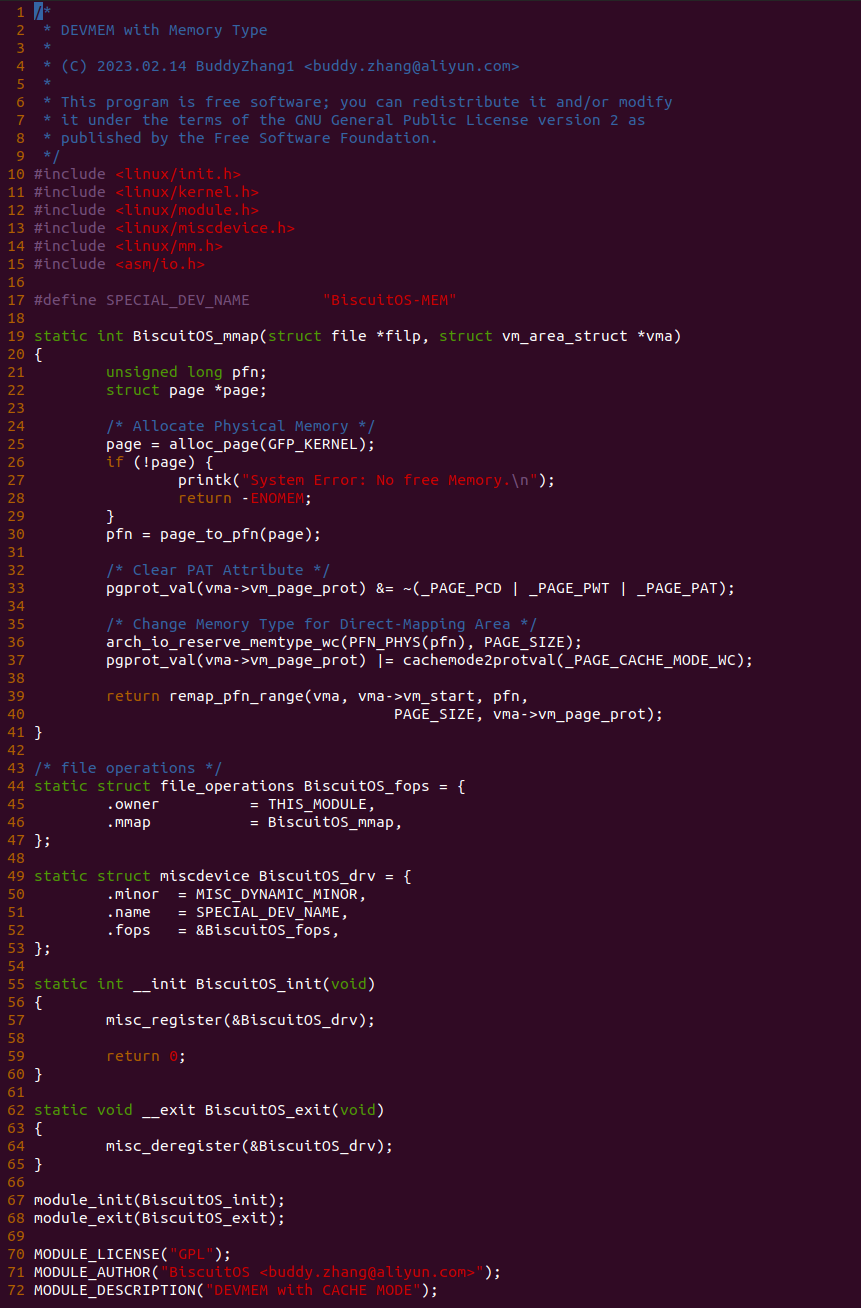

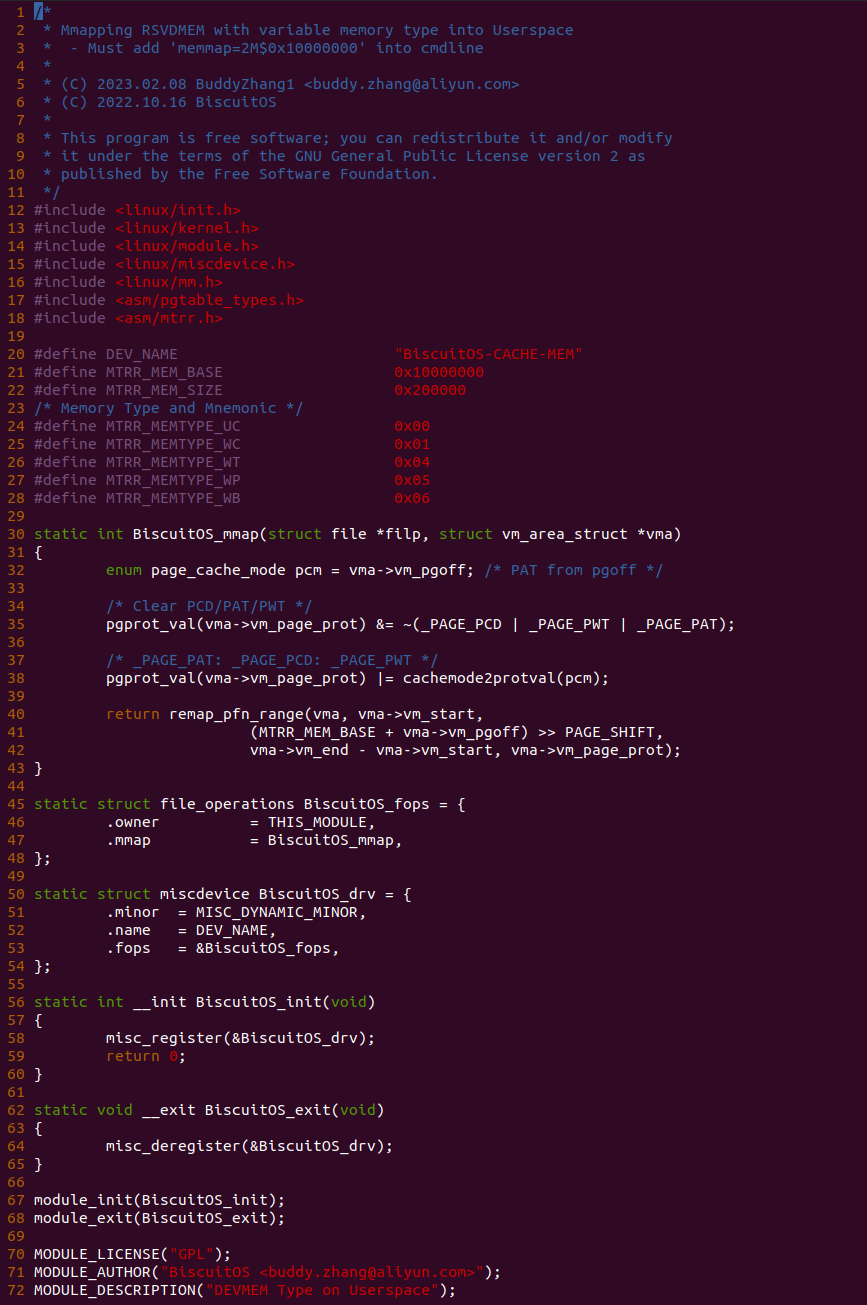

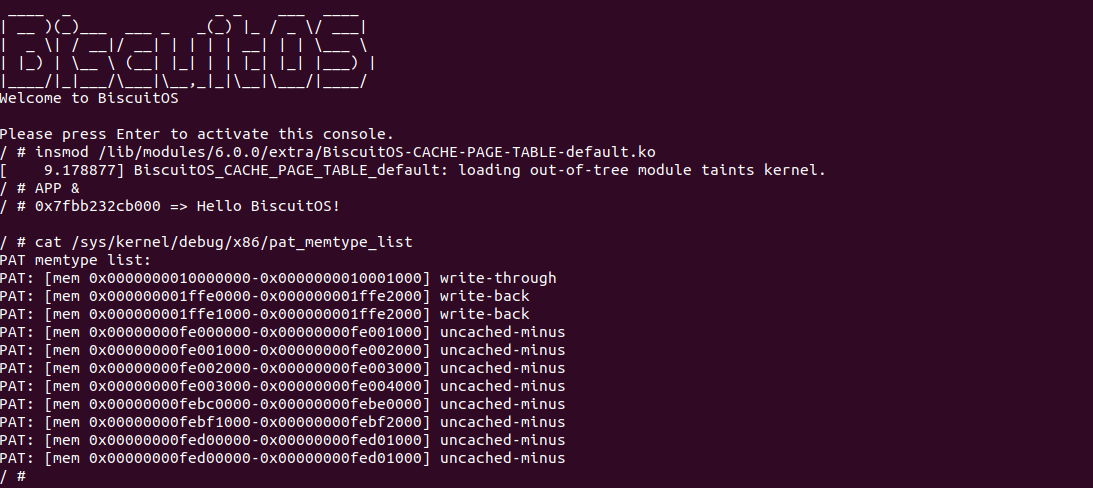

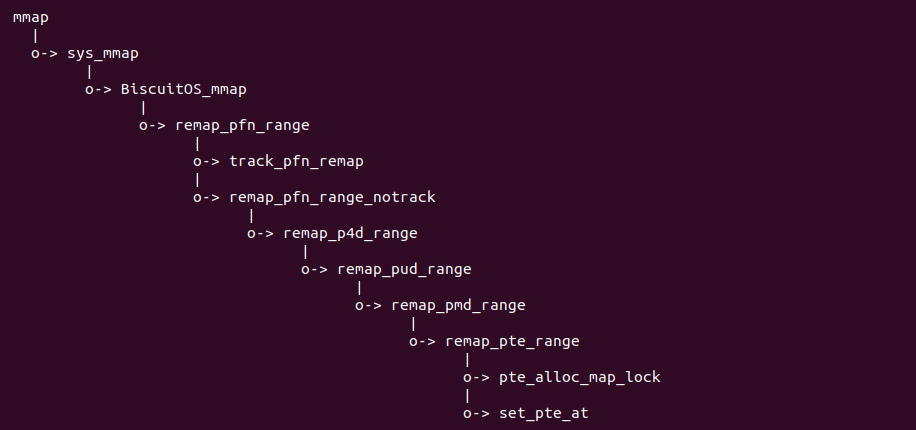

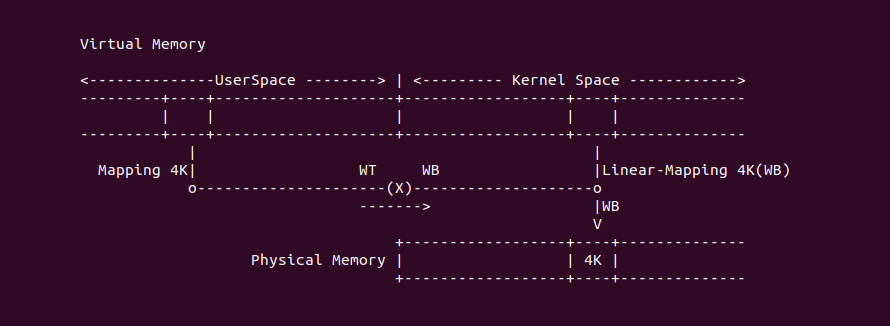

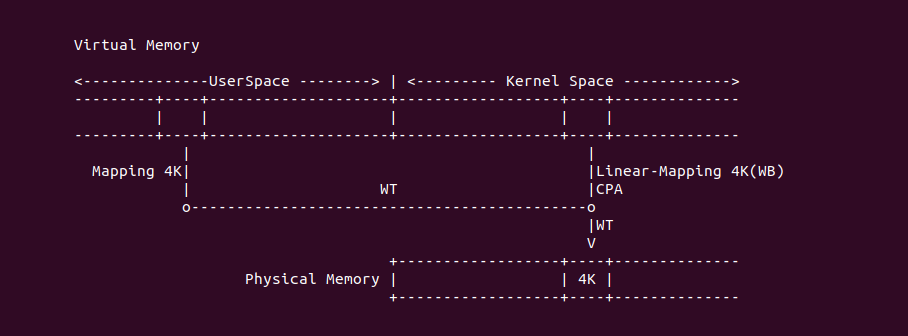

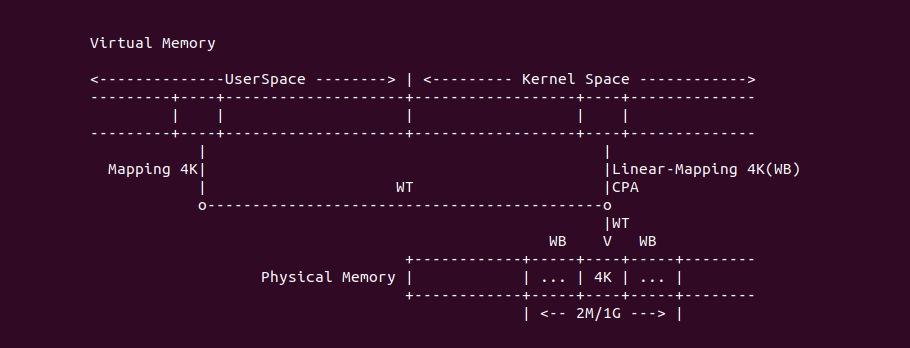

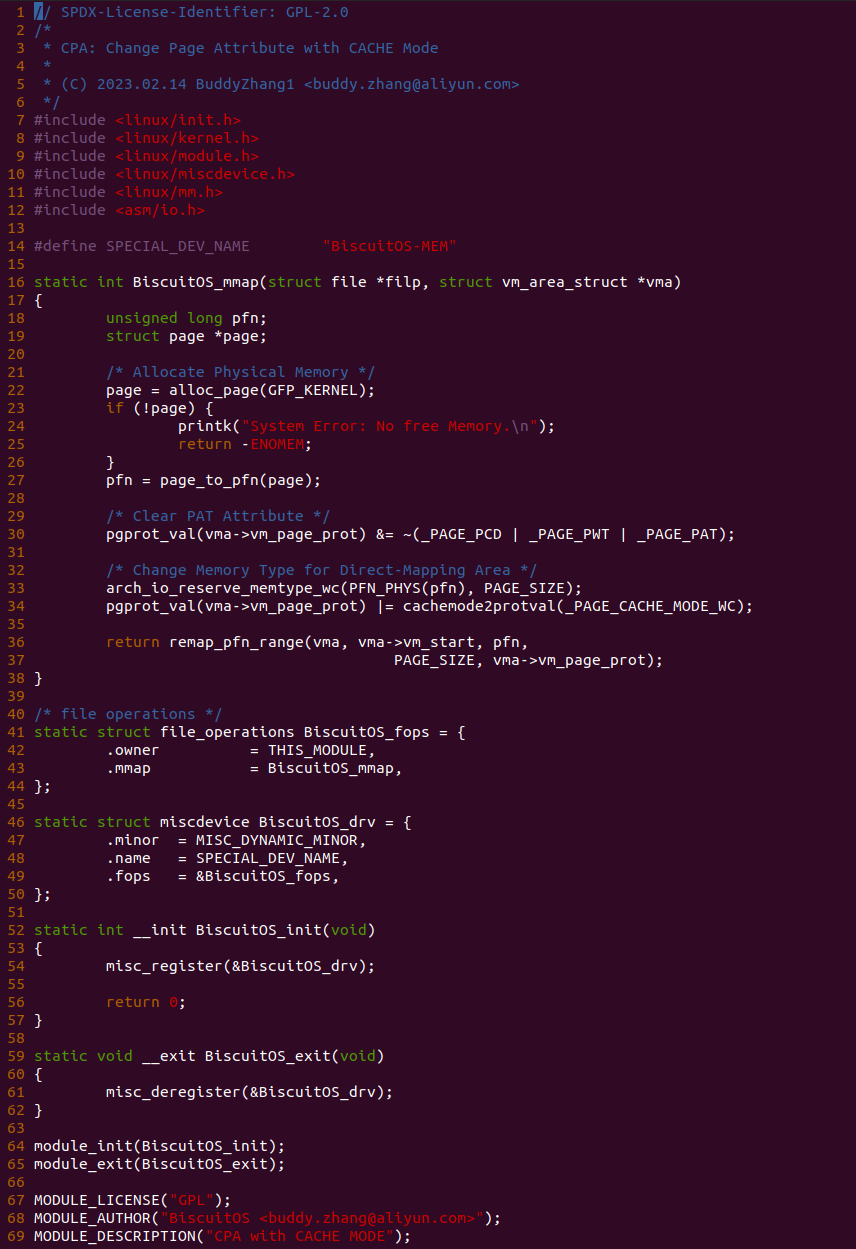

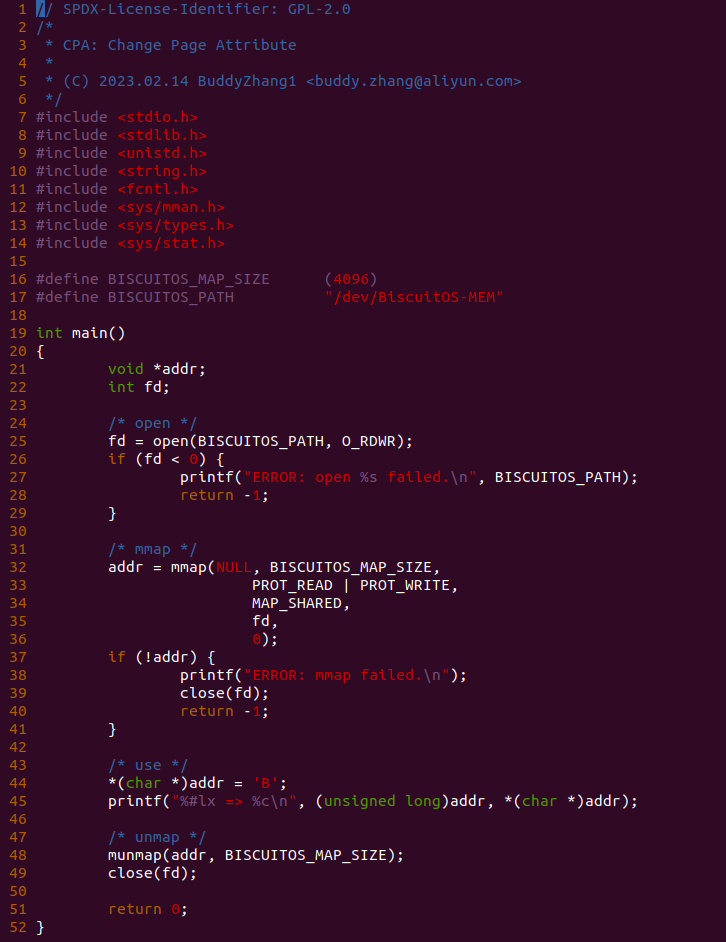

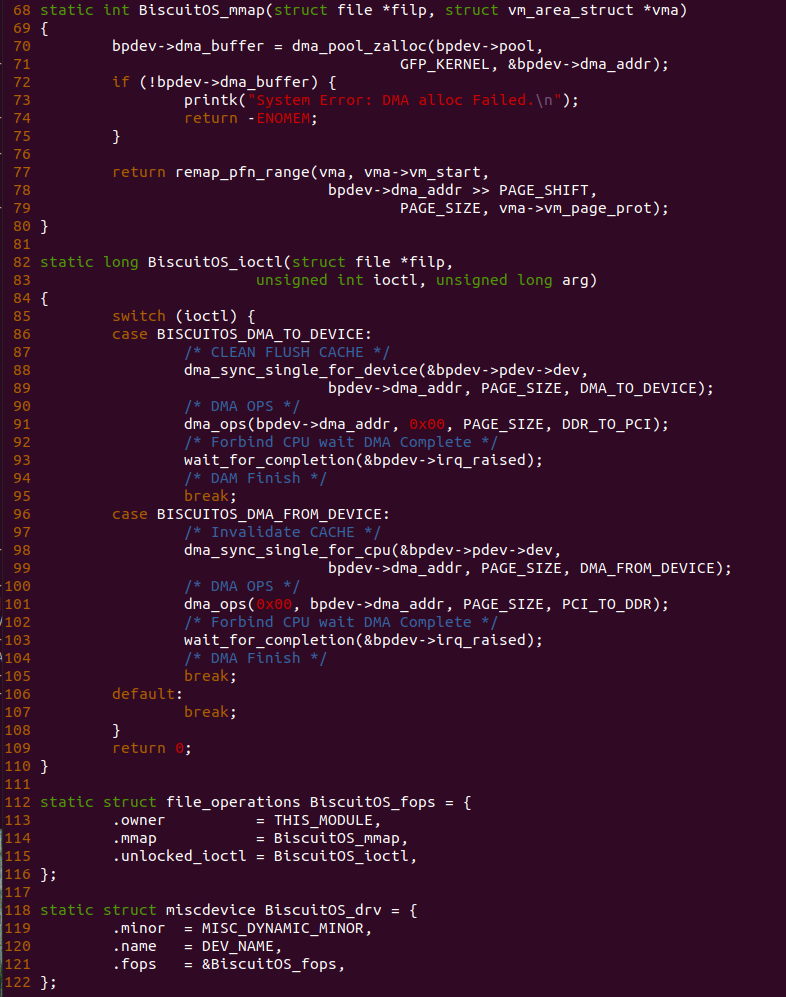

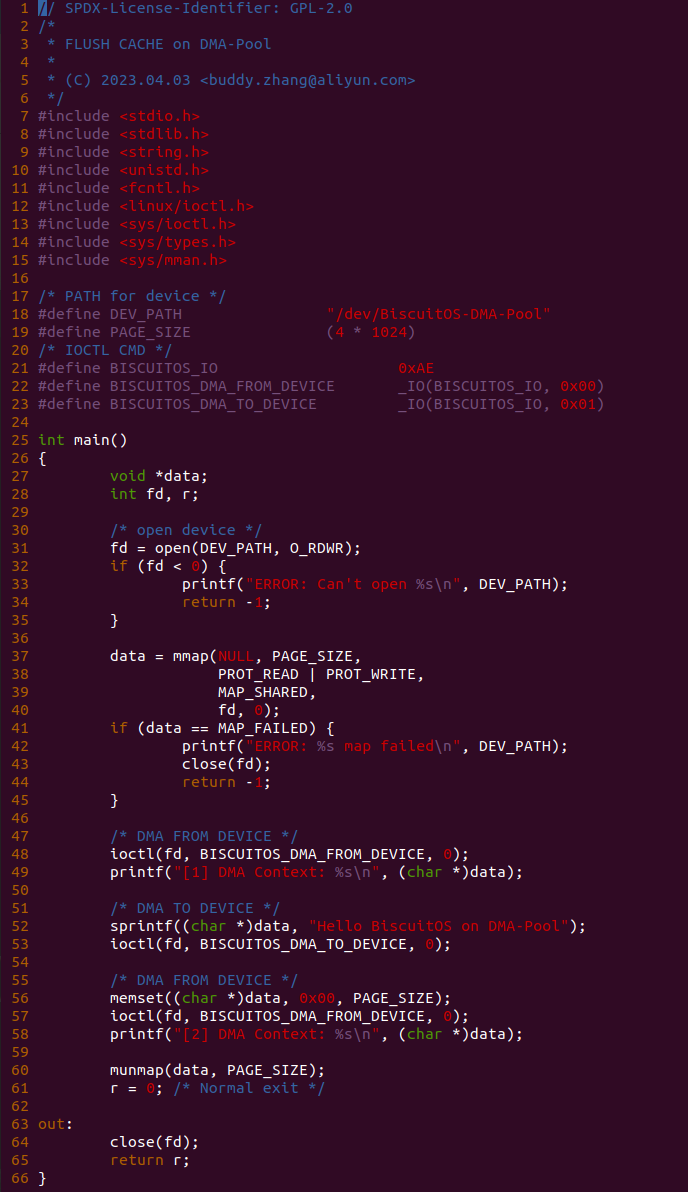

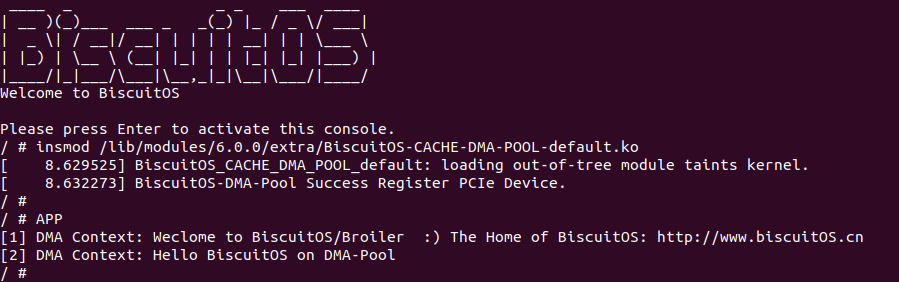

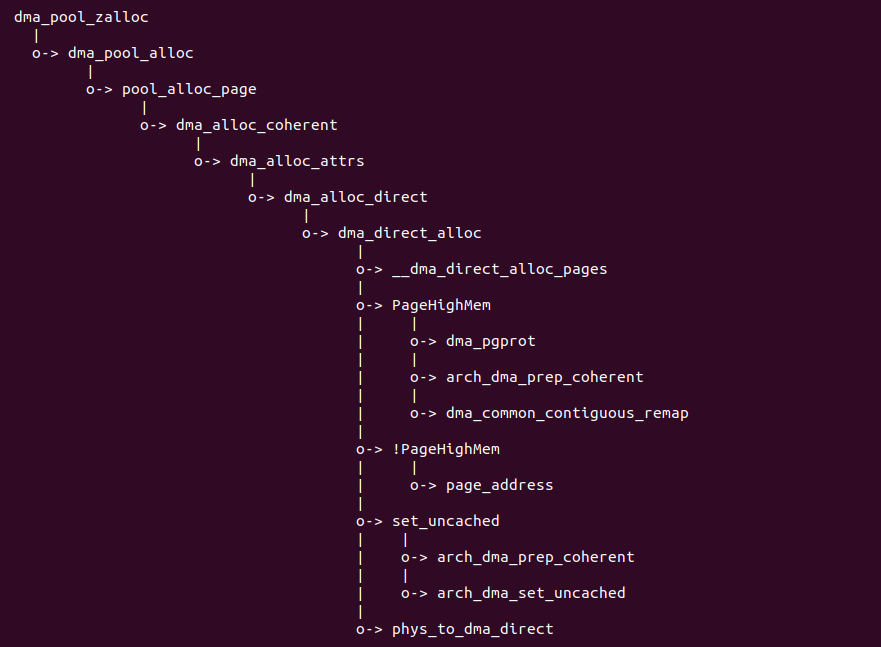

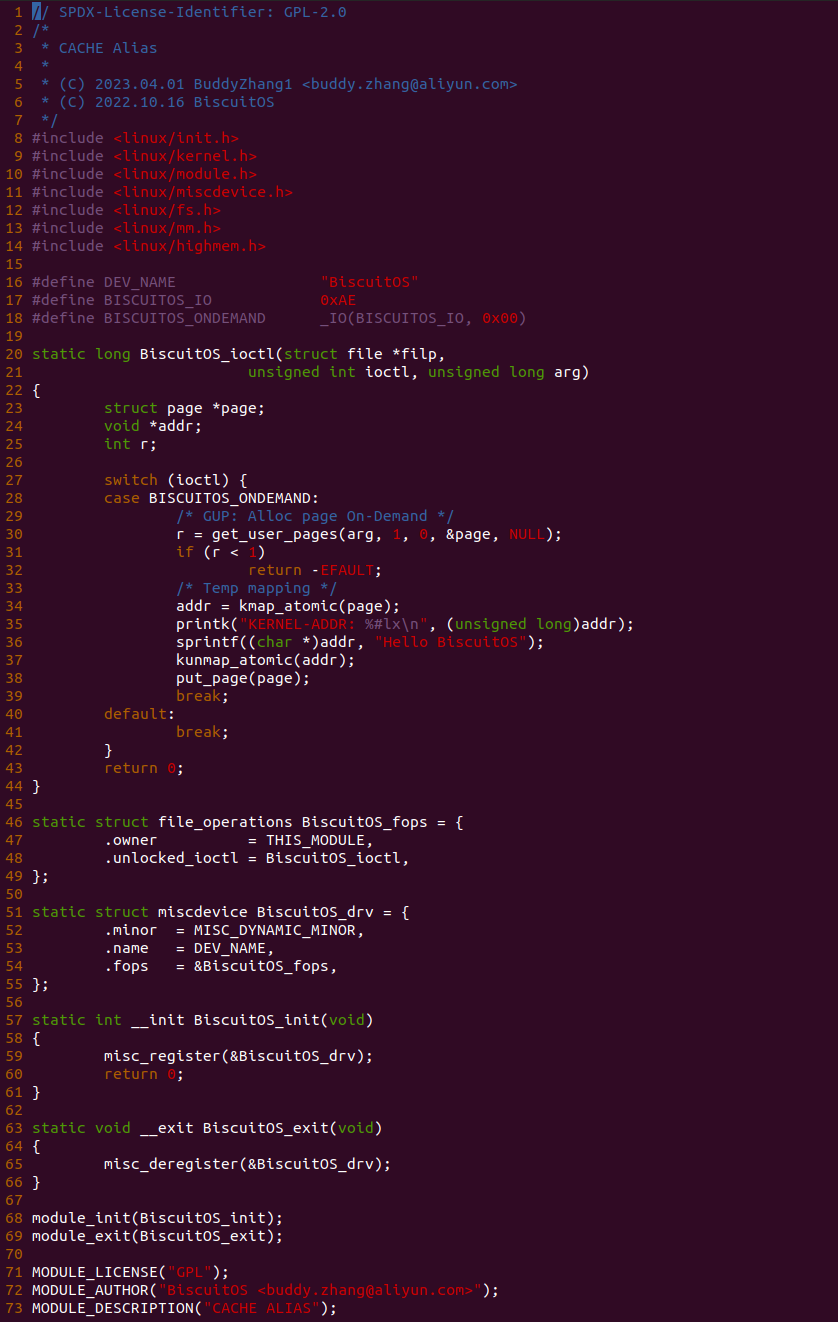

源码的另外一部分位于内核空间,其主要功能是进行实际的映射任务。模块通过一个 MISC 驱动进行实现,其提供了 mmap 接口 BiscuitOS_mmap(), 当用户空间基于 “/dev/BiscuitOS-CACHE” 节点调用 mmap() 函数时,BiscuitOS_mmap() 函数就会别调用。模块首先在 60 行调用 mtrr_add() 函数将 [MTRR_MEM_BASE, MTRR_MEM_SIZE + MTRR_MEM_BASE) 区域的 MTRR 设置为 WB. 模块接着在 33 行在用户空间调用 mmap() 函数时从 vma 的 vm_pgoff 成员中获得 PAGE CACHE MODE 信息,接着在 36 行将 vma_page_prot 成员中移除 _PAGE_PCD、_PAGE_PWT 和 _PAGE_PAT 属性,并在 39 行调用 cachemode2protval() 函数将 PAGE CACHE MODE 转换成对应的页表属性,并重新存储到 vma 的 vm_page_prot, 以此作为用于空间设置的 memory type 页表属性,最后模块在 41 行调用 remap_pfn_range() 函数为虚拟内存建立页表并映射到 MTRR_MEM_BASE 对应的物理内存上. 接下来在 BiscuitOS 上实践该案例:

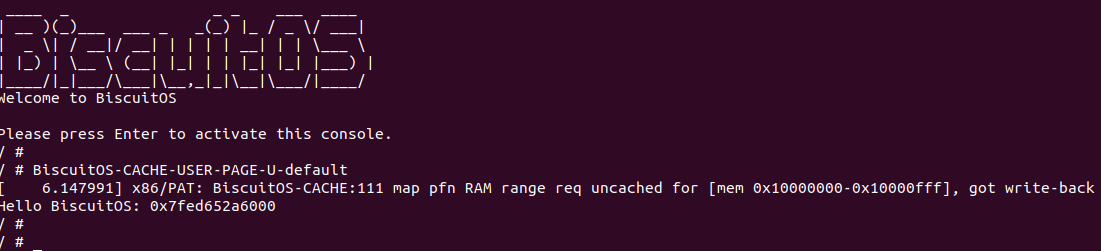

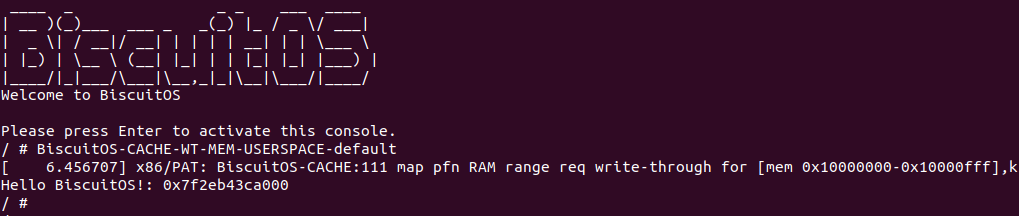

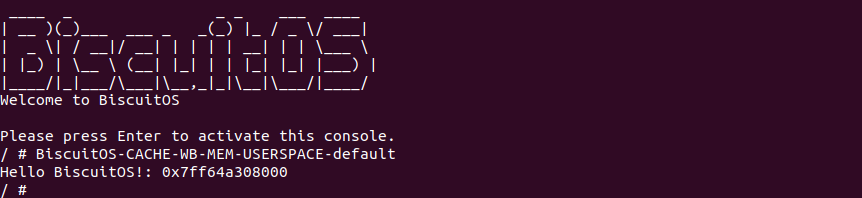

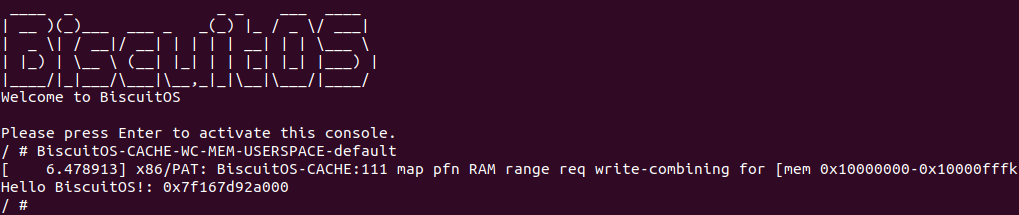

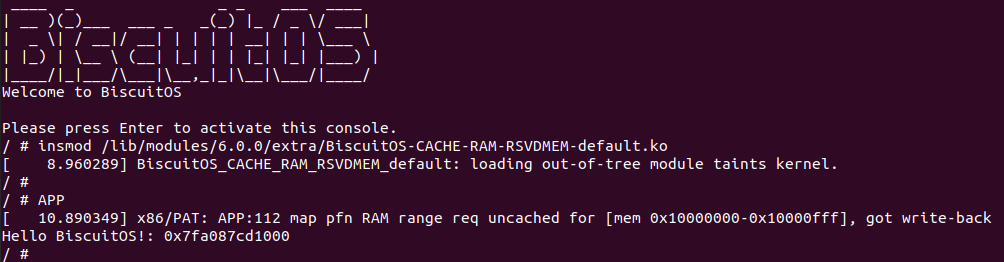

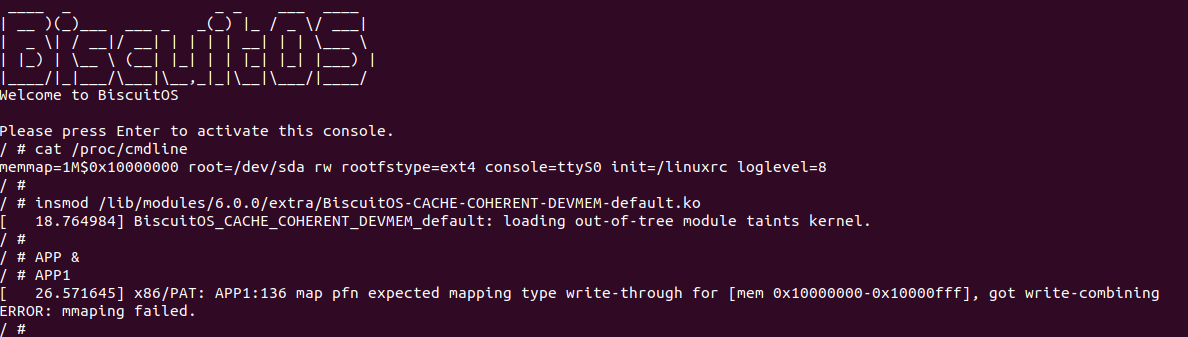

BiscuitOS 运行之后, 执行应用程序 BiscuitOS-CACHE-USER-PAGE-U-default,此时系统提示了程序预期将 [0x10000000-0x10000fff] 为 uncached,但是系统还是将对应的 memory type 设置为 write-back, 这个与预期不符合. 查看内核模块源码的 3 行提示需要将 [0x10000000, 0x10200000) 进行预留,那么在 CMDLINE(CMDLINE 位于 RunBiscuitOS.sh 文件中) 中添加预留字段后再次实践:

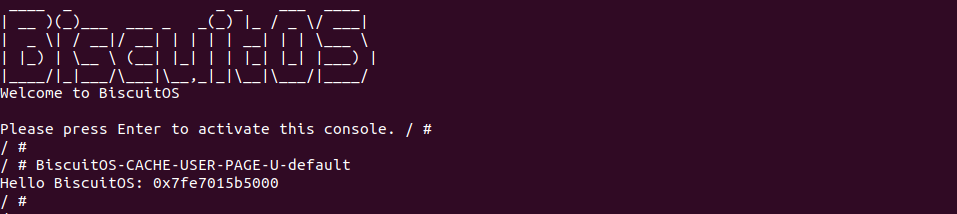

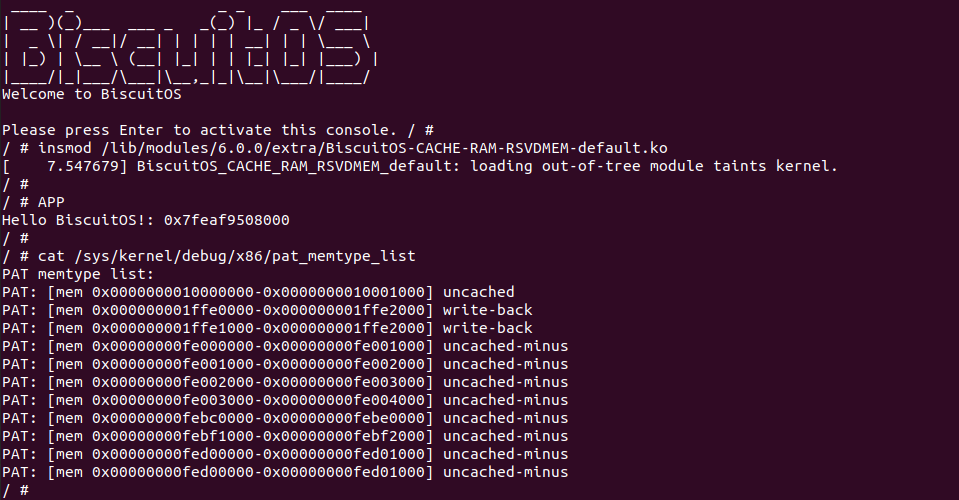

BiscuitOS 在次运行之后,运行应用程序,可以看到系统没有再提示修改信息了,那么用户进程已经成功将一段物理内存的 memory type 设置为 UC. 实践符合预期,那么接下来实践内核空间虚拟地址映射 UC 物理内存:

内核空间虚拟内存映射 UC 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] UNCACHE(UC): Mapping UC Memory on Kernel --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-UNCACHE-MEM-KERNEL-default/

# 部署源码

make download

# 在 BiscuitOS 中实践

make buildBiscuitOS-CACHE-UNCACHE-MEM-KERNEL-default Source Code on Gitee

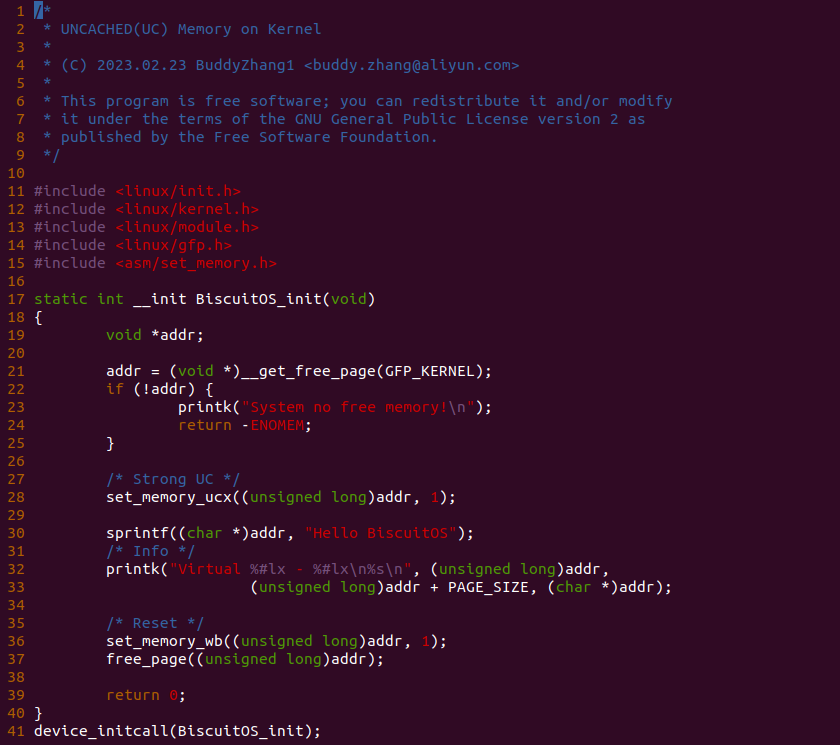

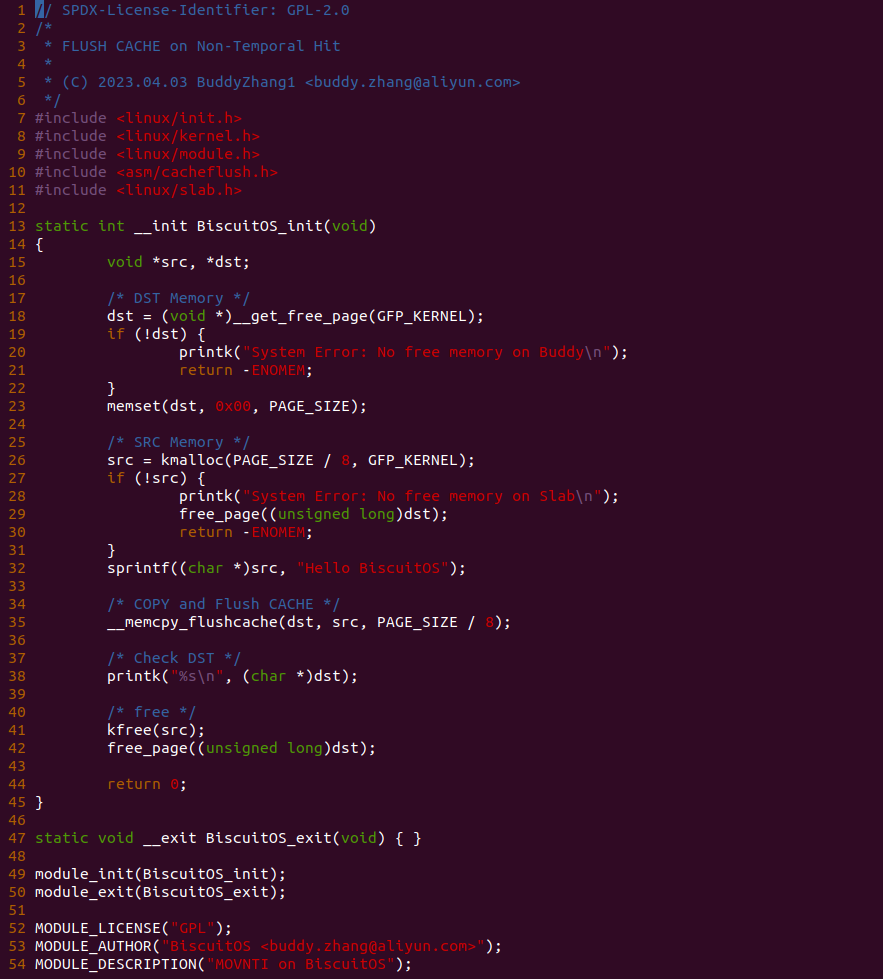

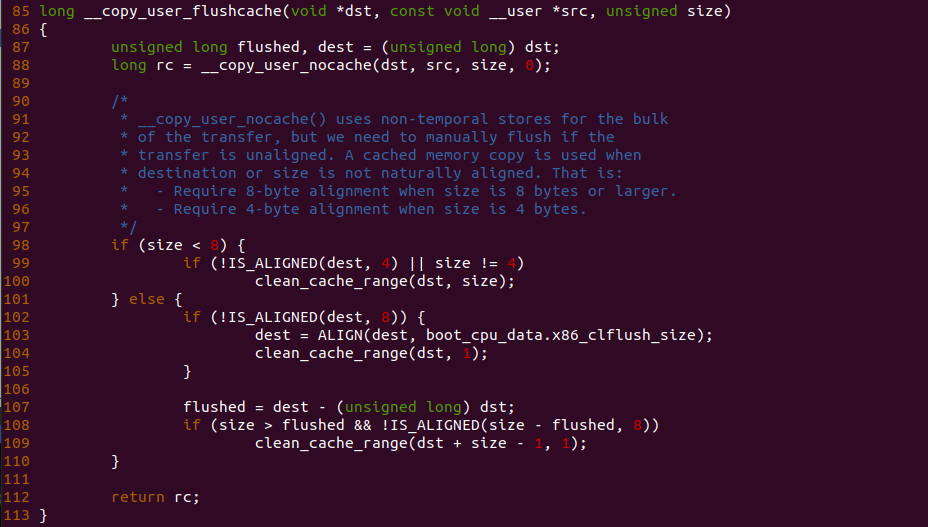

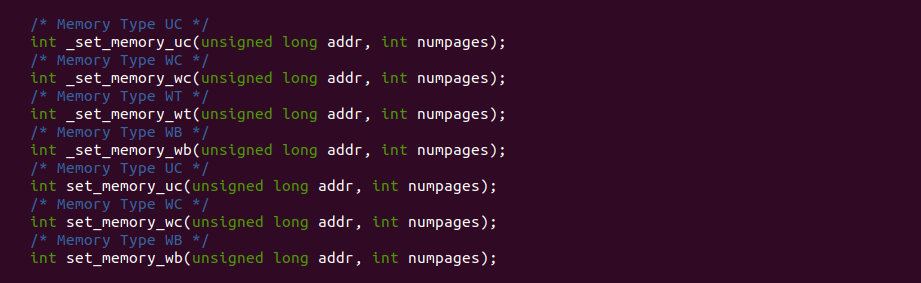

实践案例主要目的是在内核空间申请一段内存之后,将对应的虚拟地址以 UC 的方式映射到物理内存,并进行访问。案例在 21-25 行通过 __get_free_page() 函数分配一个物理页并获得对应的虚拟地址,然后在 28 行调用 set_memory_ucx() 函数进行 UC 方式的映射,案例接着在 30-33 行对映射之后的虚拟地址进行访问。最后在 36-37 行回收设置,值得注意的是当将内核空间虚拟地址设置为非 WB 之后,在回收时要主动设置为 WB。另外由于内核不支持 UC 映射物理内存方式,因此需要对内核进行修改,参考如下补丁:

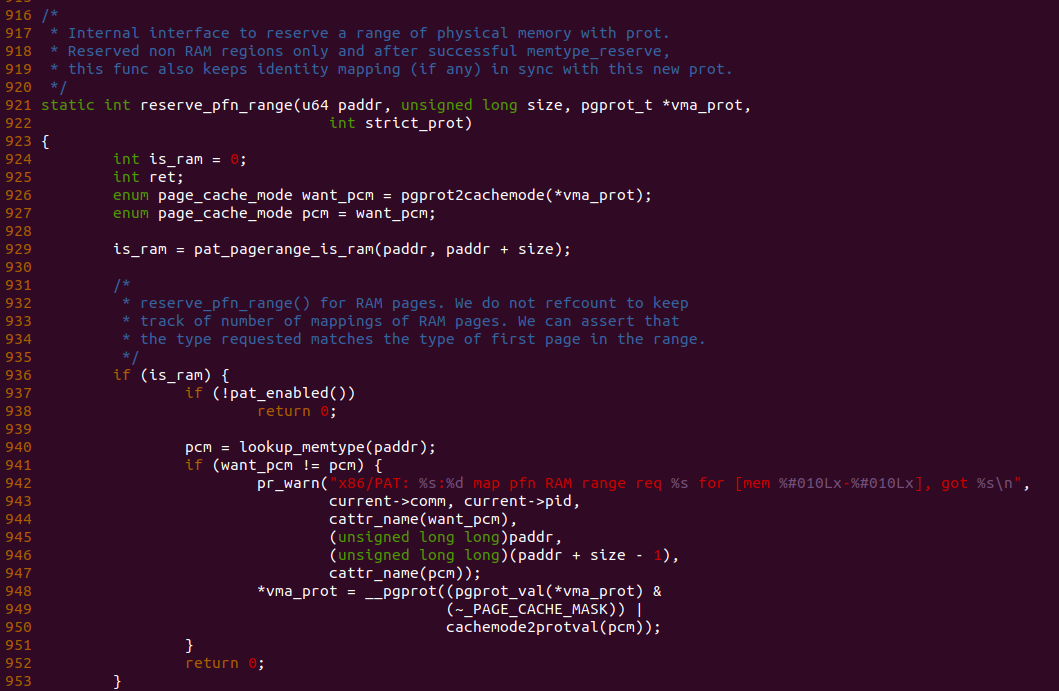

PATCH 主要做了两个事情,首先对 set_memory_ucx() 函数进行实现,然后在头文件中导出相应的函数定义,最后在 reserve_ram_page_type() 函数解除内核对 _PAGE_CACHE_MODE_UC 不支持的逻辑。接下来在 BiscuitOS 上进行实践:

BiscuitOS 运行之后查看 dmesg 可以看到映射过程,由于没有合入 reserve_ram_page_type() 的 patch,内核会提示异常,那么开发者可以自行合入补丁之后,该异常会消失,系统就可以将内核虚拟地址以 UC 方式映射到物理内存上. 另外通过前面的分析,如果将物理内存设置为 UC 之后,其性能将会受到极大影响,那么接下来通过一个实践案例对比 UC 和 WB(默认为 WB) 物理内存之间性能差异,案例在 BiscuitOS 的部署逻辑为:

UC Vs. WB 物理内存性能比对

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] CACHE Performance: WB Vs. UC on Normal Memory --->

-*- CACHE User-Page for Kernel Stub (Basic) --->

# 进入源码目录

# Userspace: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-PERFORMANCE-WB-UC-default/

# Kernel: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default/

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-PERFORMANCE-WB-VS-UC-default/

# 部署源码

make prepare

make download

# 在 BiscuitOS 中实践

make buildBiscuitOS-CACHE-PERFORMANCE-WB-VS-UC-default Source Code on Gitee

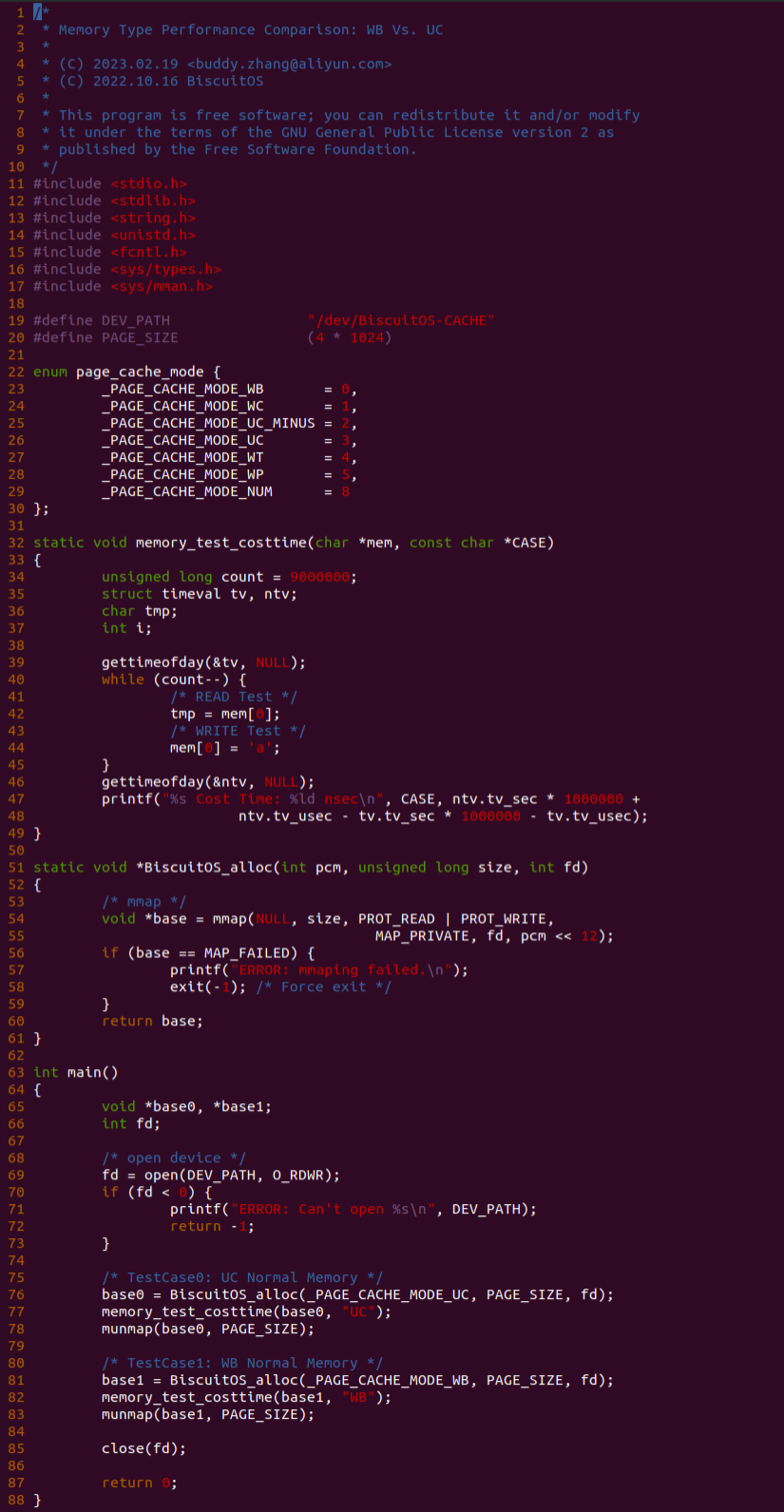

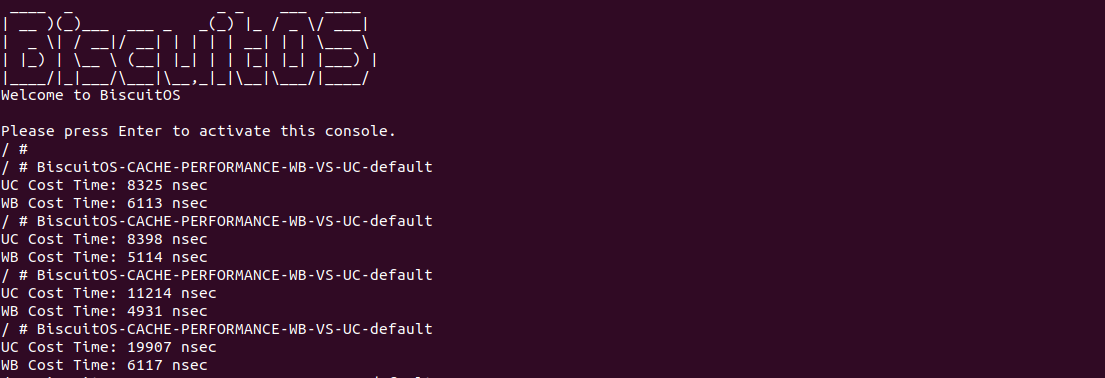

基于上一个实践案例进行改进,实践案例提供了 memory_test_costtime() 函数,其逻辑是对同一个地址循环读写 9000000 次,并计算所消耗的时间,并将时间按 ns 进行打印。其他的代码逻辑和上一个分析一致,并且其也对应一个内核模块。那么接下来直接在 BiscuitOS 上运行程序查看结果(运行前在 CMDLINE 中添加预留内存字段):

BiscuitOS 运行之后,分别运行 BiscuitOS-CACHE-PERFORMANCE-WB-VS-UC-default 5 次,查看每次 WB 和 UC 之间的差异,可以看到差异最大的一组 WB 仅仅消耗 6117ns, 而 UC 消耗达到 19907ns. 通过实践可以初步得出结论不同的 memory type 之间会存在性能差异,并且 WB 在读写测试中明显优于 UC 内存, 因此建议不要把普通物理内存映射为 UC!

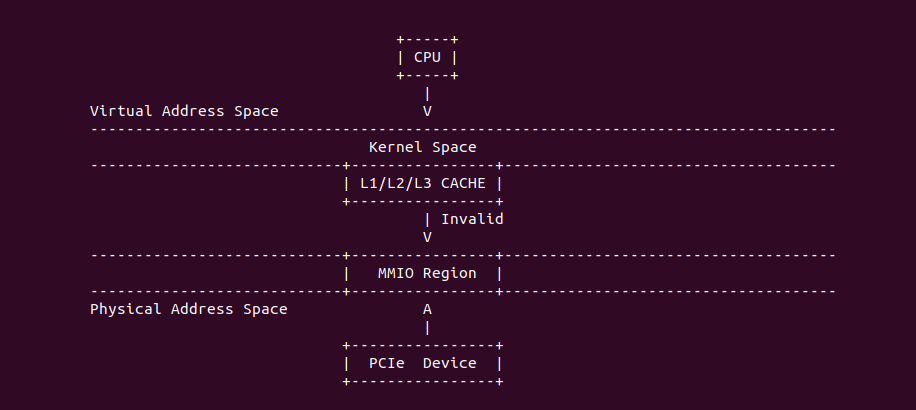

Uncacheable (UC-)

Uncacheable (UC-): 非缓存类型,该类型的物理内存不使用任何缓存机制. 系统对该类型的物理内存的读写请求会直接发送到总线上,另外硬件上不会对该类型物理内存的访问和对应页表遍历预测功能,同样也不会对分支进行预测, 与 UC 不同的是 UC- 会被 WC 给覆盖. UC- 缓存类型通常用于映射外设的 MMIO,因为外设不具有监听(snoop)总线的能力,为了保持设备看物理区域与 CPU 看到的一致,因此将该物理区域设置为 UC- 之后,CPU 对该区域的读写请求直接访问到物理地址上,不会缓存在 CACHE 里,因此可以保持设备和 CPU 看到数据的一致性. 不建议将普通的物理内存的缓存类型设置为 UC-,这样会 CPU 每次都对物理内存进行访问,这会大大影响系统性能. 接下来通过一个实践案例介绍内核如何将一段 MMIO 区域的缓存类型设置为 UC-, 其在 BiscuitOS 上的部署逻辑如下:

内核空间虚拟地址映射 UC- MMIO

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support BiscuitOS Hardware Emulate

[*] CACHE --->

[*] UNCACHED(UC-): Mapping UC- MMIO on Kernel --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-UNCACHED-MMIO-KERNEL-default

# 部署源码

make download

# 在 BiscuitOS/Broiler 中实践

make broilerBiscuitOS-CACHE-UNCACHED-MMIO-KERNEL-default Source Code on Gitee

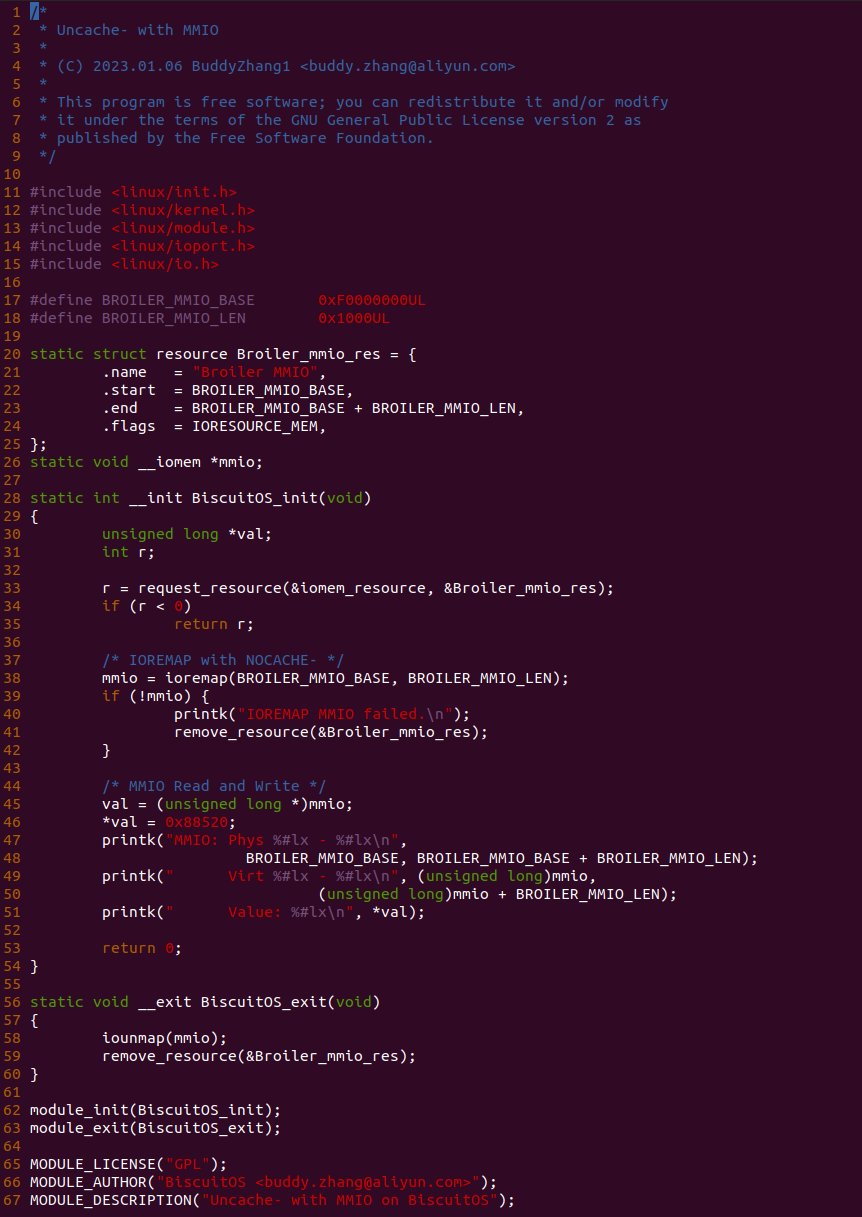

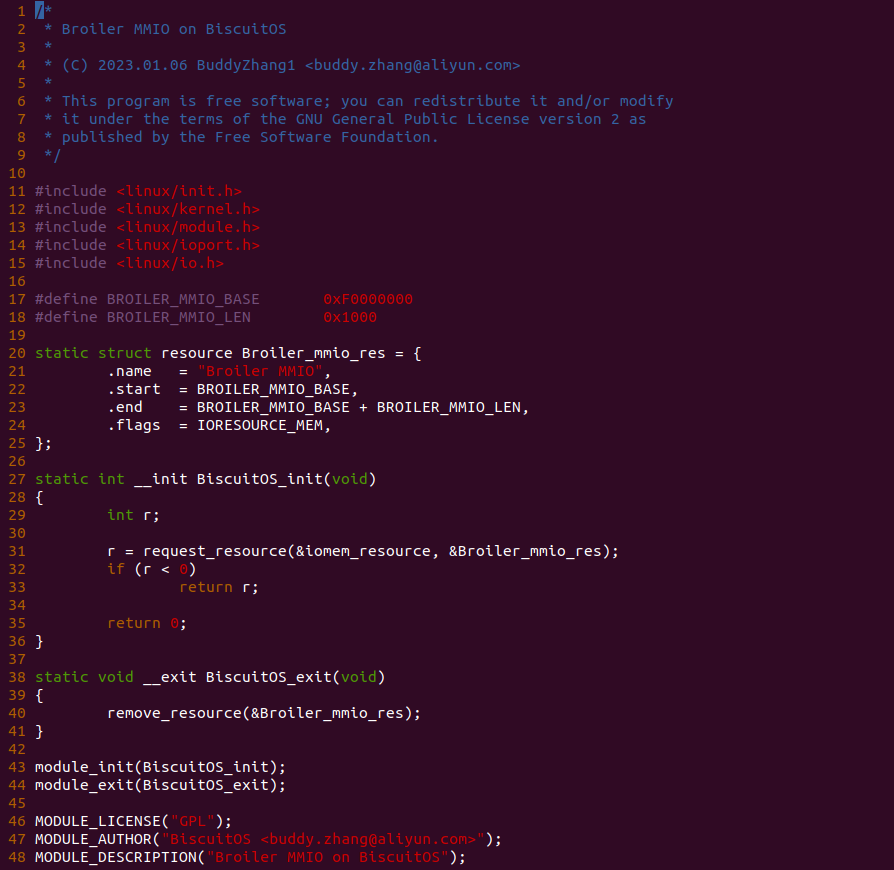

源码通过一个内核模块进行展示,模块有两部分组成,第一部分是 20-35 行,模块向系统资源总线注册了一段 MMIO,这段 MMIO 起始物理地址是 BROILER_MMIO_BASE, 长度为 BROILER_MMIO_LEN, 注册完毕之后可以在系统启动之后,通过 ‘/proc/iomem’ 接口查看到该段信息; 第二部分是 38-46 行,模块在 38 行调用 ioremap() 函数将 BROILER_MMIO_BASE 开始且长度为 BROILER_MMIO_LEN 的 MMIO 区域,映射为 UC- 的 memory type, 映射完毕之后函数在 46 行对 MMIO 进行访问,此时并不会触发缺页,因为 ioremap() 函数已为 MMIO 分配了对应的虚拟地址并建立了页表,因此模块可以直接访问 MMIO. 最后在 BiscuitOS 上实践模块,由于需要一段真实的 MMIO 才能运行模块,因此可使用 Broiler 模拟一段 MMIO,其起始物理地址为 0xF0000000(Broiler 已经模拟好硬件),开发者直接在源码目录执行 make broiler 即可:

BiscuitOS 运行之后,加载 BiscuitOS-CACHE-UNCACHED-MMIO-KERNEL-default.ko 模块之后,从打印的内核信息可以看出模块已经映射了 MMIO,并且向 MMIO 写入 0x88520 之后可以读出正确的数据,最后查看 ‘/sys/kernel/debug/x86/pat_memtype_list’ 节点查看系统 MMIO memory_type 信息,可以看到模块映射的 MMIO [0xF0000000, 0xF0001000] 为 uncached-minus, 另外查看 ‘/proc/iomem’ 节点查看物理地址空间信息,可以看到 [0xF0000000, 0xF0001000) 为 Broiler MMIO 区域, 实践符合预期. 接下来一个实践案例用于介绍如何将用户空间虚拟地址映射成 UC- 的 MMIO,BiscuitOS 部署逻辑如下:

用户空间虚拟地址映射 UC- MMIO

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support BiscuitOS Hardware Emulate

[*] CACHE --->

[*] UNCACHED(UC-): Mapping UC- MMIO on Userspace --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-UNCACHED-MMIO-USERSPACE-default

# 部署源码

make download

# 在 BiscuitOS/Broiler 中实践

make broilerBiscuitOS-CACHE-UNCACHED-MMIO-USERSPACE-default Source Code on Gitee

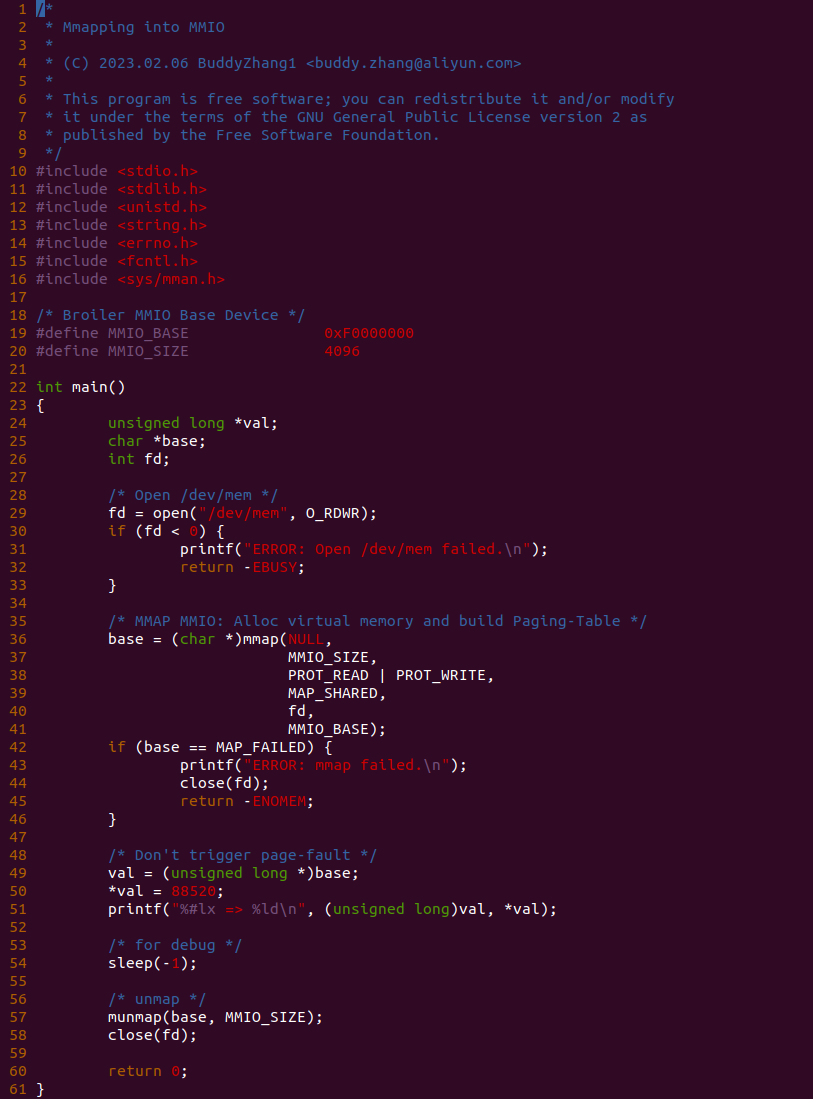

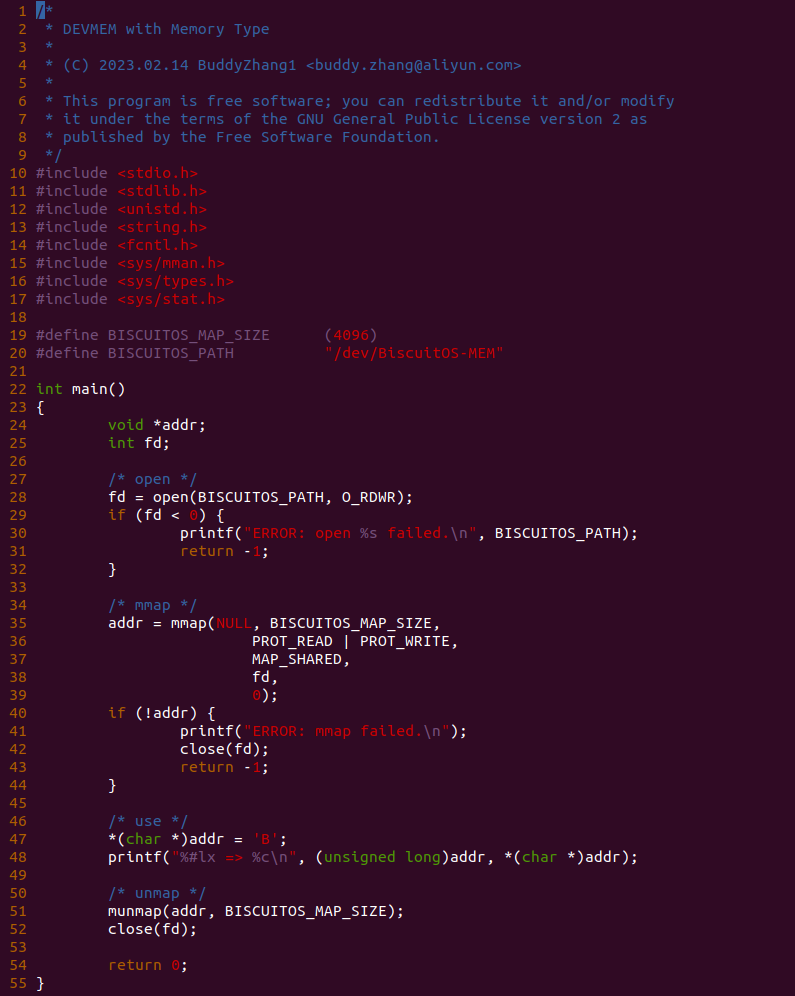

实践案例由两个部分组成,main.c 为内核模块部分,负责映射 MMIO 的底层逻辑。模块首先在 22-26 行定义了 MMIO 区域的信息,然后在 56-57 行通过调用 request_resource() 函数将 MMIO 区域添加到系统物理地址空间树里。接下来基于 Linux 提供的 “/dev/mem” 接口进行映射 MMIO.

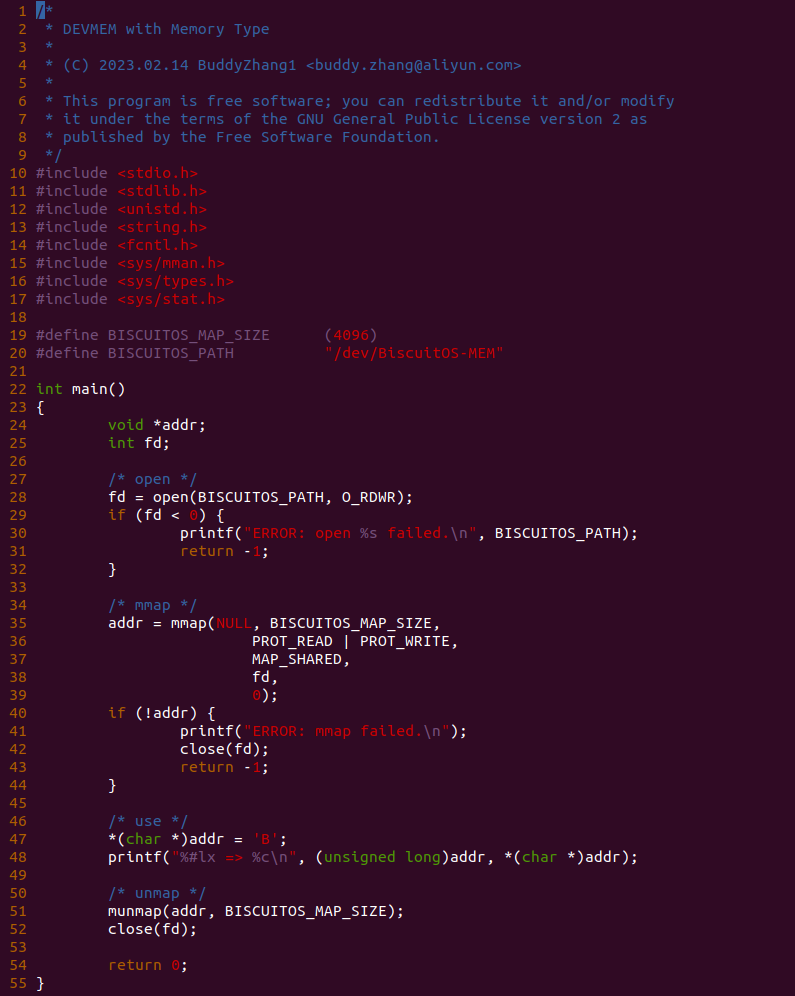

实践案例的另外一部分位于 app.c 内,其为用户空间程序,用于映射虚拟地址到 MMIO 并进行访问. 程序首先在 29 行通过 open() 函数打开 “/dev/mem” 节点,然后在 36-46 通过 mmap() 函数将进程地址空间的虚拟地址映射到 MMIO,接下来在 49-51 行对映射之后对 MMIO 进行访问,最后在 56-57 行释放相应的资源. 源码分析完毕之后在 BiscuitOS 进行实践,由于 MMIO 绑定在具体的硬件上,此时可以使用 Broiler 进行模块,直接使用 “make broiler” 命令进行实践:

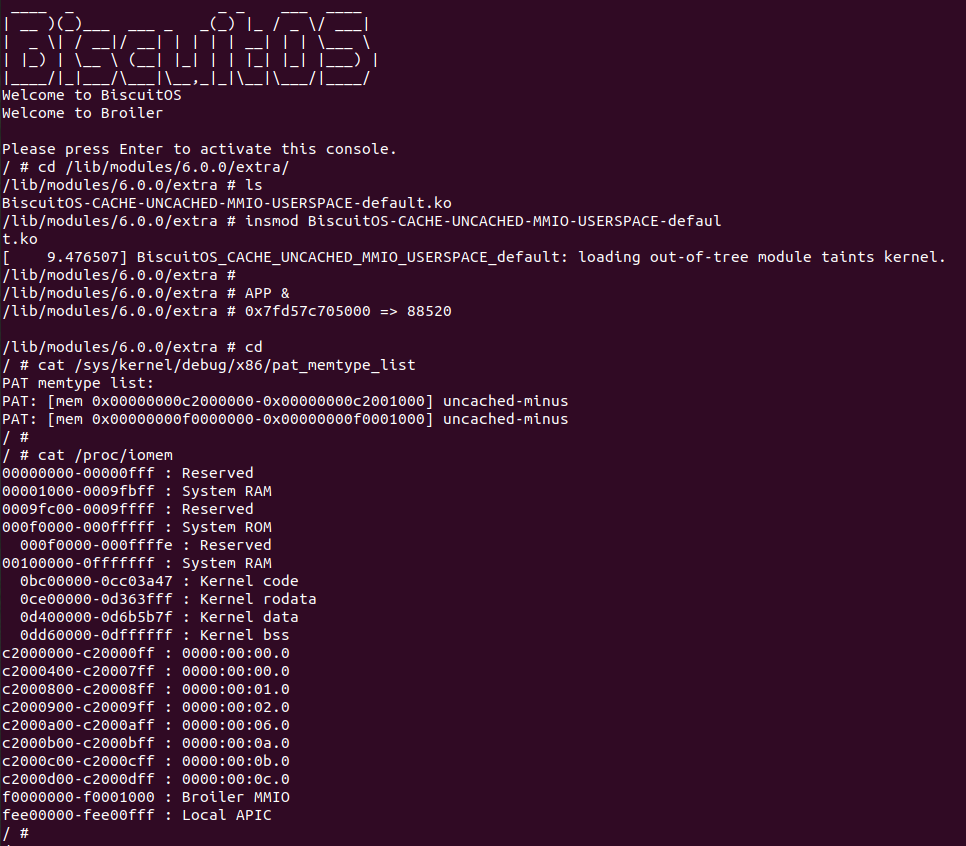

BiscuitOS Broiler 运行之后加载 BiscuitOS-CACHE-UNCACHED-MMIO-USERSPACE-default.ko, 接着运行用户态程序 APP,这里以后台方式运行,因此查看其他有用信息,运行之后可以看到正常访问 MMIO。接下来查看 /sys/kernel/debug/x86/pat_memtype_list 节点,可以看到 [0xF0000000, 0xF0001000) 区域映射为 uncached-minus,最后查看 /proc/iomem 系统物理地址空间,可以看到 Broiler MMIO 对应的区域正好是 [0xF0000000, 0xF0001000)。实践结果符合预期,那么接下来对普通物理内存映射为 UC- 场景进行实践:

用户空间虚拟内存映射 UC- 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] UNCACHED(UC-): Mapping UC- Memory on Userspace --->

-*- CACHE User-Page for Kernel Stub (Basic) --->

# 进入源码目录

# Userspace: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-UNCACHED-MEM-USERSPACE-default/

# Kernel: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default/

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-UNCACHED-MEM-USERSPACE-default/

# 部署源码

make prepare

make download

# 在 BiscuitOS 中实践

make buildBiscuitOS-CACHE-UNCACHED-MEM-USERSPACE-default Source Code on Gitee

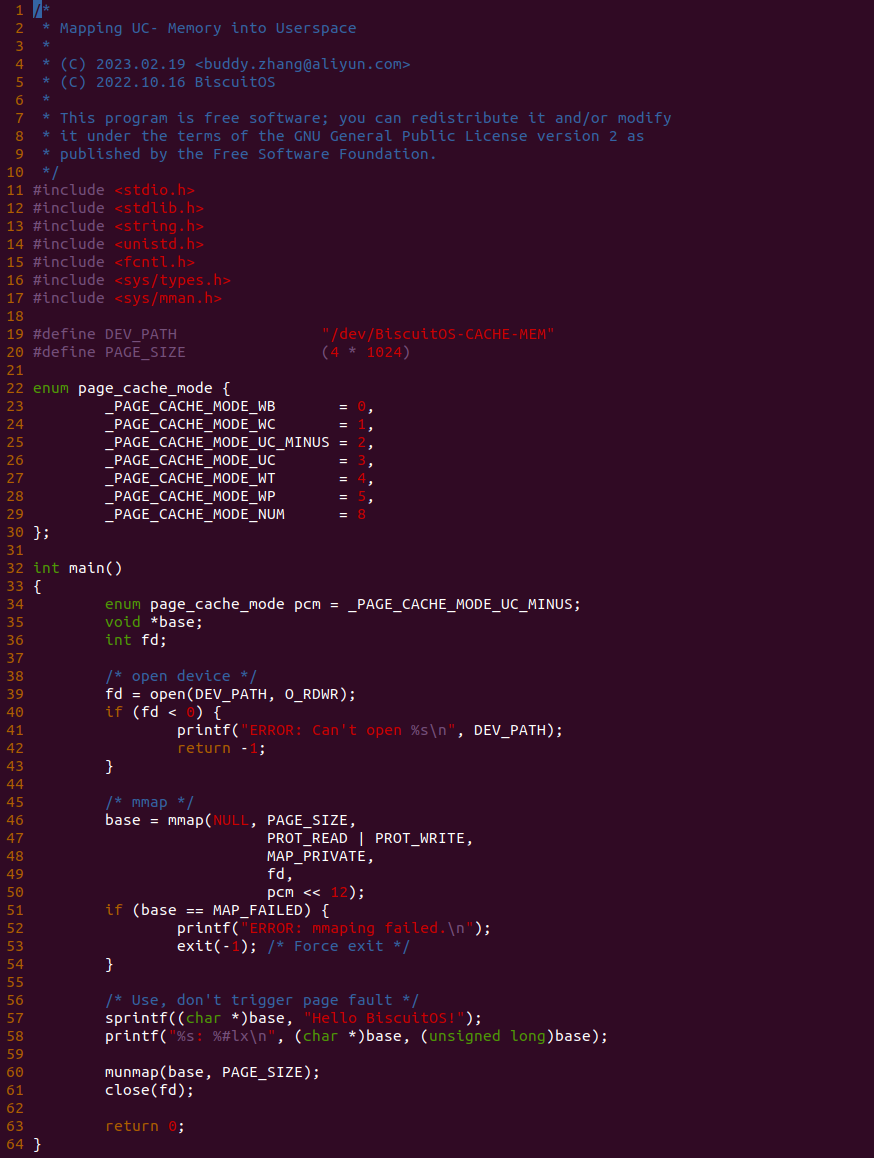

源码分成两部分,其中一部分为用户空间程序(上图所示), 用户空间代码的主要功能是映射一段虚拟内存,并将其缓存类型设置为 UC-. 函数首先在 34 行将 pcm 变量设置为 _PAGE_CACHE_MODE_UC_MINUS, 然后在 39 行打开 “/dev/BiscuitOS-CACHE” 节点,并基于该节点映射长度为 PAGE_SIZE 的虚拟内存,此时在函数 50 行将 pcm 传入到 mmap() 函数,映射完毕后函数在 58-59 行使用 UC 的内存,使用完毕在 61-62 行解除映射并关闭文件。

BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default Source Code on Gitee

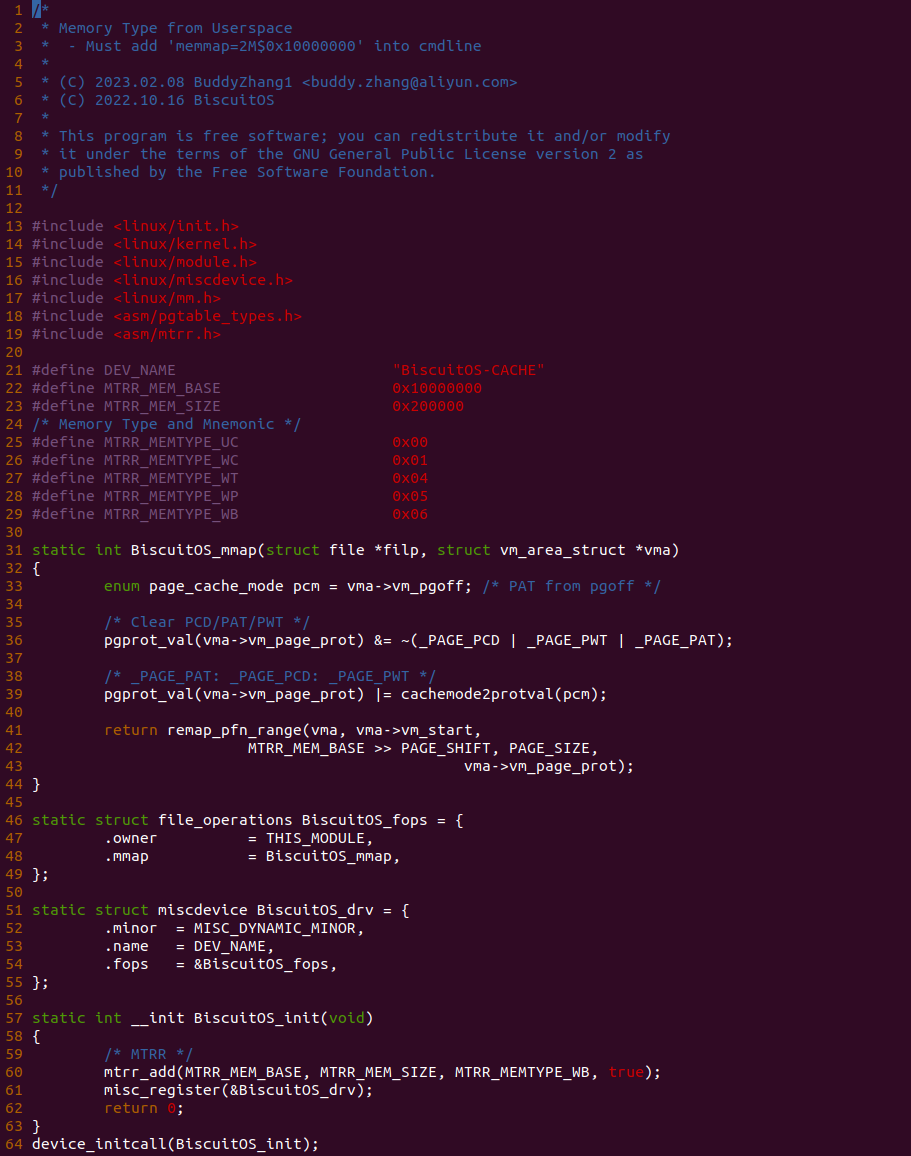

源码的另外一部分位于内核空间,其主要功能是进行实际的映射任务。模块通过一个 MISC 驱动进行实现,其提供了 mmap 接口 BiscuitOS_mmap(), 当用户空间基于 “/dev/BiscuitOS-CACHE” 节点调用 mmap() 函数时,BiscuitOS_mmap() 函数就会别调用。模块首先在 60 行调用 mtrr_add() 函数将 [MTRR_MEM_BASE, MTRR_MEM_SIZE + MTRR_MEM_BASE) 区域的 MTRR 设置为 WB. 模块接着在 33 行在用户空间调用 mmap() 函数时从 vma 的 vm_pgoff 成员中获得 PAGE CACHE MODE 信息,接着在 36 行将 vma_page_prot 成员中移除 _PAGE_PCD、_PAGE_PWT 和 _PAGE_PAT 属性,并在 39 行调用 cachemode2protval() 函数将 PAGE CACHE MODE 转换成对应的页表属性,并重新存储到 vma 的 vm_page_prot, 以此作为用于空间设置的 memory type 页表属性,最后模块在 41 行调用 remap_pfn_range() 函数为虚拟内存建立页表并映射到 MTRR_MEM_BASE 对应的物理内存上. 接下来在 BiscuitOS 上实践该案例:

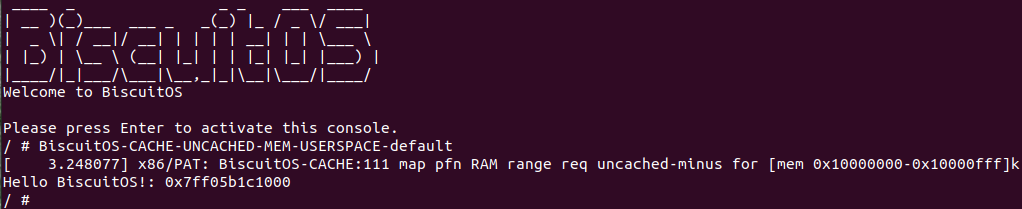

BiscuitOS 运行之后, 执行应用程序 BiscuitOS-CACHE-USER-PAGE-U-default,此时系统提示了程序预期将 [0x10000000-0x10000fff] 为 uncached-minus,但是系统还是将对应的 memory type 设置为 write-back, 这个与预期不符合. 查看内核模块源码的 3 行提示需要将 [0x10000000, 0x10200000) 进行预留,那么在 CMDLINE(CMDLINE 位于 RunBiscuitOS.sh 文件中) 中添加预留字段后再次实践:

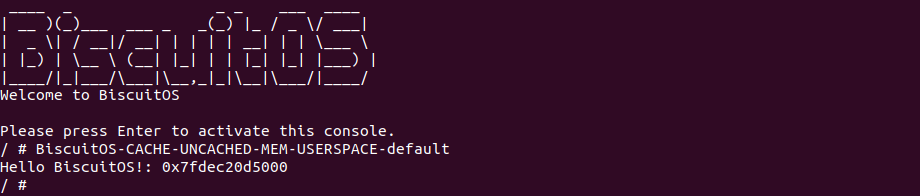

BiscuitOS 在次运行之后,运行应用程序,可以看到系统没有再提示修改信息了,那么用户进程已经成功将一段物理内存的 memory type 设置为 UC-. 实践符合预期,那么接下来实践内核空间虚拟地址映射 UC- 物理内存:

内核空间虚拟内存映射 UC- 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] UNCACHED(UC-): Mapping UC- Memory on Kernel --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-UNCACHED-MEM-KERNEL-default/

# 部署源码

make download

# 在 BiscuitOS 中实践

make buildBiscuitOS-CACHE-UNCACHED-MEM-KERNEL-default Source Code on Gitee

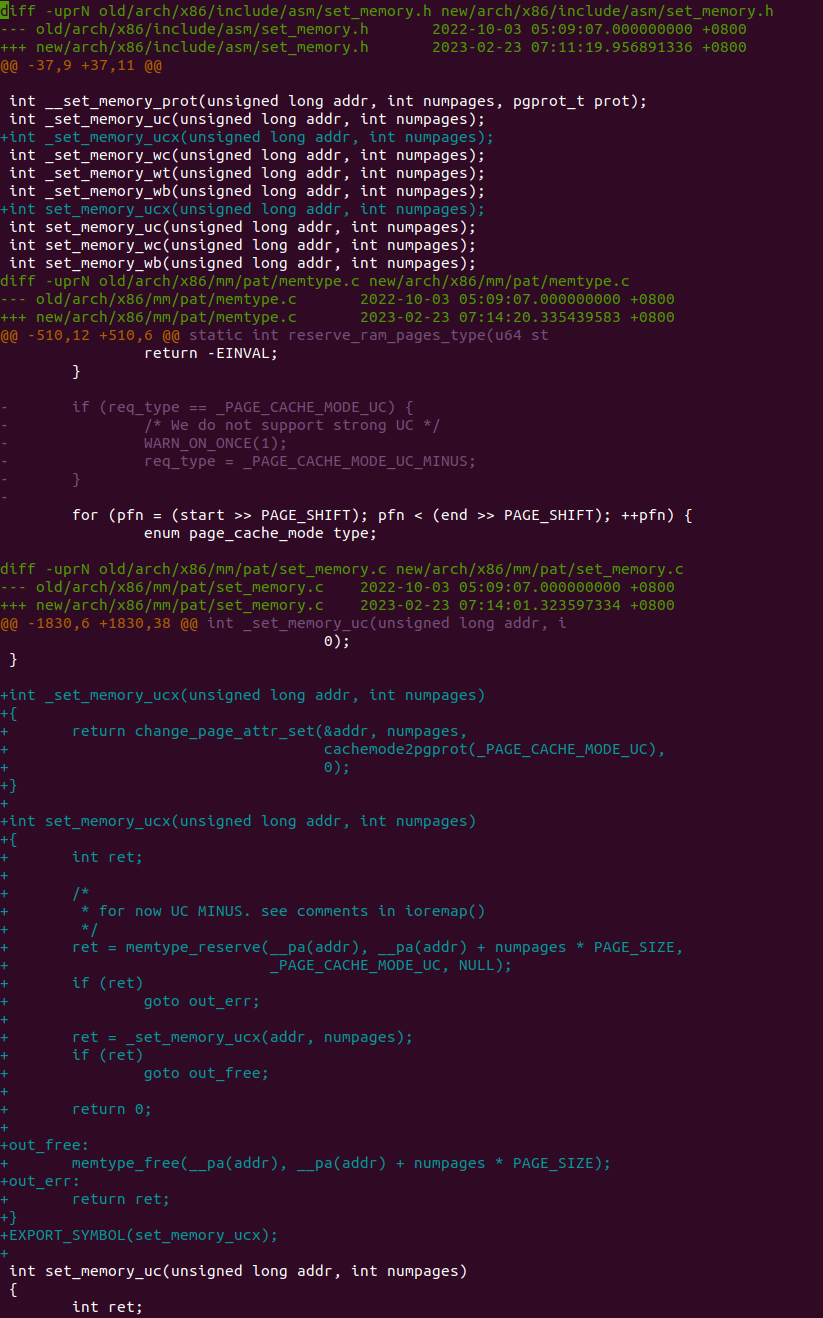

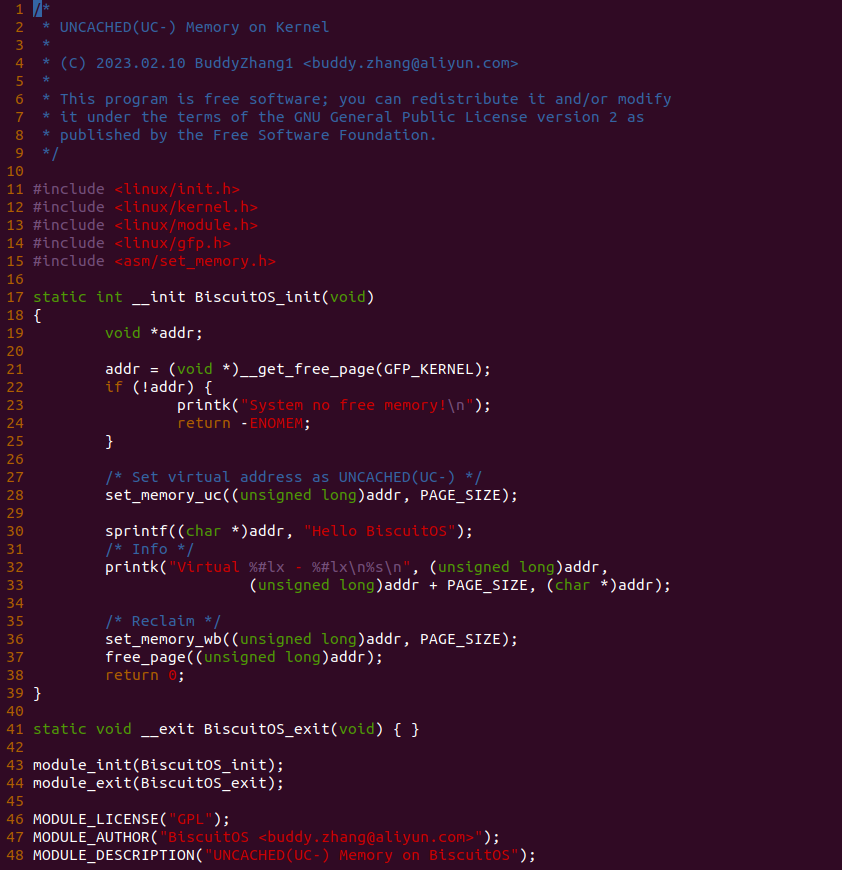

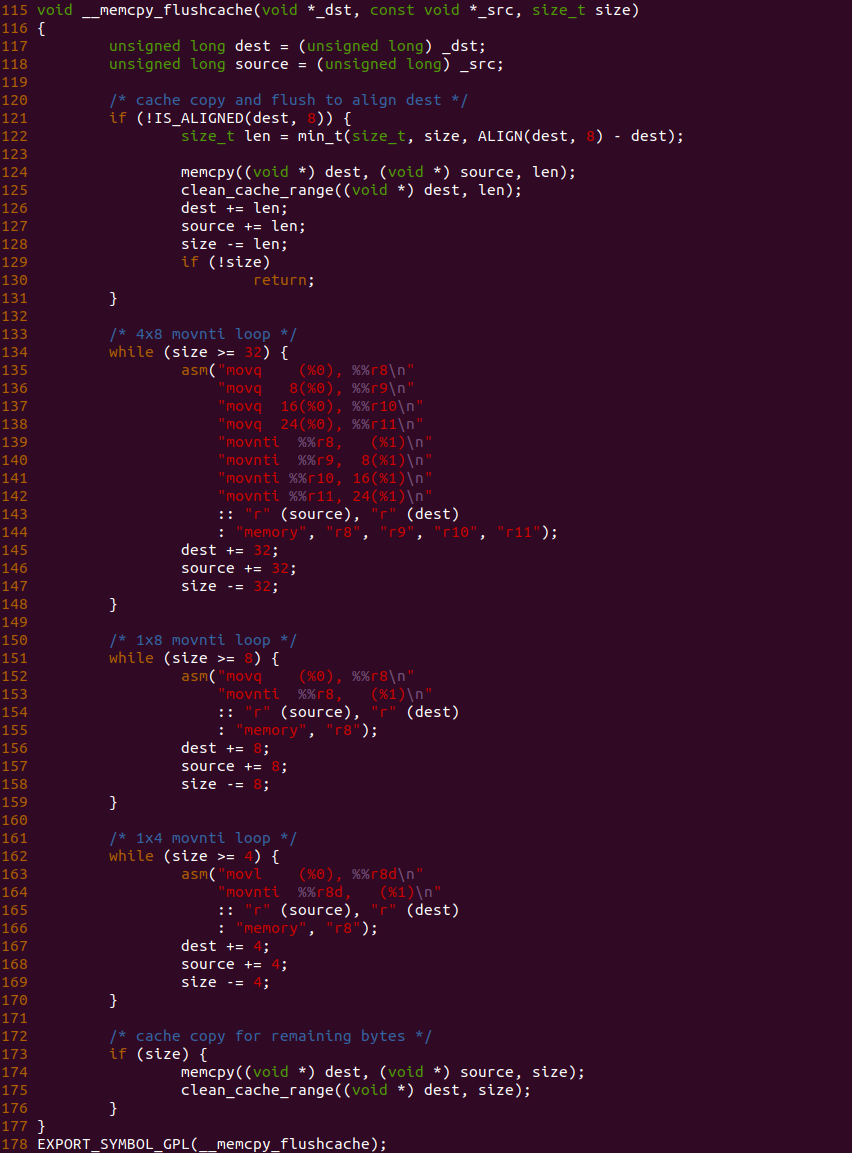

实践案例主要目的是在内核空间申请一段内存之后,将对应的虚拟地址以 UC- 的方式映射到物理内存,并进行访问。案例在 21-25 行通过 __get_free_page() 函数分配一个物理页并获得对应的虚拟地址,然后在 28 行调用 set_memory_uc() 函数进行 UC- 方式的映射,案例接着在 30-33 行对映射之后的虚拟地址进行访问。最后在 36-37 行回收设置,值得注意的是当将内核空间虚拟地址设置为非 WB 之后,在回收时要主动设置为 WB. 接下来在 BiscuitOS 上进行实践:

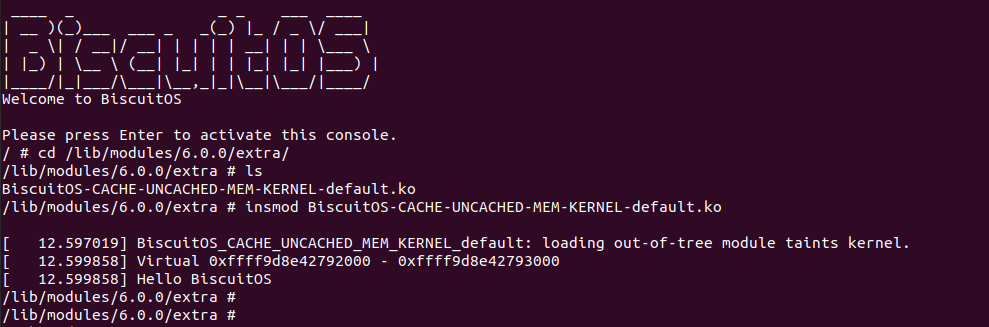

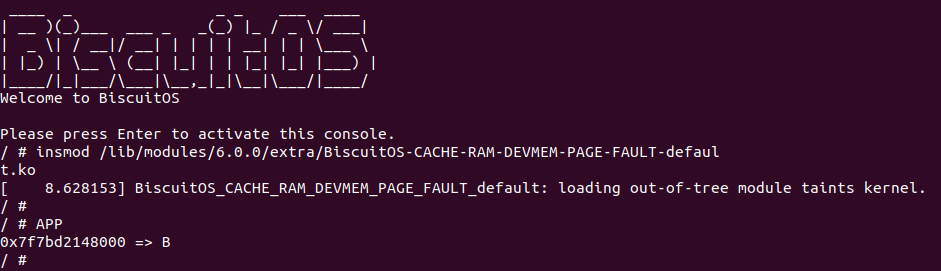

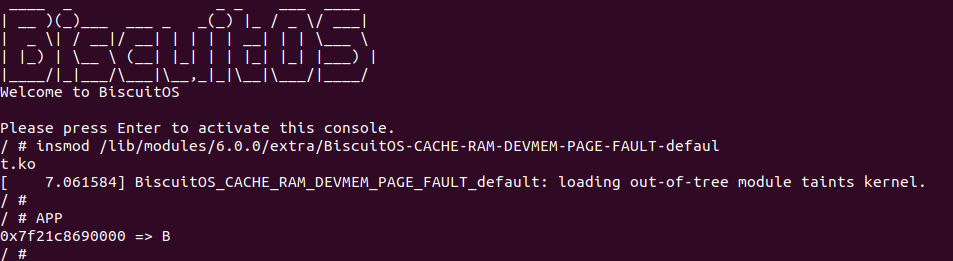

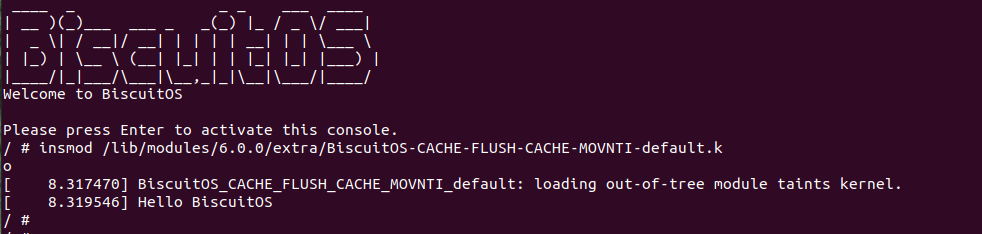

BiscuitOS 运行之后,加载 BiscuitOS-CACHE-UNCACHED-MEM-KERNEL-default.ko 模块,可以看到系统可以使用 UC- 的虚拟内存,并打印字符串 “Hello BiscuitOS”, 符合预期.

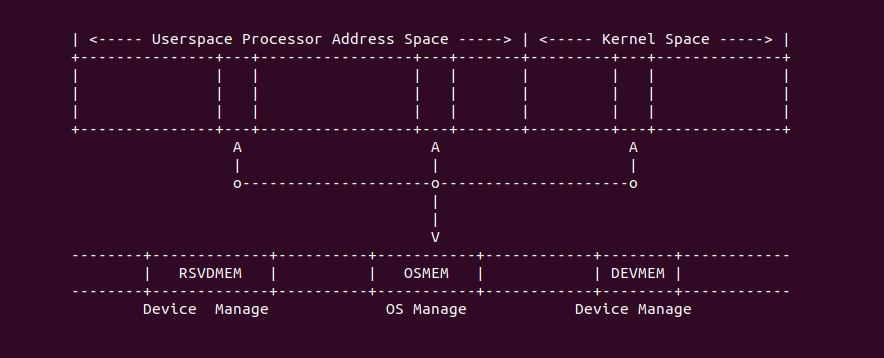

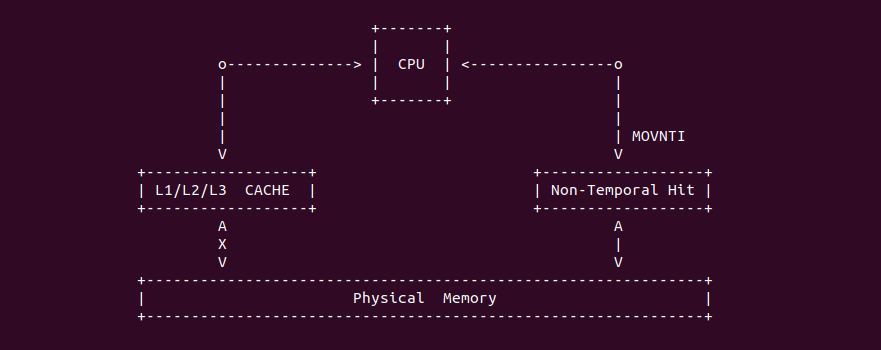

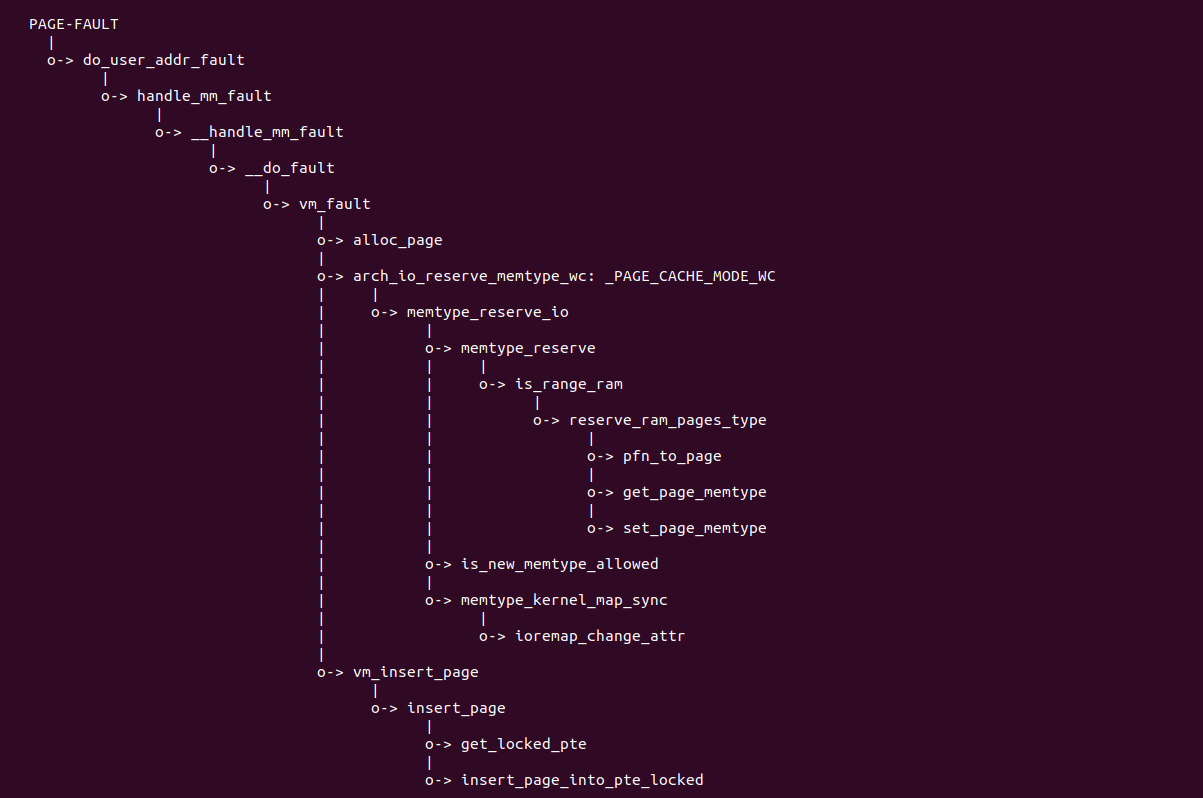

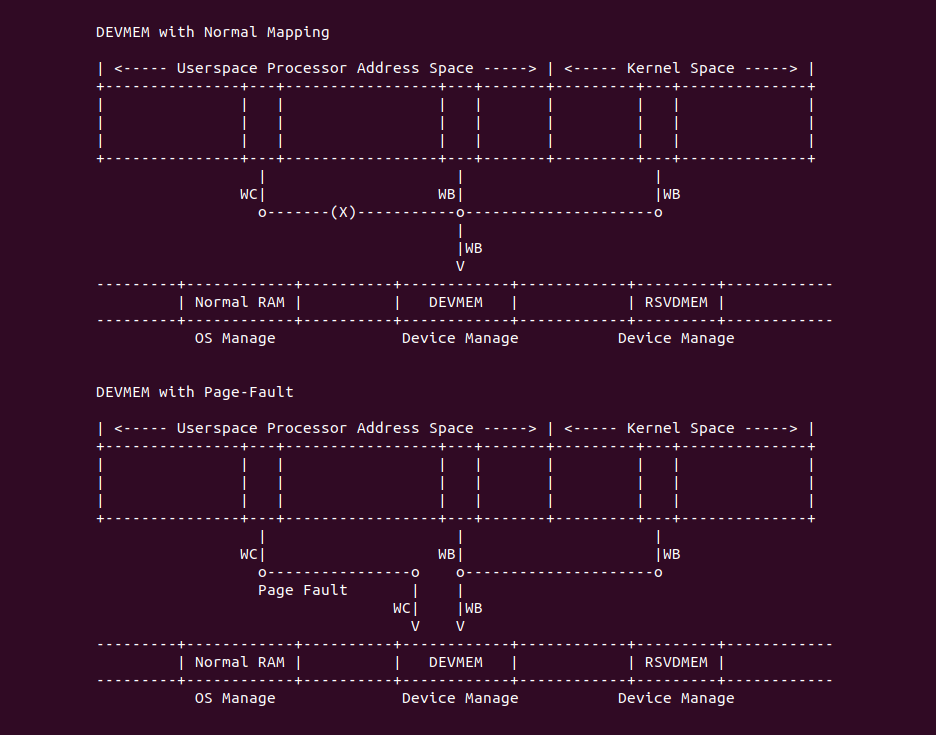

Write Combining (WC)

Write Combining (WC): 写合并类型,该类型与 UC 类似不使用任何缓存机制,并且不保证 CACHE 一致性协议。WC 允许读预测,但写请求可能会被延后并合并缓存到 Write Combining Buffer(WC) 里,以此减少对总线拥堵。如果 WC Buffer 没有满,那么写请求很可能被延时并合并到 WC buffer,直到下一个串行事件发生之后,写请求才会被真正写入内存. 这类型应用的场景包括 Video Frame Buffer,其特点就是对写的顺序不是很重要,只要最后更新数据的时候都能在图形设备上显示. 具体可以参考如下章节对 WriteCombining Buffer 进一步了解, 那么接下来通过一组实践案例介绍内核和用户空间如何使用 WC 类型的内存.

内核空间虚拟地址映射 WC MMIO

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support BiscuitOS Hardware Emulate

[*] CACHE --->

[*] WriteCombining(WC): Mapping WC MMIO on Kernel --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WC-MMIO-KERNEL-default

# 部署源码

make download

# 在 BiscuitOS/Broiler 中实践

make broilerBiscuitOS-CACHE-UNCACHE-WC-KERNEL-default Source Code on Gitee

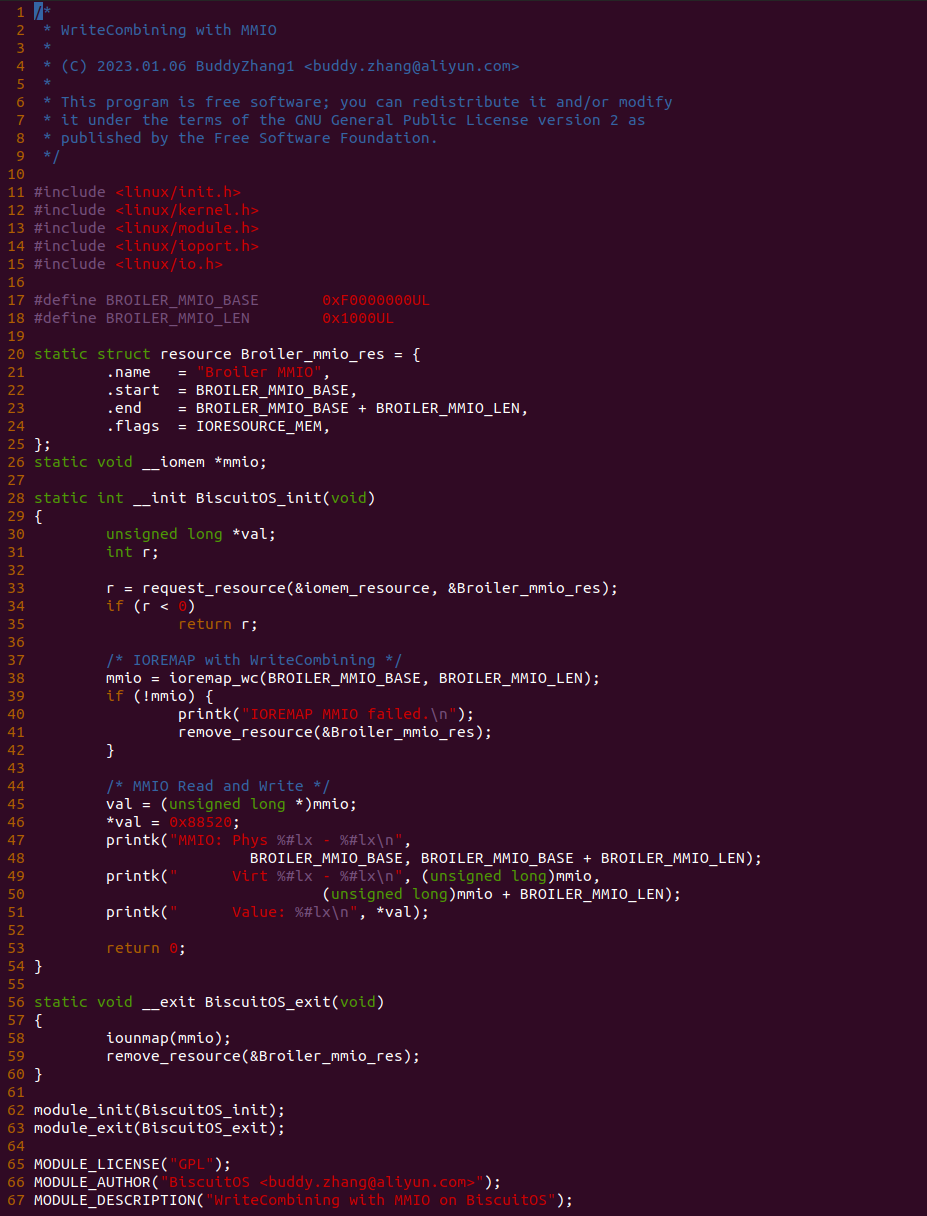

源码通过一个内核模块进行展示,模块有两部分组成,第一部分是 20-35 行,模块向系统资源总线注册了一段 MMIO,这段 MMIO 起始物理地址是 BROILER_MMIO_BASE, 长度为 BROILER_MMIO_LEN, 注册完毕之后可以在系统启动之后,通过 ‘/proc/iomem’ 接口查看到该段信息; 第二部分是 38-46 行,模块在 38 行调用 ioremap_wc() 函数将 BROILER_MMIO_BASE 开始且长度为 BROILER_MMIO_LEN 的 MMIO 区域,映射为 WriteCombining 的 memory type, 映射完毕之后函数在 46 行对 MMIO 进行访问,此时并不会触发缺页,因为 ioremap_wc() 函数已为 MMIO 分配了对应的虚拟地址并建立了页表,因此模块可以直接访问 MMIO. 最后在 BiscuitOS 上实践模块,由于需要一段真实的 MMIO 才能运行模块,因此可使用 Broiler 模拟一段 MMIO,其起始物理地址为 0xF0000000(Broiler 已经模拟好硬件),开发者直接在源码目录执行 make broiler 即可:

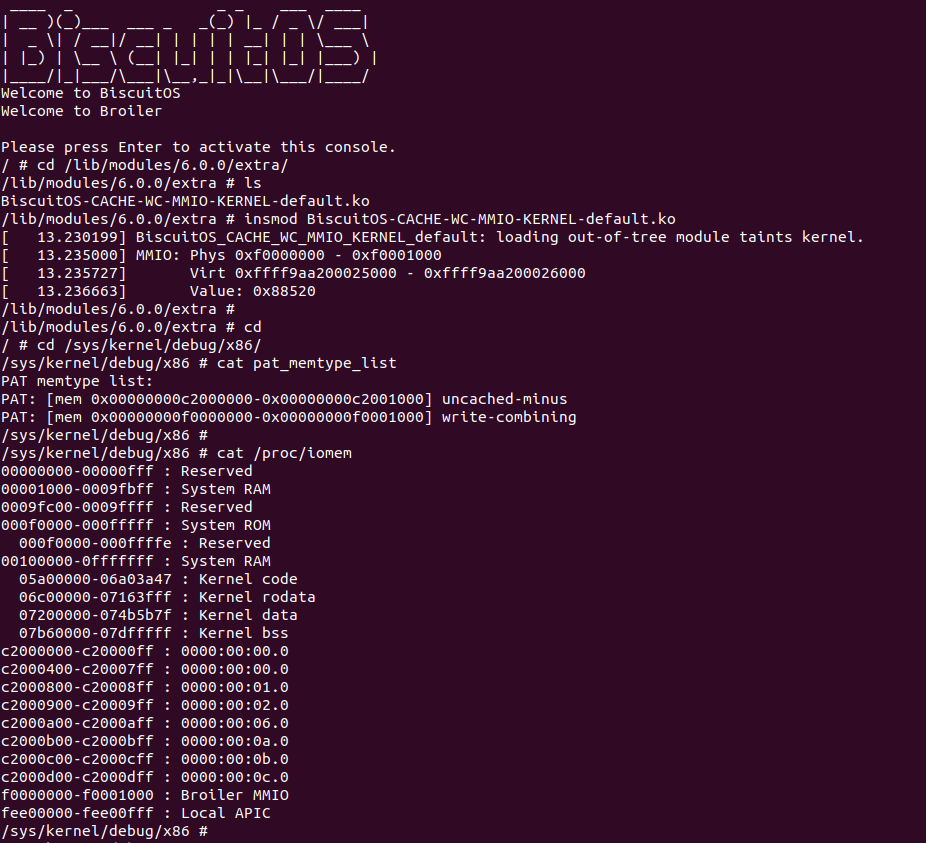

BiscuitOS 运行之后,加载 BiscuitOS-CACHE-WC-MMIO-KERNEL-default.ko 模块之后,从打印的内核信息可以看出模块已经映射了 MMIO,并且向 MMIO 写入 0x88520 之后可以读出正确的数据,最后查看 ‘/sys/kernel/debug/x86/pat_memtype_list’ 节点查看系统 MMIO memory_type 信息,可以看到模块映射的 MMIO [0xF0000000, 0xF0001000] 为 write-combining, 另外查看 ‘/proc/iomem’ 节点查看物理地址空间信息,可以看到 [0xF0000000, 0xF0001000) 为 Broiler MMIO 区域, 实践符合预期. 接下来一个实践案例用于介绍如何将用户空间虚拟地址映射成 WC 的 MMIO,BiscuitOS 部署逻辑如下:

用户空间虚拟地址映射 WC MMIO

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support BiscuitOS Hardware Emulate

[*] CACHE --->

[*] WriteCombining(WC): Mapping WC MMIO on Userspace --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WC-MMIO-USERSPACE-default

# 部署源码

make download

# 在 BiscuitOS/Broiler 中实践

make broilerBiscuitOS-CACHE-WC-MMIO-USERSPACE-default Source Code on Gitee

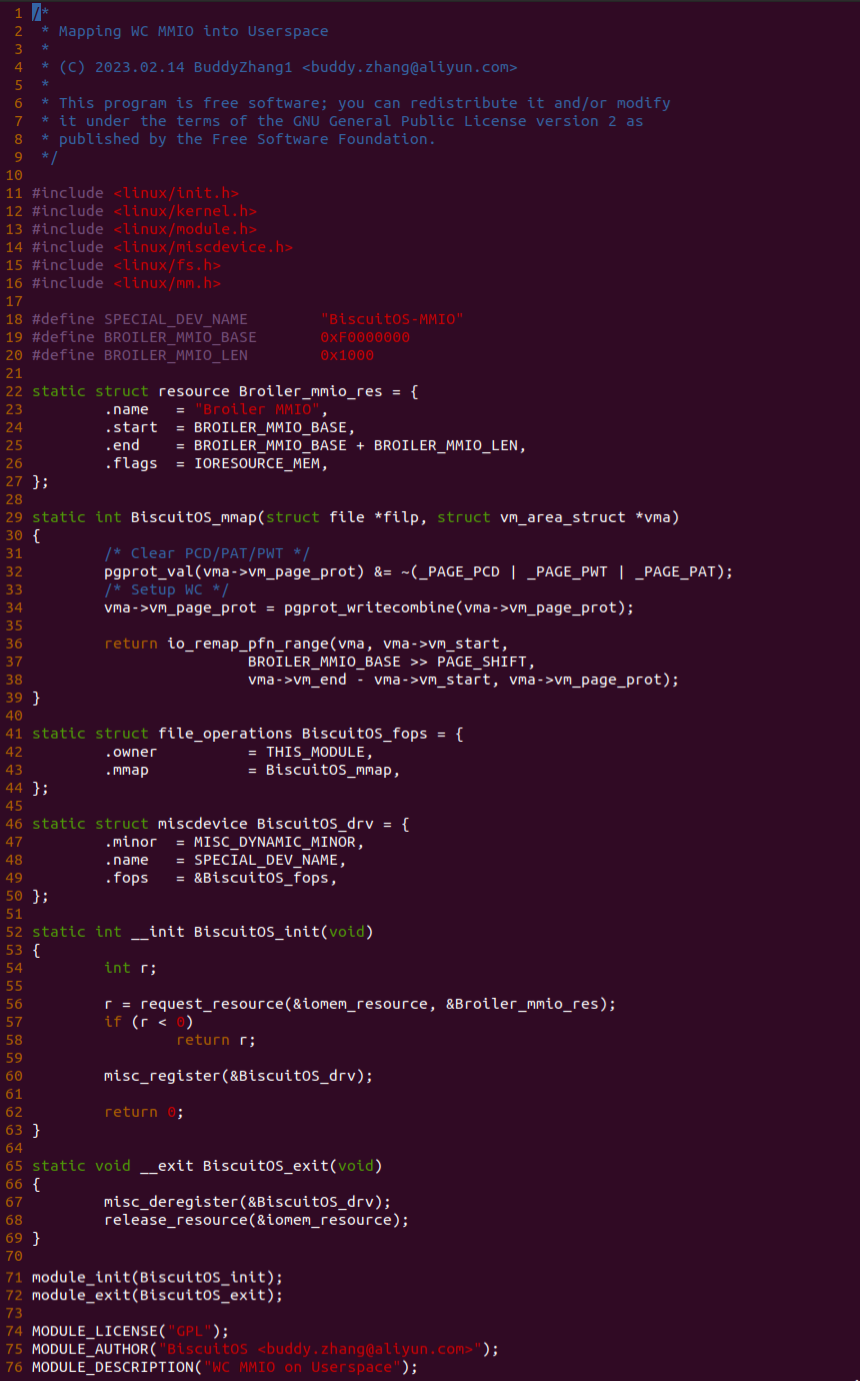

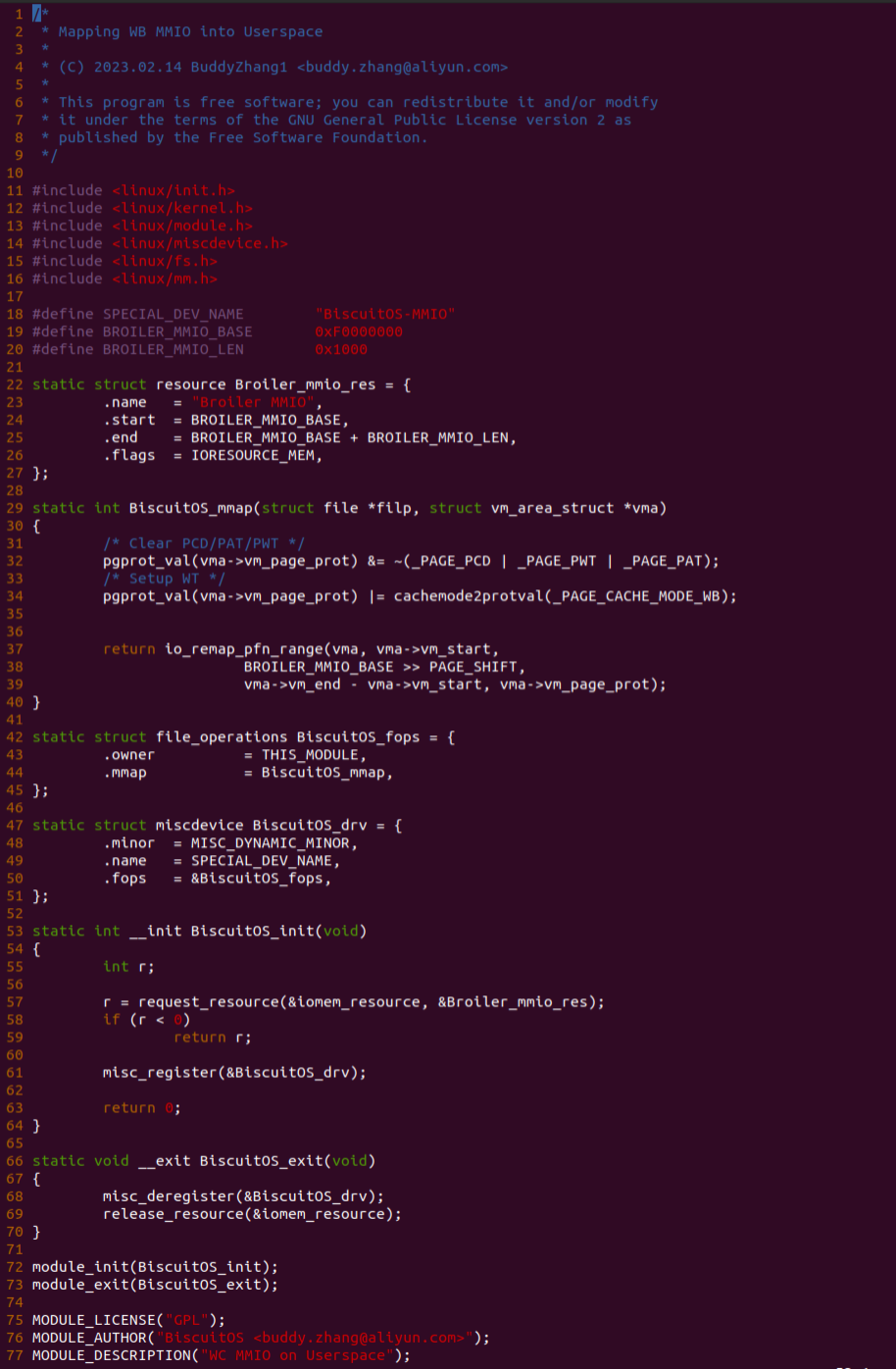

实践案例由两个部分组成,main.c 为内核模块部分,负责映射 MMIO 的底层逻辑。模块首先在 22-26 行定义了 MMIO 区域的信息,然后在 56-57 行通过调用 request_resource() 函数将 MMIO 区域添加到系统物理地址空间树里。模块通过注册一个 MISC 驱动,向用户空间提供 “/dev/BiscuitOS-MMIO” 接口,用户空间程序打开该接口,并调用 mmap() 映射 MMIO 时会调用到模块的 BiscuitOS_mmap() 函数,该函数首先在 32 行将虚拟地址对应的页表属性里的 _PAGE_PAT、_PAGE_PCD 和 _PAGE_PWT 标志清除,然后在 34 行调用 pgport_writecombine() 函数,将 WC 属性赋值到 vm_page_prot 成员,接下来调用 io_remap_pfn_range() 函数进行虚拟地址到 MMIO 的映射工作。映射完毕之后用户空间虚拟地址就可以以 WC 方式访问 MMIO.

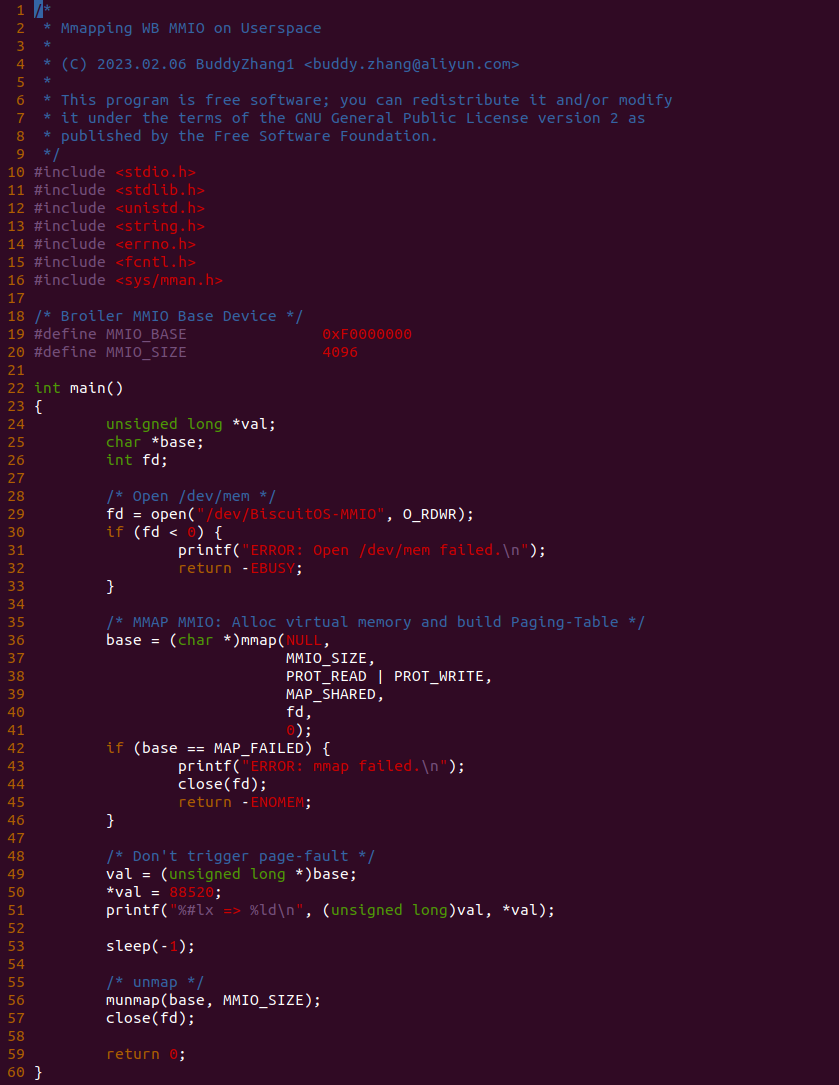

实践案例的另外一部分位于 app.c 内,其为用户空间程序,用于映射虚拟地址到 MMIO 并进行访问. 程序首先在 29 行通过 open() 函数打开 “/dev/BiscuitOS-MMIO” 节点,然后在 36-46 通过 mmap() 函数将进程地址空间的虚拟地址映射到 MMIO,接下来在 49-51 行对映射之后对 MMIO 进行访问,最后在 56-57 行释放相应的资源. 源码分析完毕之后在 BiscuitOS 进行实践,由于 MMIO 绑定在具体的硬件上,此时可以使用 Broiler 进行模块,直接使用 “make broiler” 命令进行实践:

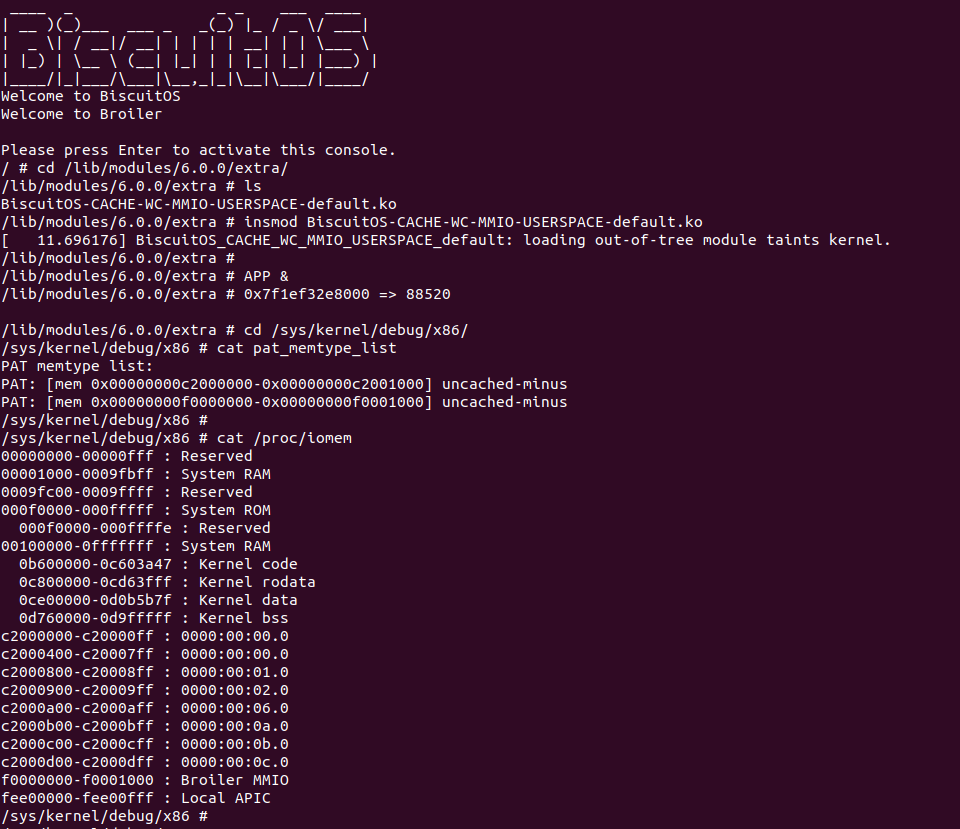

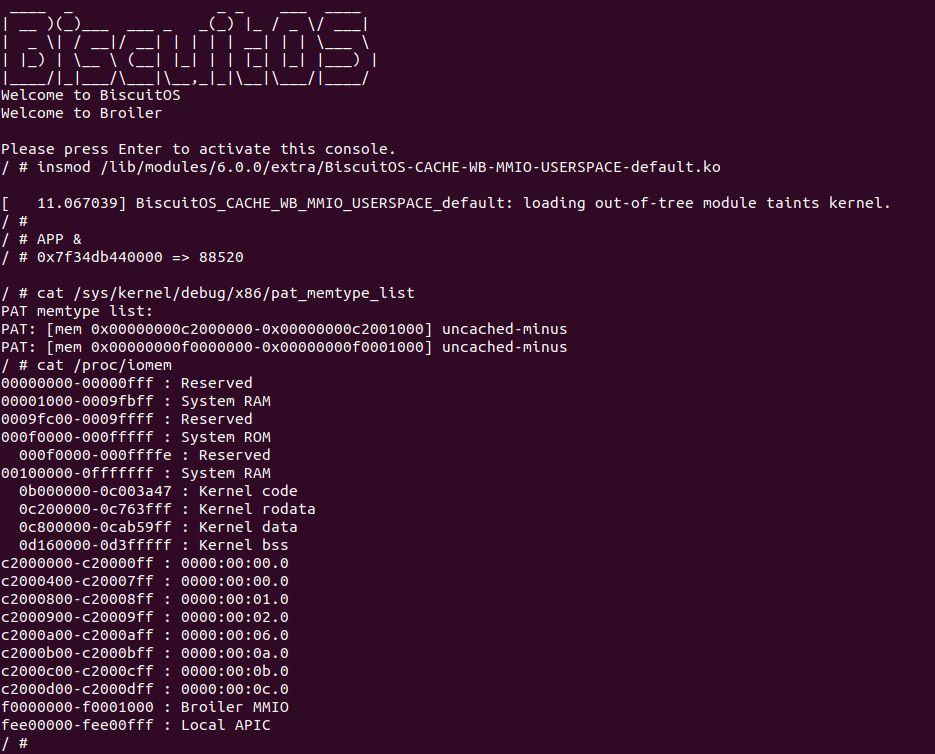

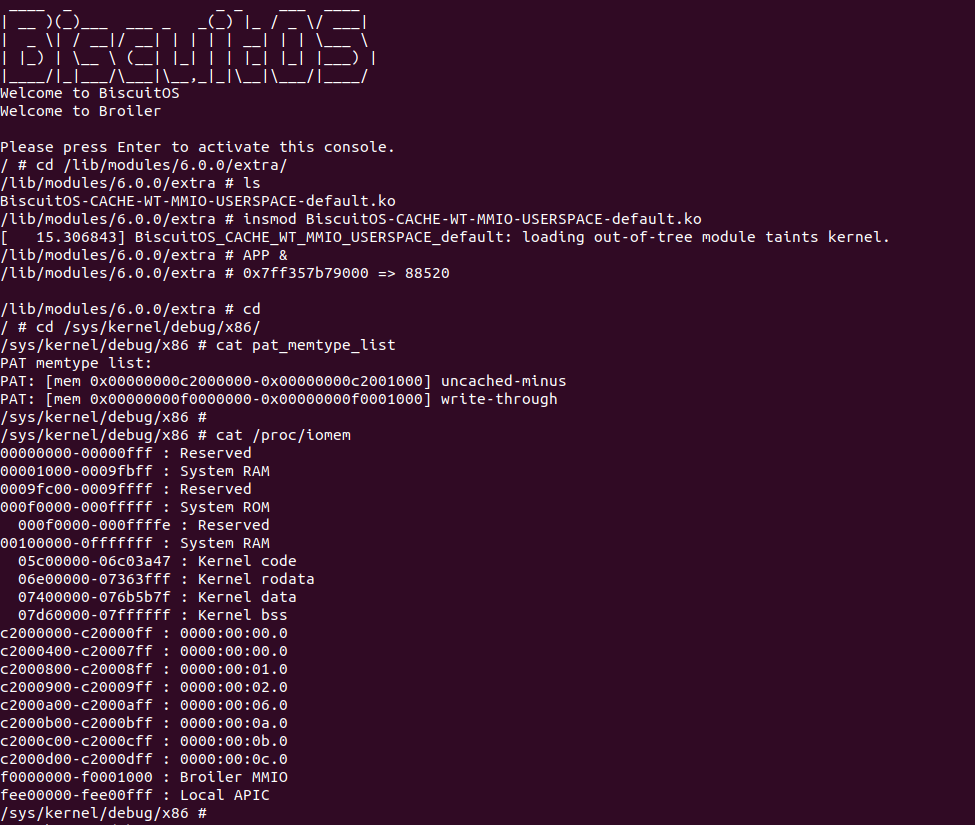

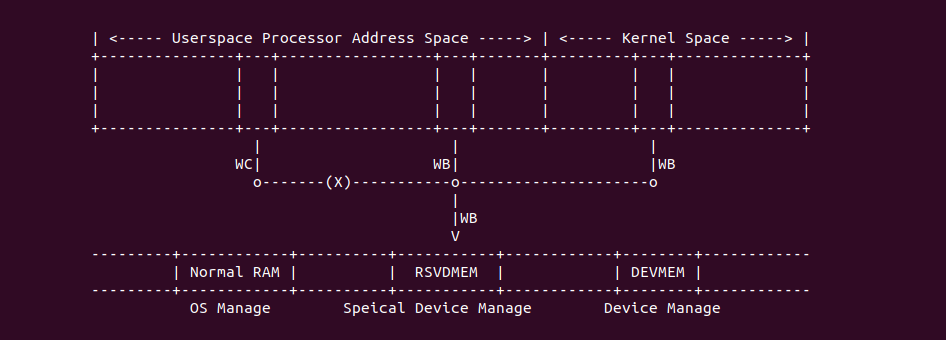

BiscuitOS Broiler 运行之后加载 BiscuitOS-CACHE-WC-MMIO-USERSPACE-default.ko, 接着运行用户态程序 APP,这里以后台方式运行,因此查看其他有用信息,运行之后可以看到正常访问 MMIO。接下来查看 /sys/kernel/debug/x86/pat_memtype_list 节点,可以看到 [0xF0000000, 0xF0001000) 区域映射为 uncached-minus,最后查看 /proc/iomem 系统物理地址空间,可以看到 Broiler MMIO 对应的区域正好是 [0xF0000000, 0xF0001000)。实践结果不符合预期,为什么用户空间无法映射 WC MMIO 呢? 具体分析请看. 那么接下来对普通物理内存映射为 WC 场景进行实践:

用户空间虚拟内存映射 WC 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] WriteCombining(WC): Mapping WC Memory on Userspace --->

-*- CACHE User-Page for Kernel Stub (Basic) --->

# 进入源码目录

# Userspace: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WC-MEM-USERSPACE-default/

# Kernel: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default/

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WC-MEM-USERSPACE-default/

# 部署源码

make prepare

make download

# 在 BiscuitOS 中实践

make buildBiscuitOS-CACHE-WC-MEM-USERSPACE-default Source Code on Gitee

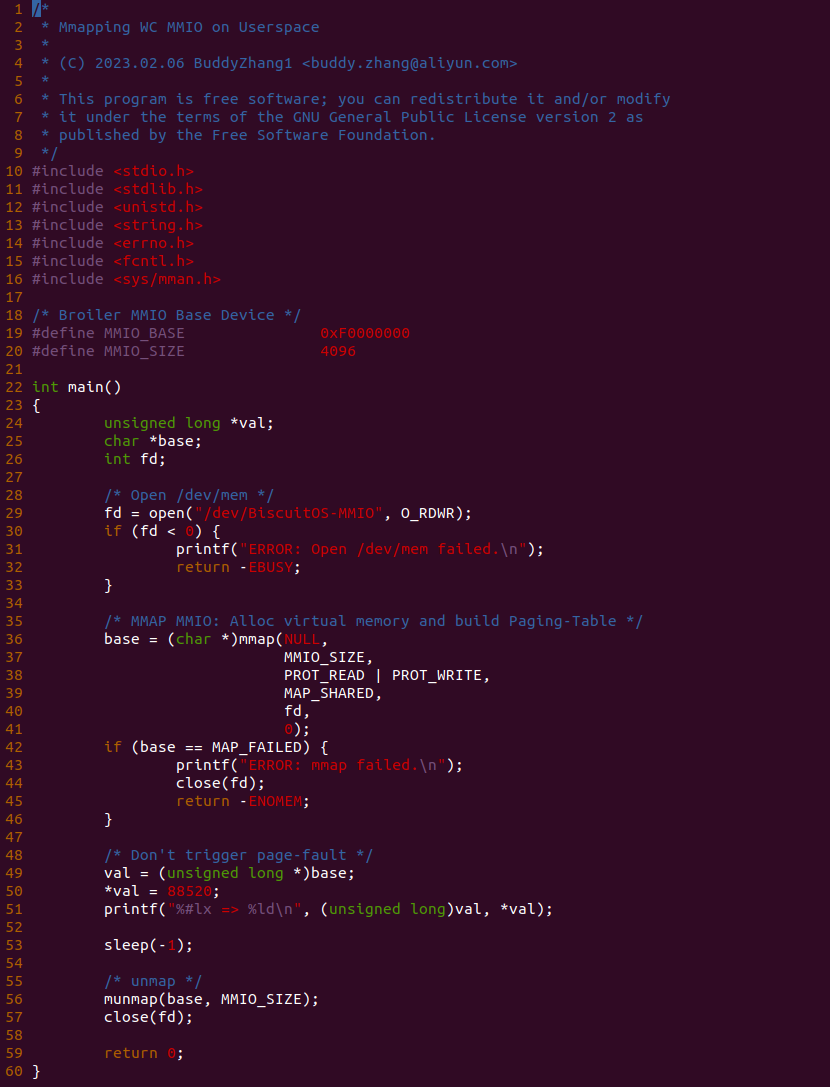

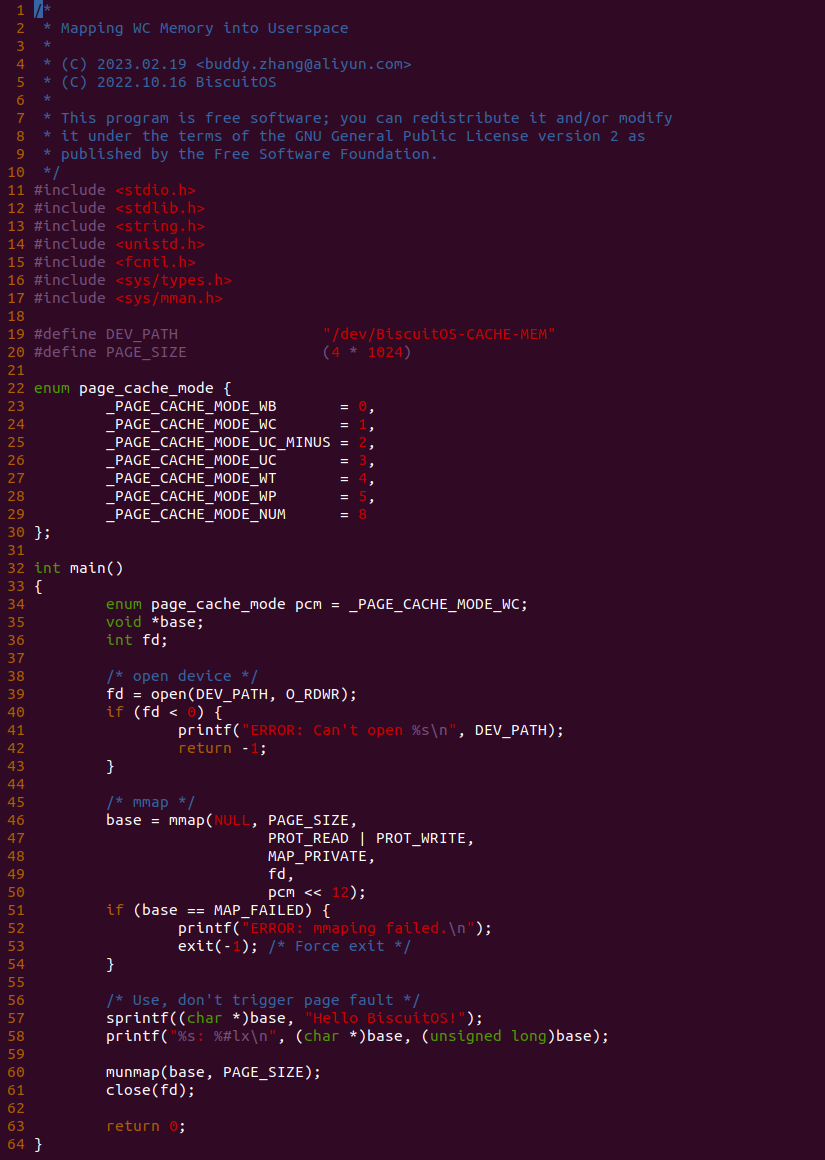

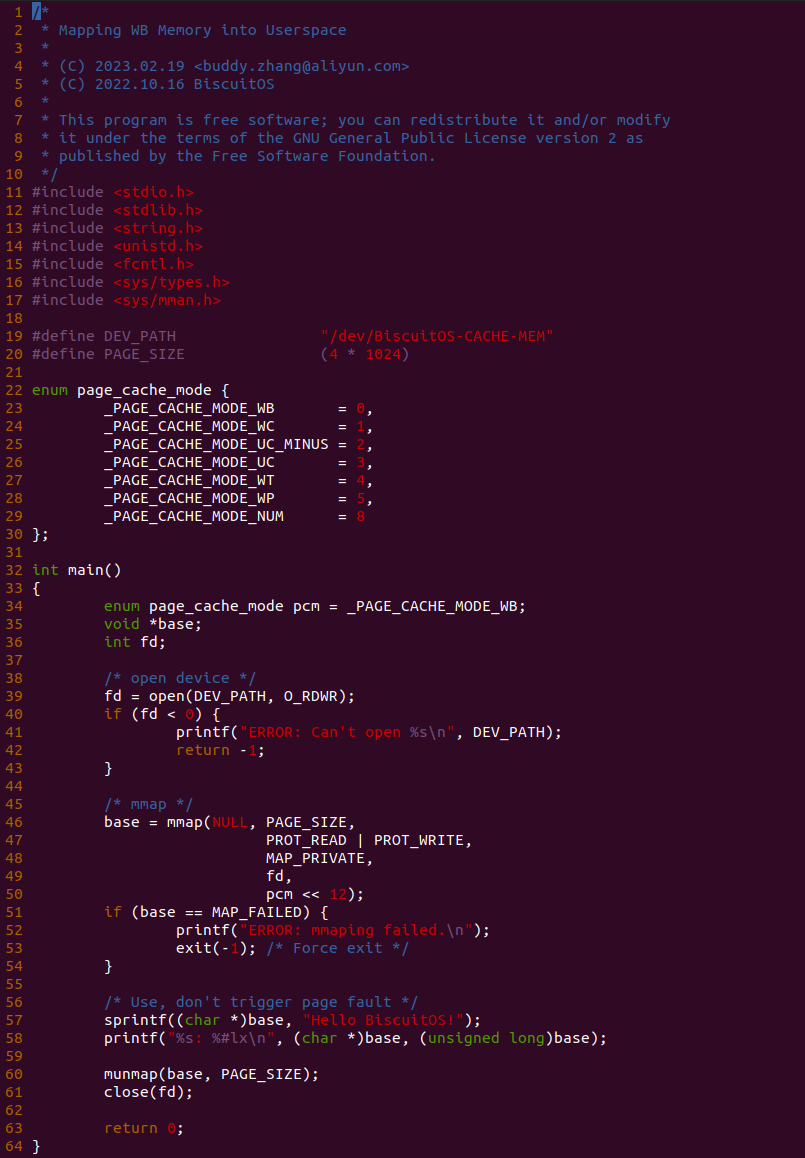

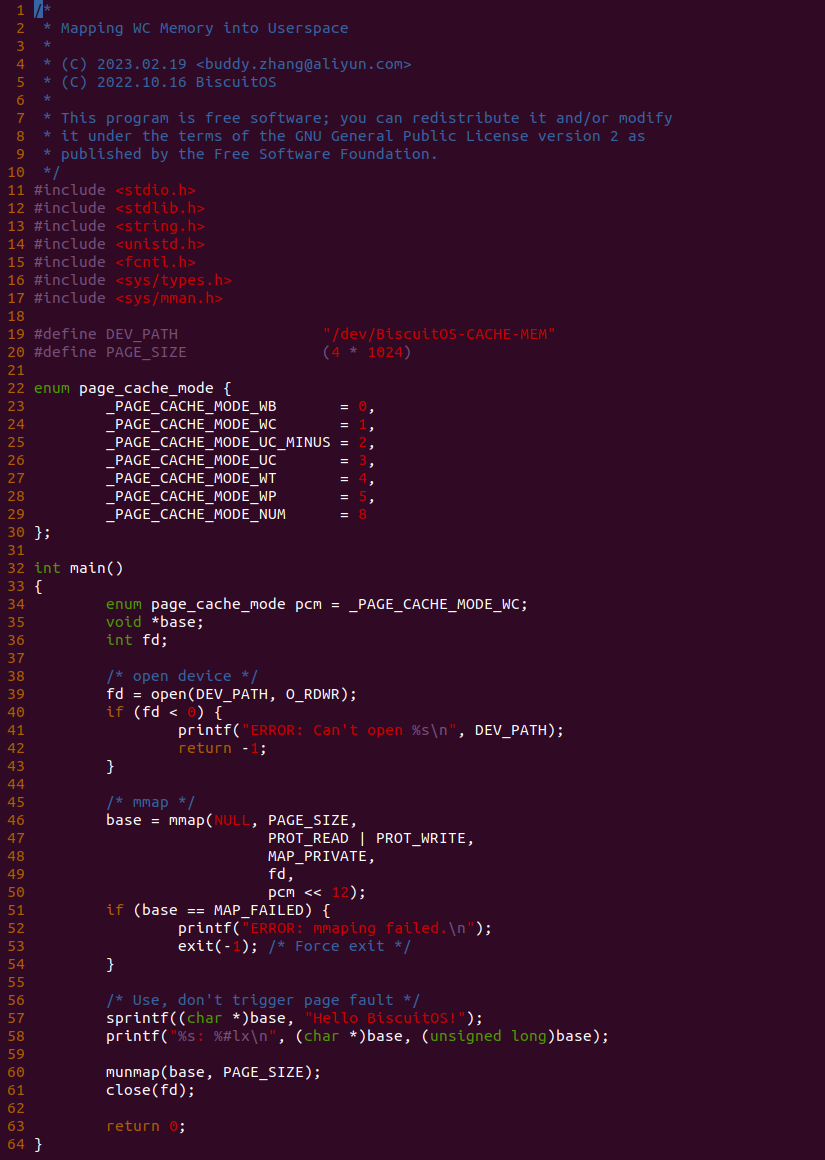

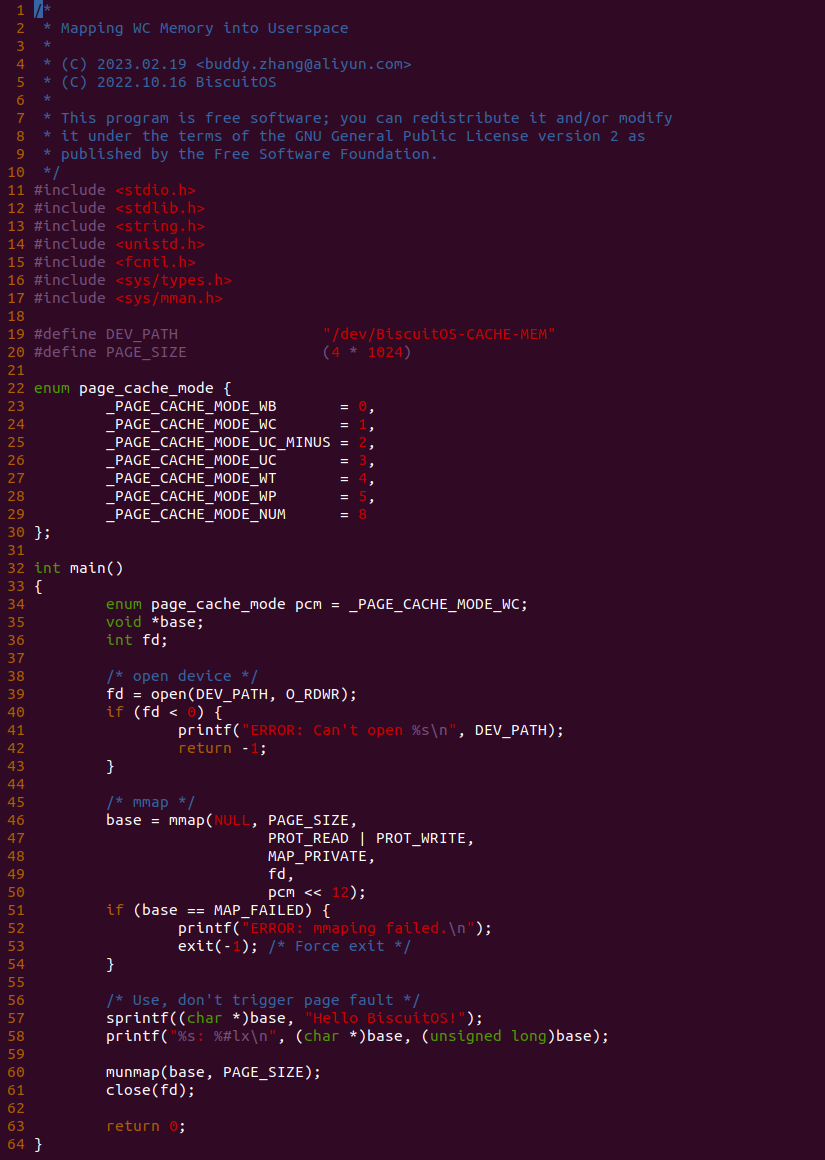

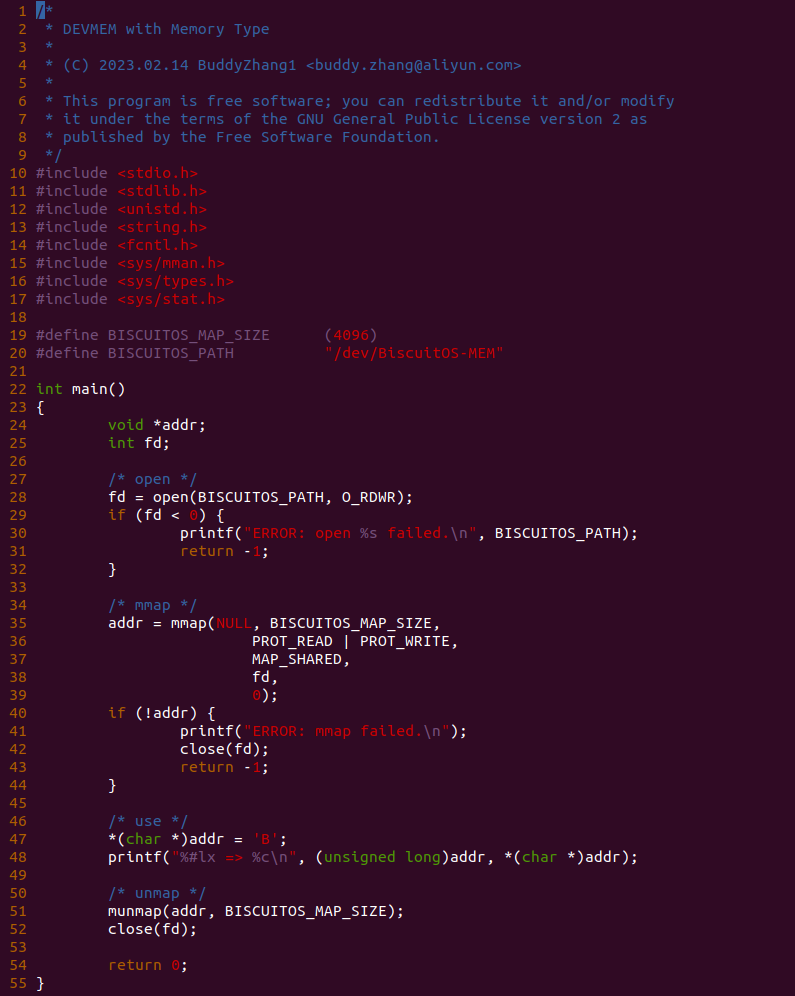

源码分成两部分,其中一部分为用户空间程序(上图所示), 用户空间代码的主要功能是映射一段虚拟内存,并将其缓存类型设置为 WC. 函数首先在 34 行将 pcm 变量设置为 _PAGE_CACHE_MODE_WC, 然后在 39 行打开 “/dev/BiscuitOS-CACHE” 节点,并基于该节点映射长度为 PAGE_SIZE 的虚拟内存,此时在函数 50 行将 pcm 传入到 mmap() 函数,映射完毕后函数在 58-59 行使用 WC 的内存,使用完毕在 61-62 行解除映射并关闭文件。

BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default Source Code on Gitee

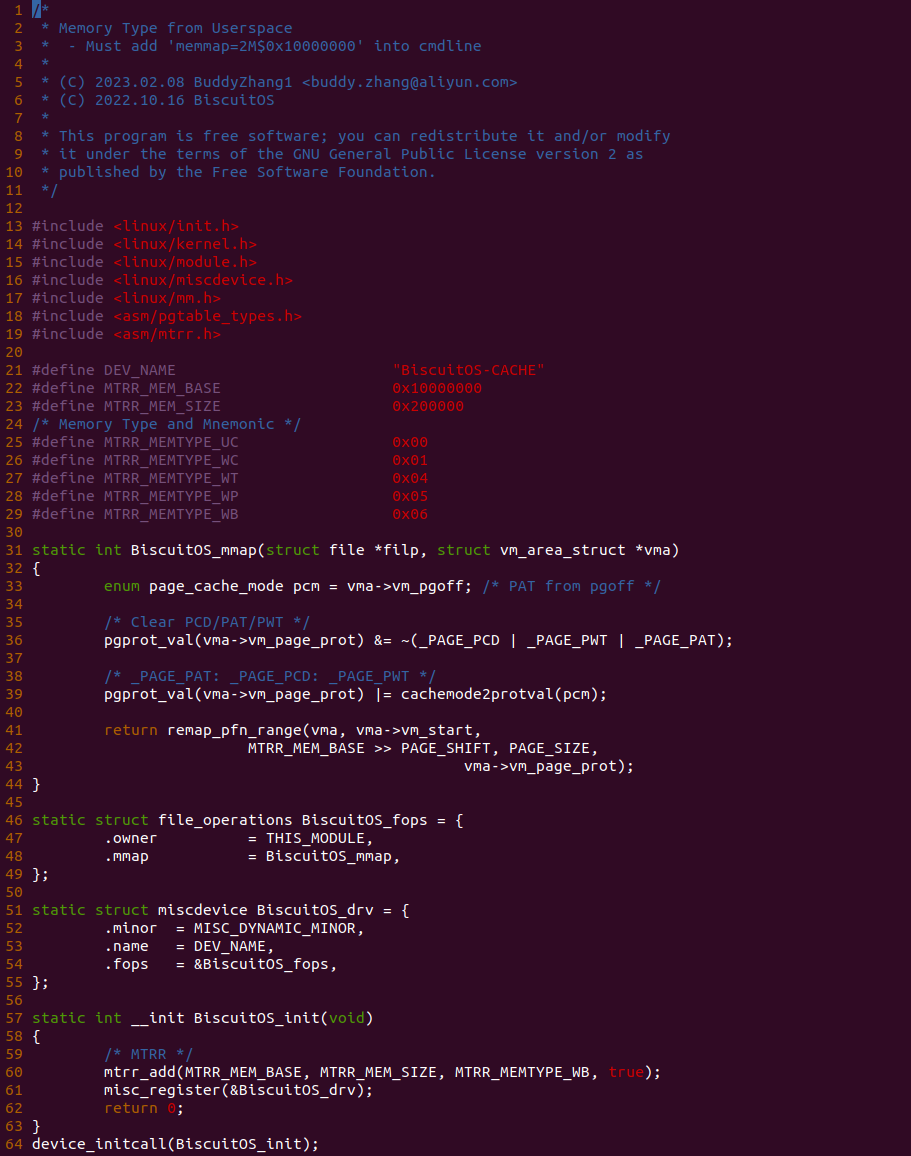

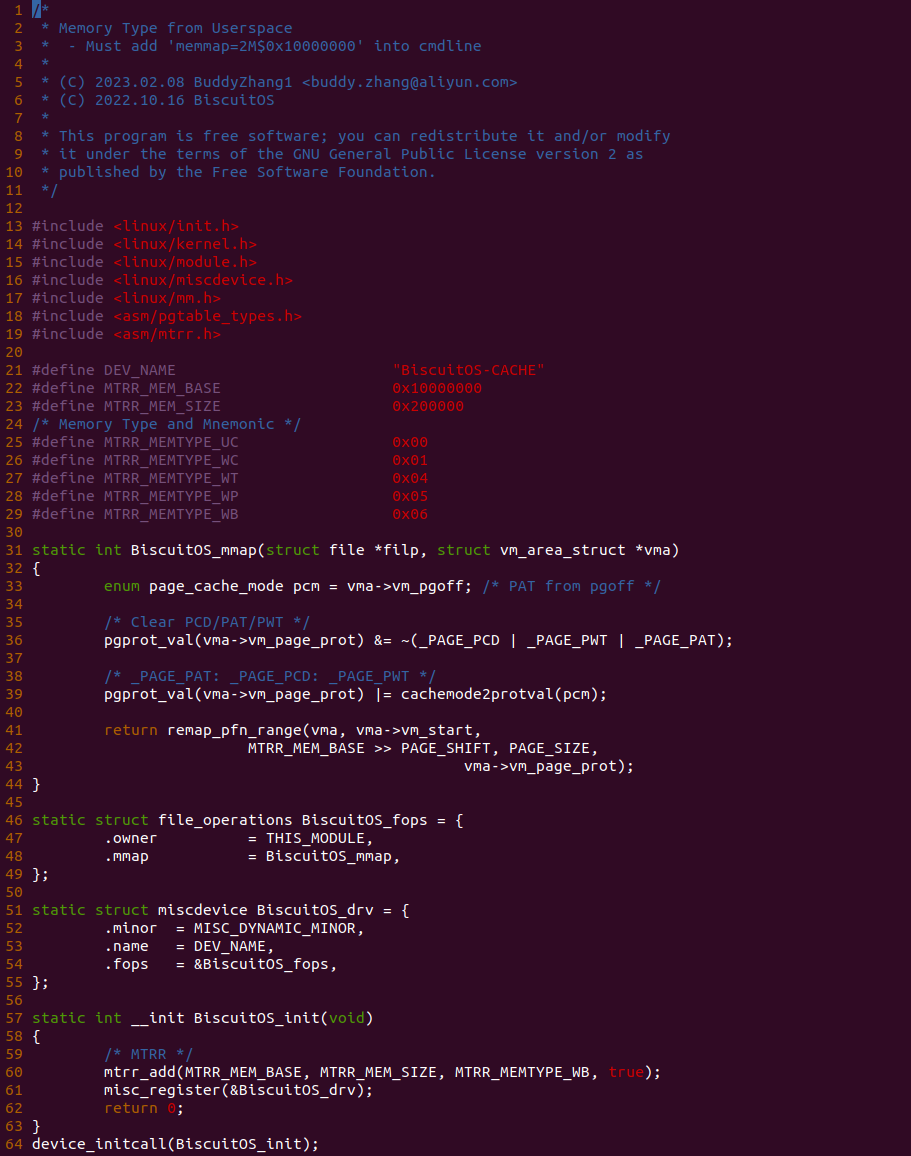

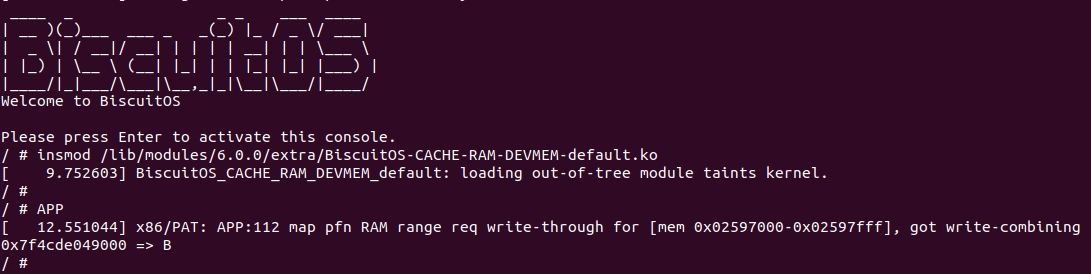

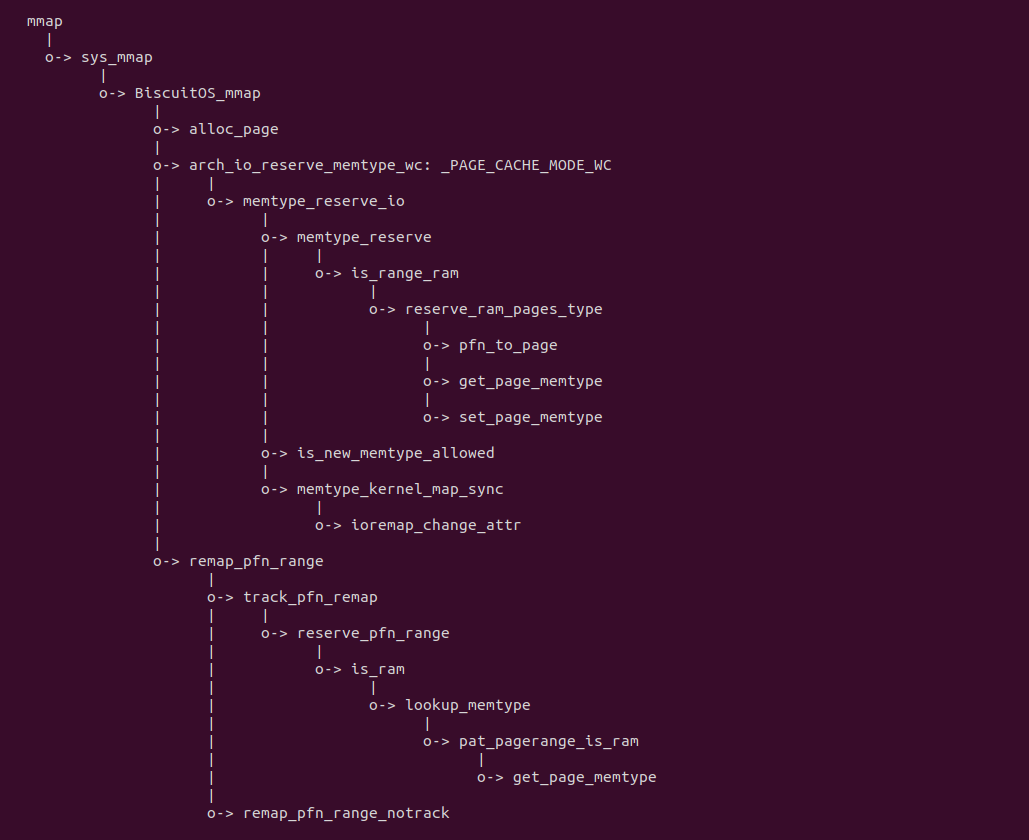

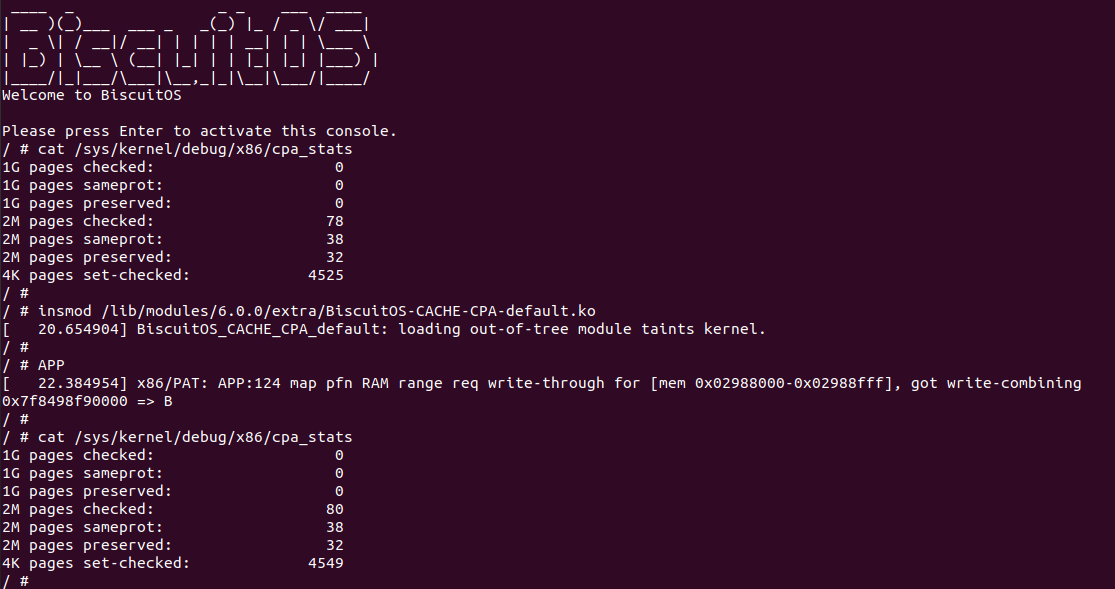

源码的另外一部分位于内核空间,其主要功能是进行实际的映射任务。模块通过一个 MISC 驱动进行实现,其提供了 mmap 接口 BiscuitOS_mmap(), 当用户空间基于 “/dev/BiscuitOS-CACHE” 节点调用 mmap() 函数时,BiscuitOS_mmap() 函数就会别调用。模块首先在 60 行调用 mtrr_add() 函数将 [MTRR_MEM_BASE, MTRR_MEM_SIZE + MTRR_MEM_BASE) 区域的 MTRR 设置为 WB. 模块接着在 33 行在用户空间调用 mmap() 函数时从 vma 的 vm_pgoff 成员中获得 PAGE CACHE MODE 信息,接着在 36 行将 vma_page_prot 成员中移除 _PAGE_PCD、_PAGE_PWT 和 _PAGE_PAT 属性,并在 39 行调用 cachemode2protval() 函数将 PAGE CACHE MODE 转换成对应的页表属性,并重新存储到 vma 的 vm_page_prot, 以此作为用于空间设置的 memory type 页表属性,最后模块在 41 行调用 remap_pfn_range() 函数为虚拟内存建立页表并映射到 MTRR_MEM_BASE 对应的物理内存上. 接下来在 BiscuitOS 上实践该案例:

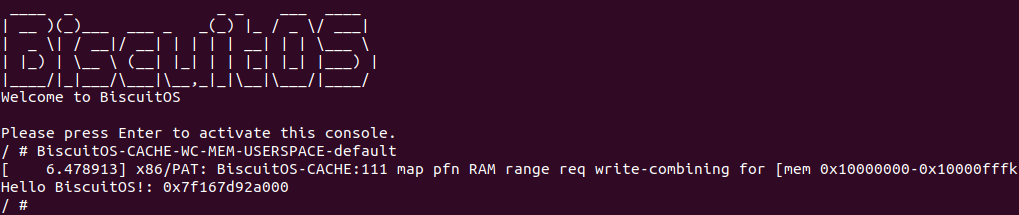

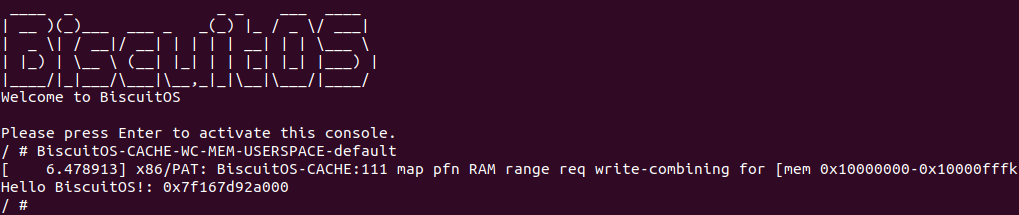

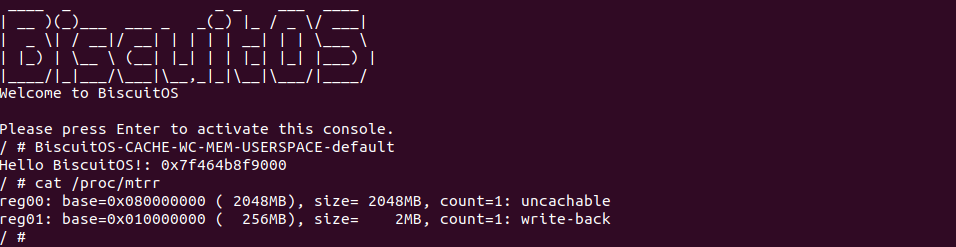

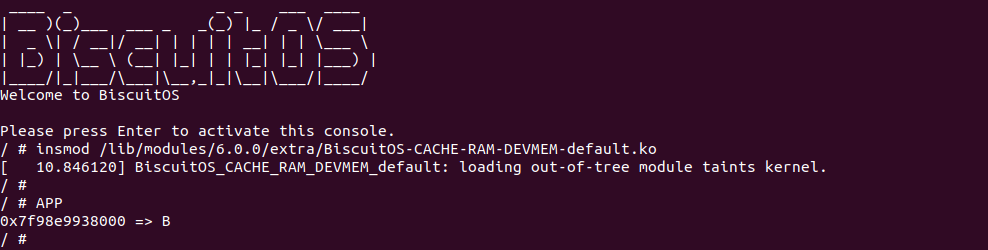

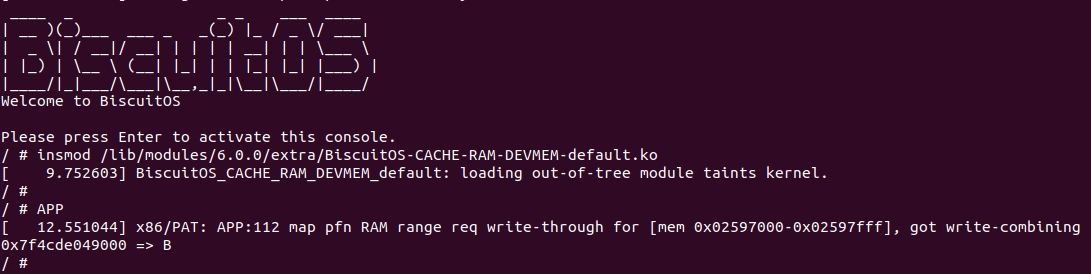

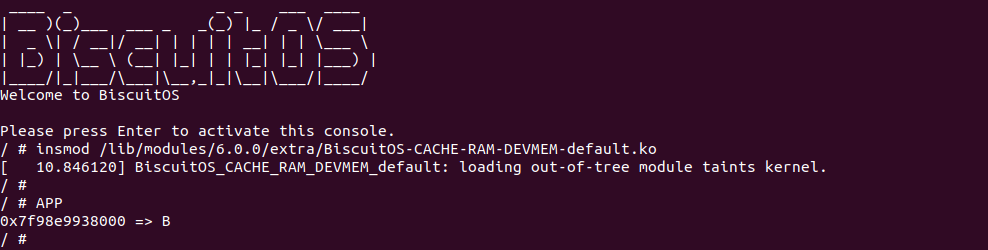

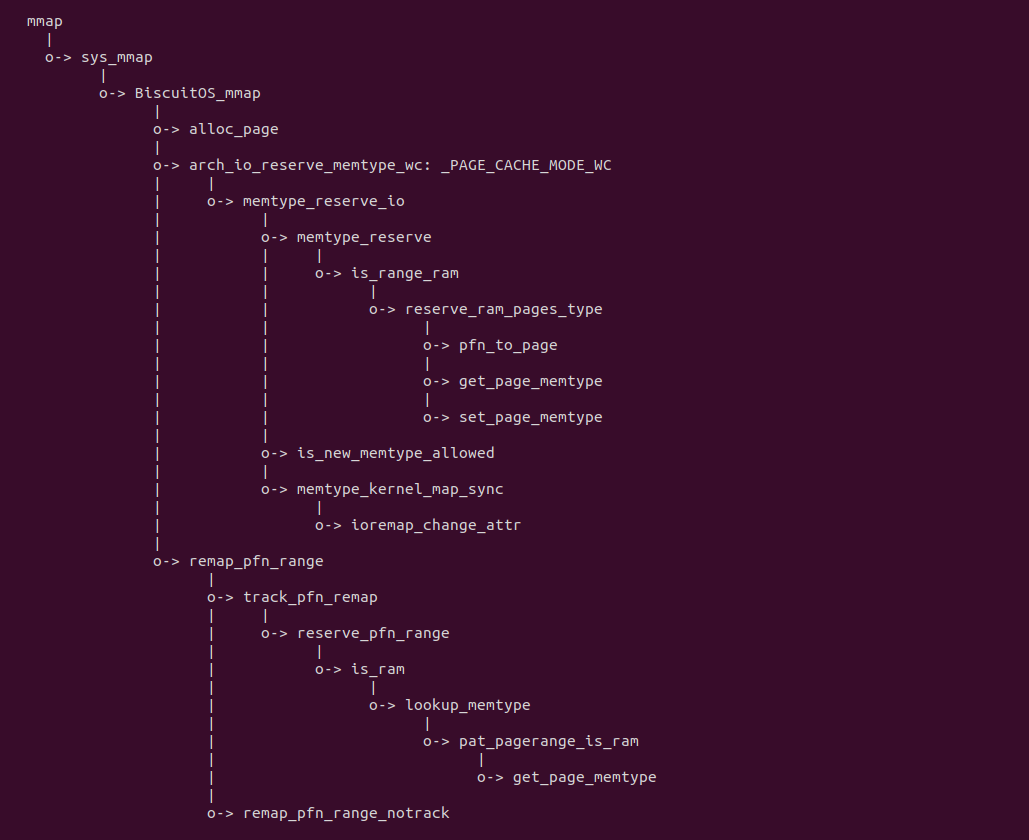

BiscuitOS 运行之后, 执行应用程序 BiscuitOS-CACHE-WC-MEM-USERSPACE-default,此时系统提示了程序预期将 [0x10000000-0x10000fff] 为 write-combining,但是系统还是将对应的 memory type 设置为 write-back, 这个与预期不符合. 查看内核模块源码的 3 行提示需要将 [0x10000000, 0x10200000) 进行预留,那么在 CMDLINE(CMDLINE 位于 RunBiscuitOS.sh 文件中) 中添加预留字段后再次实践:

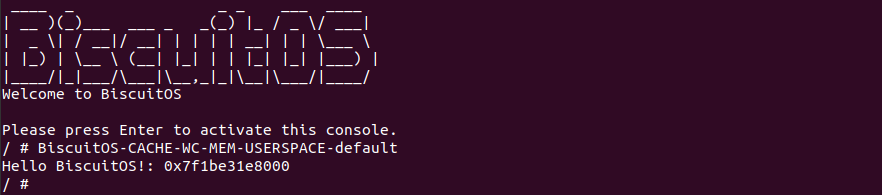

BiscuitOS 在次运行之后,运行应用程序,可以看到系统没有再提示修改信息了,那么用户进程已经成功将一段物理内存的 memory type 设置为 WC. 实践符合预期,那么接下来实践内核空间虚拟地址映射 WC 物理内存:

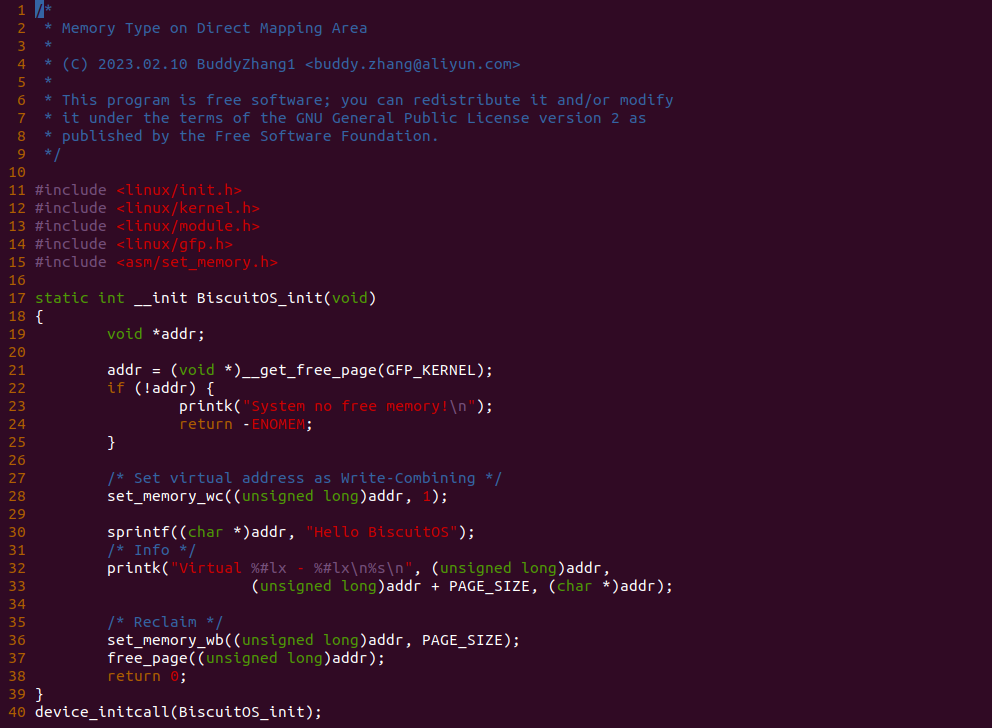

内核空间虚拟内存映射 WC 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] WriteCombining(WC): Mapping WC Memory on Kernel --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WC-MEM-KERNEL-default/

# 部署源码

make download

# 在 BiscuitOS 中实践

make build

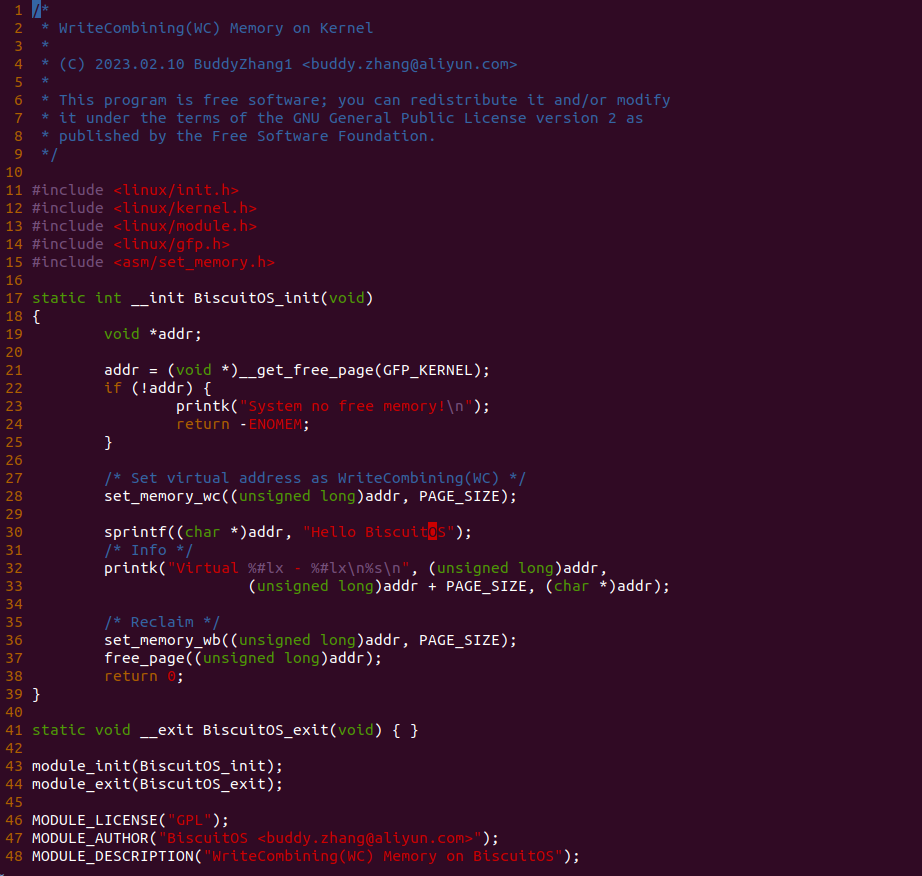

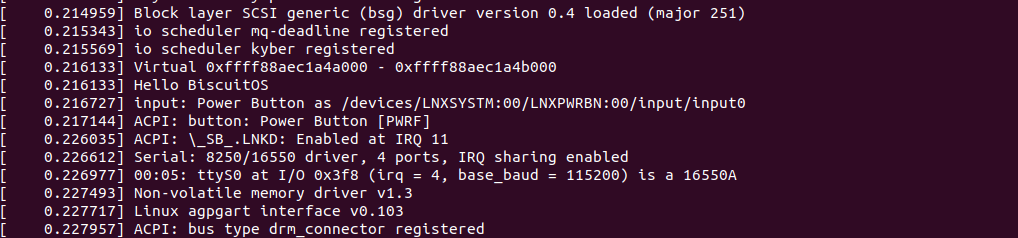

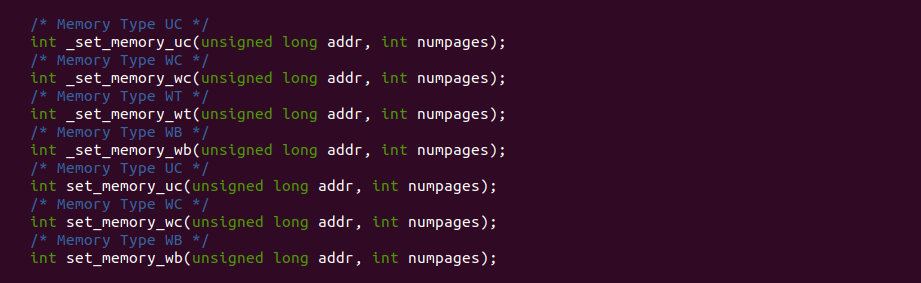

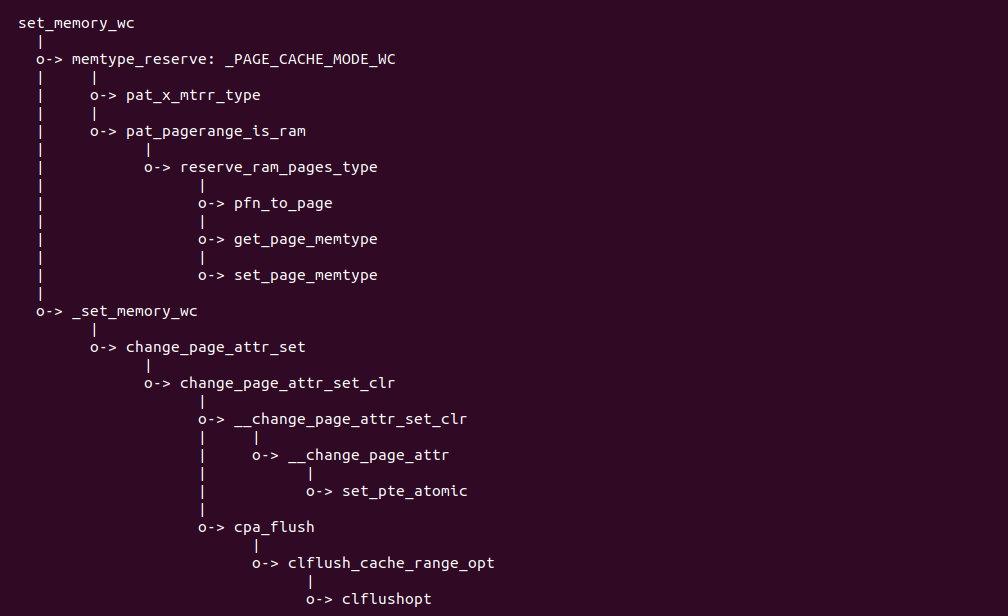

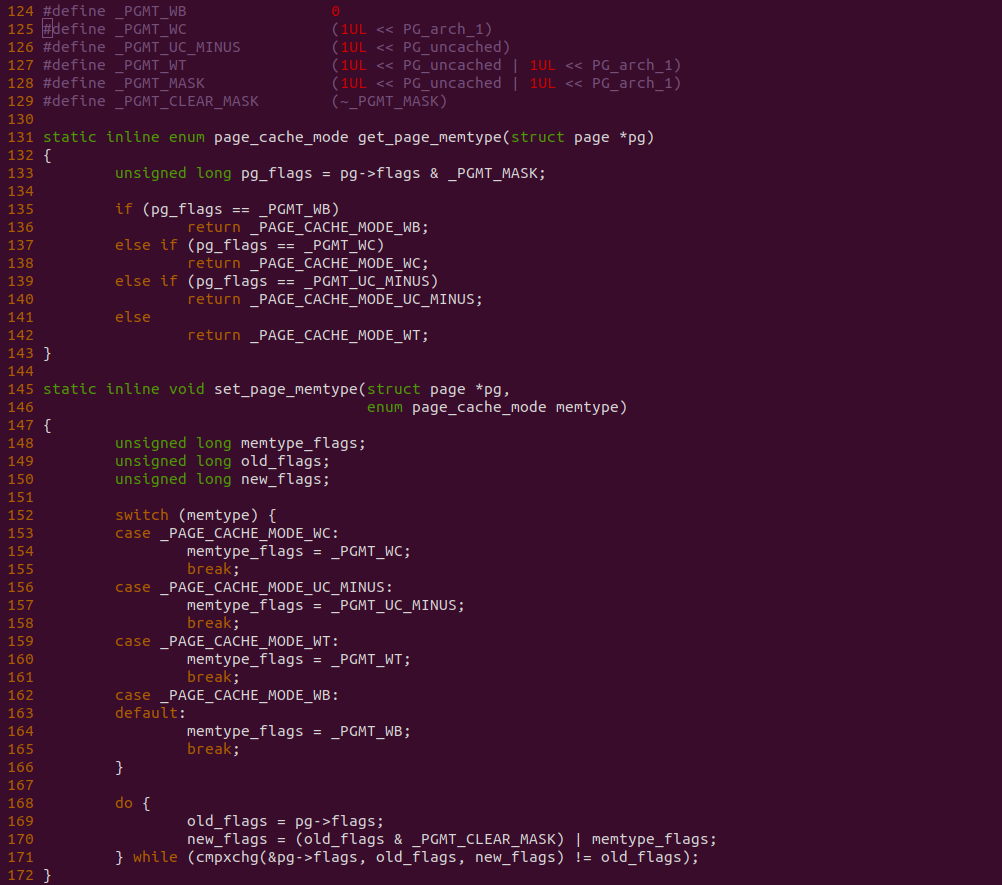

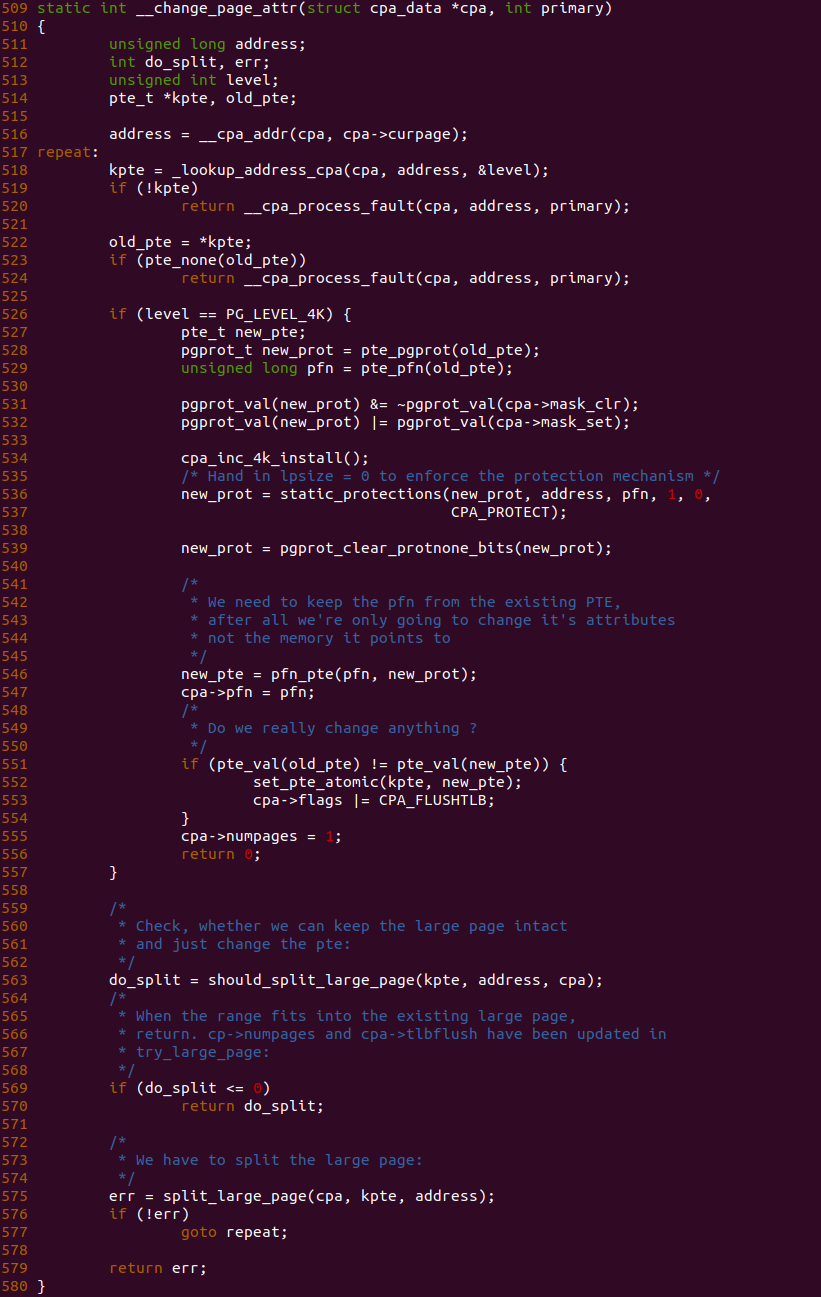

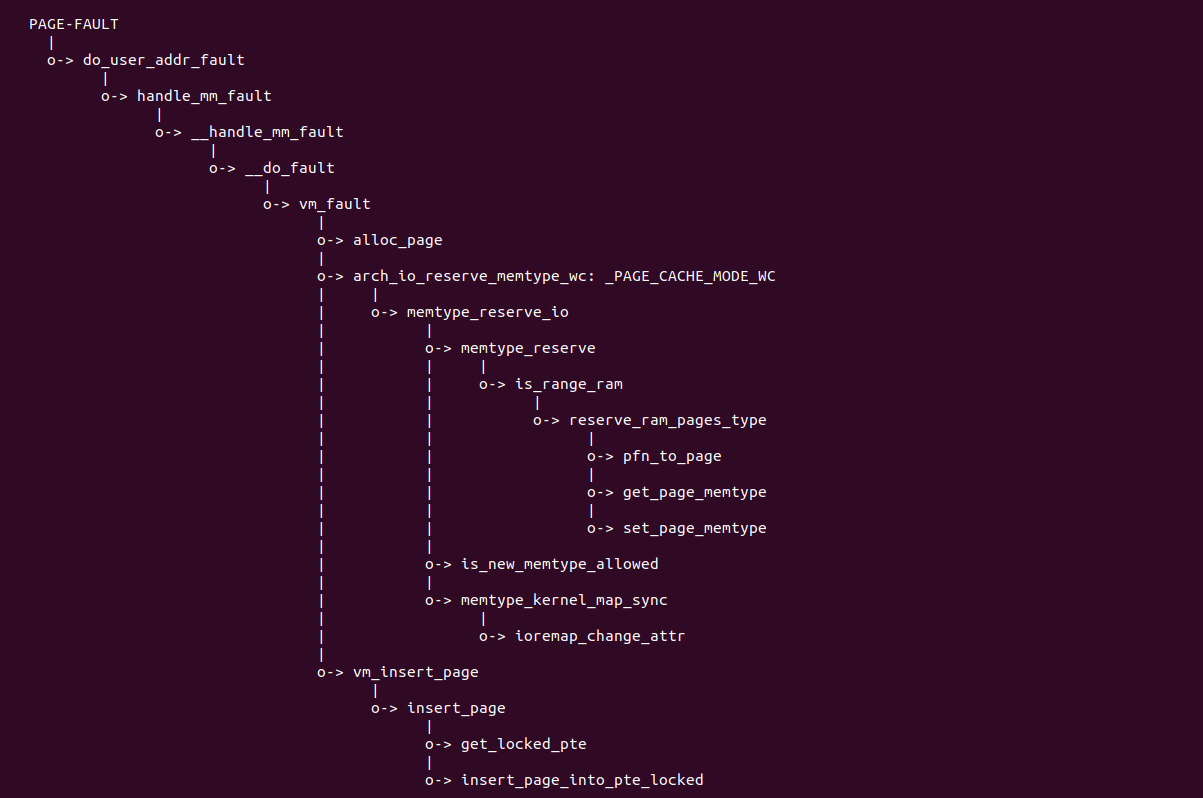

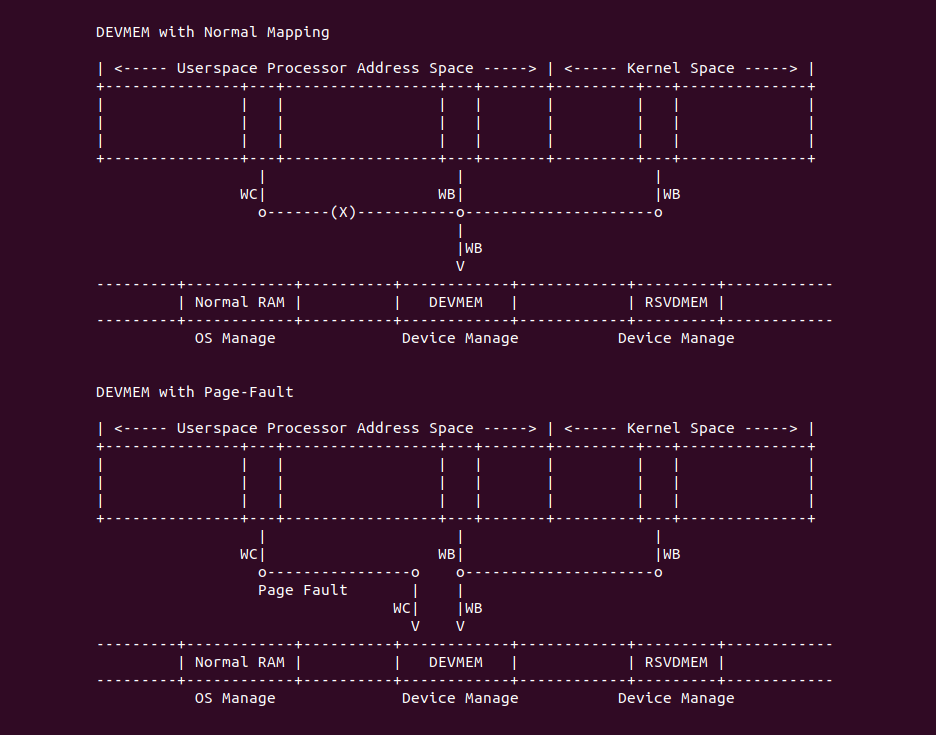

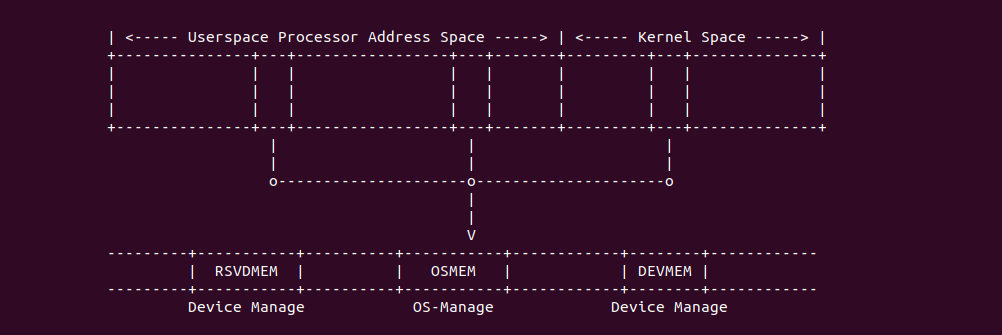

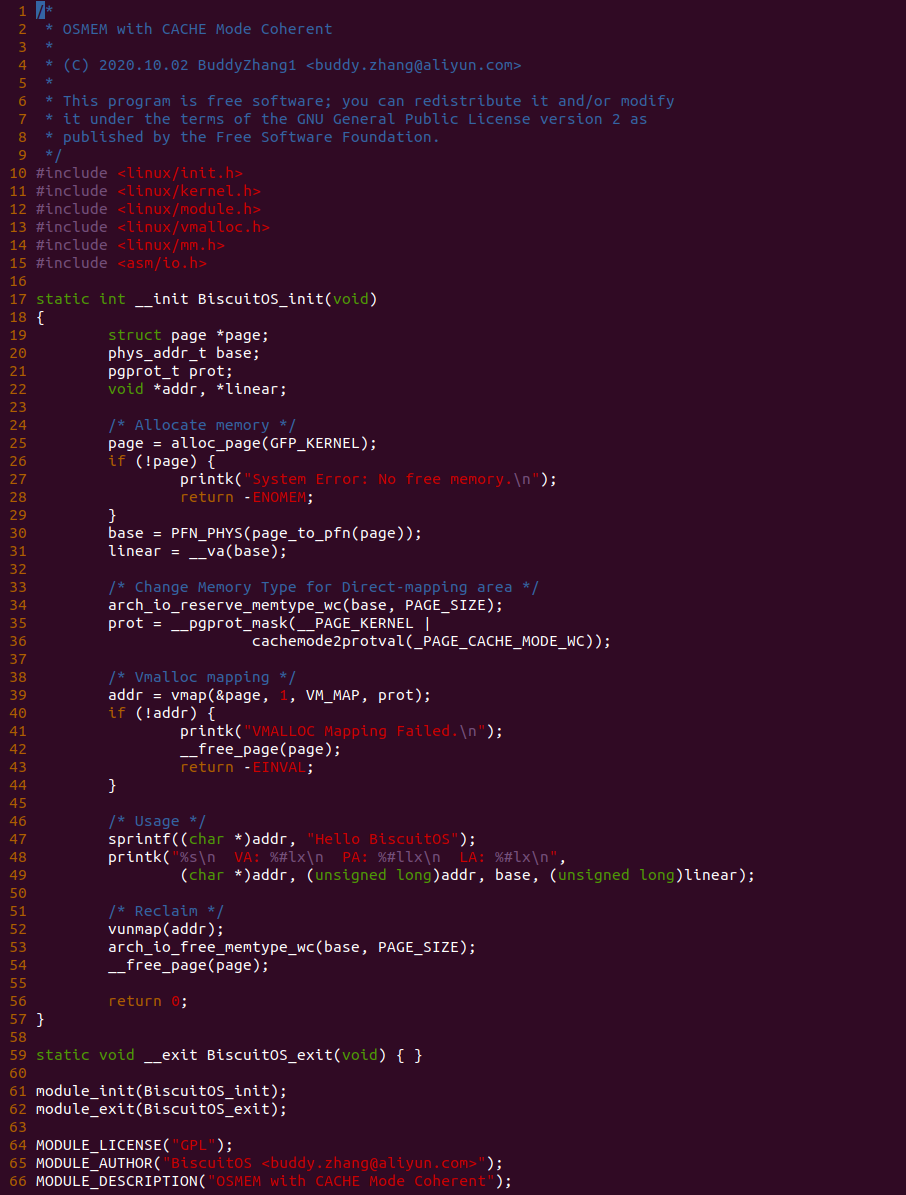

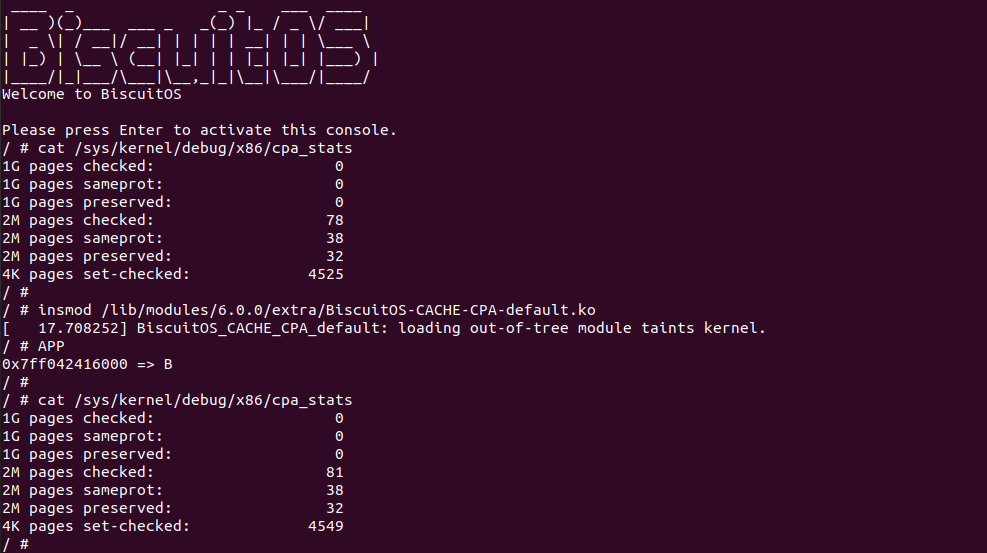

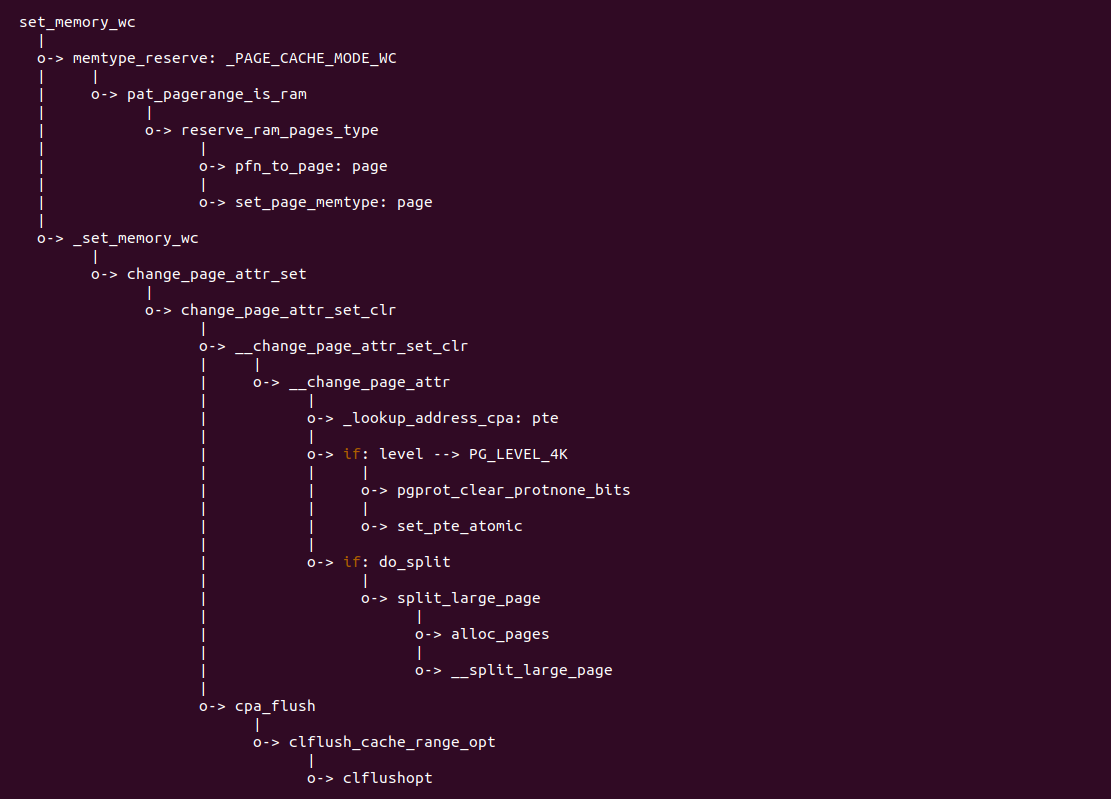

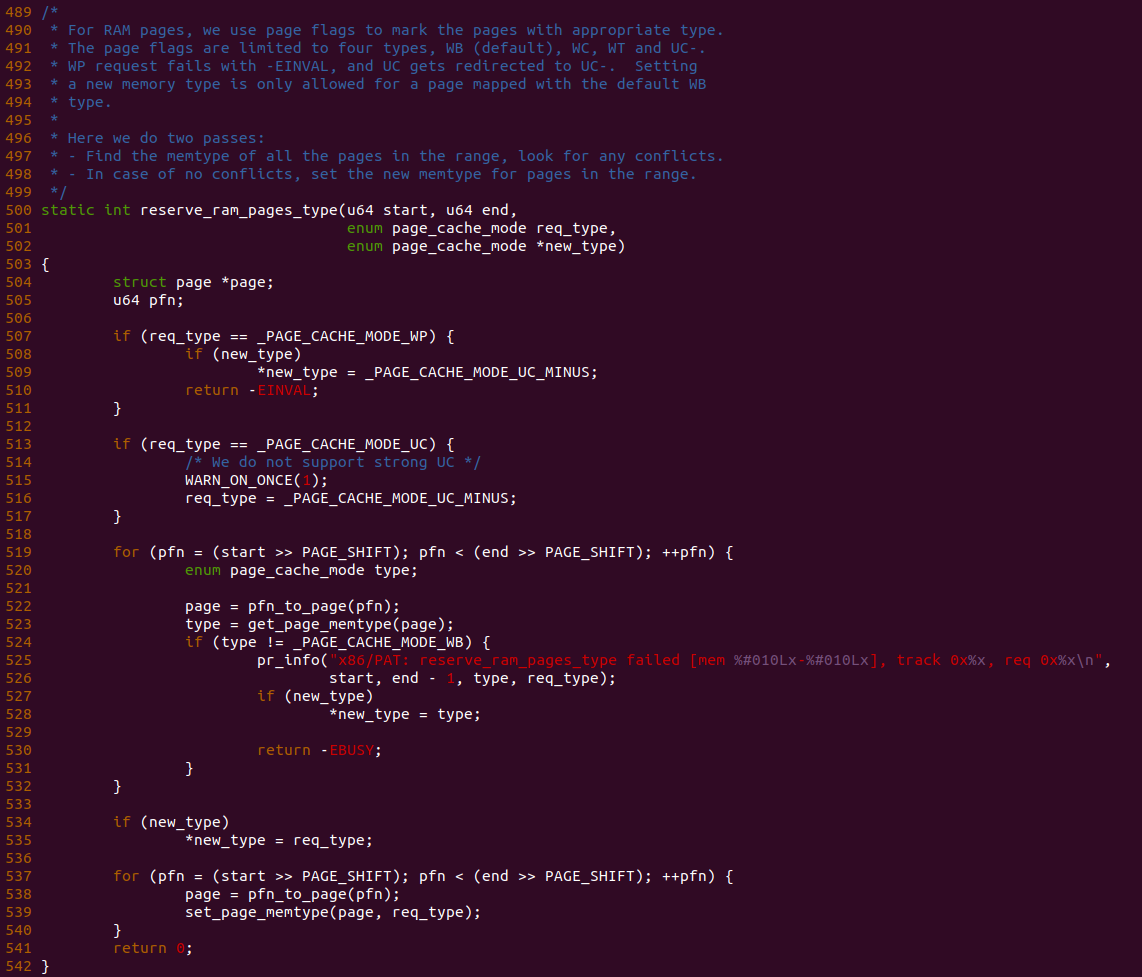

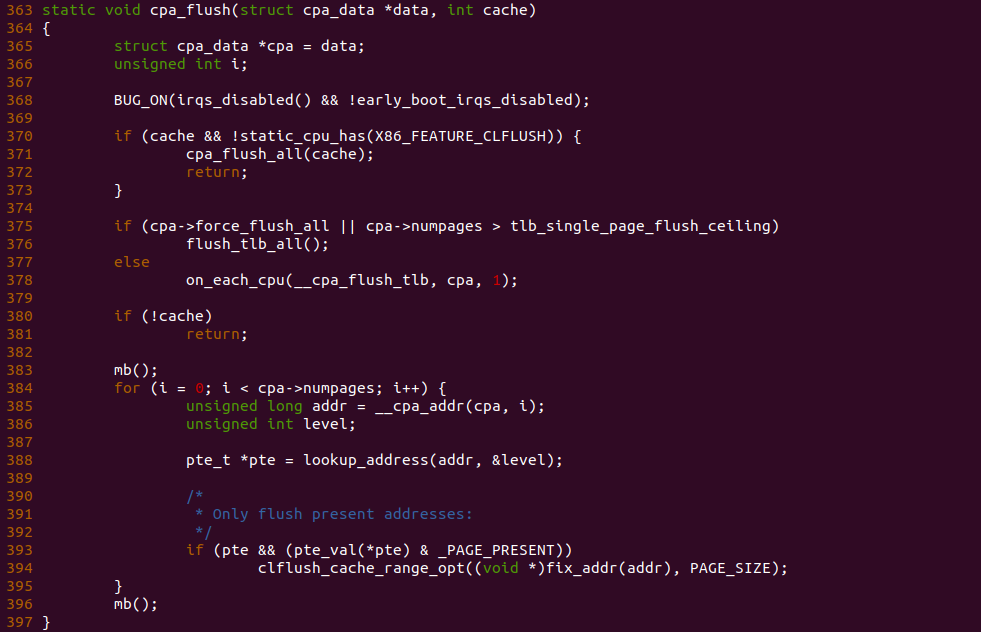

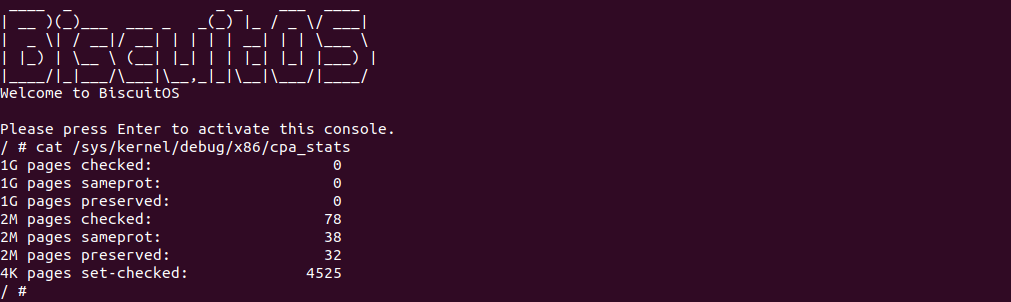

实践案例主要目的是在内核空间申请一段内存之后,将对应的虚拟地址以 WC 的方式映射到物理内存,并进行访问。案例在 21-25 行通过 __get_free_page() 函数分配一个物理页并获得对应的虚拟地址,然后在 28 行调用 set_memory_wc() 函数进行 WC 方式的映射,案例接着在 30-33 行对映射之后的虚拟地址进行访问。最后在 36-37 行回收设置,值得注意的是当将内核空间虚拟地址设置为非 WB 之后,在回收时要主动设置为 WB, 接下来在 BiscuitOS 上实践该案例:

BiscuitOS 运行之后,加载 BiscuitOS-CACHE-WC-MEM-KERNEL-default.ko 模块,可以看到系统可以使用 WC 的虚拟内存,并打印字符串 “Hello BiscuitOS”, 符合预期.

Write-Through (WT)

Write Through (WT): 通写类型,该类型会缓存读写请求。当 Read CACHE Hit 时直接从 CACHE Line 中读取数据,当 Read CACHE Miss 时先进行 CACHE Fill,然后再从 CACHE Line 中读取数据; 当 Write CACHE Hit 时,即更新 CACHE Line 的数据,也更新 Memory 中的数据, 当 Write CACHE Miss 时不会 CACHE Fills,而是直接更新 Memory 中的数据. 当 WT 类型时预测读是允许的,并且 Write Combining 也是允许的。WT 类型通常应用于 Frame Buffer 或者会访问内存的设备,这类设备会访问总线,但没有监听总线的能力. WT 强制遵循 CACHE 一致性原理. 那么接下来通过一组实践案例介绍内核和用户空间如何使用 WT 类型的内存:

内核空间虚拟地址映射 WT MMIO

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support BiscuitOS Hardware Emulate

[*] CACHE --->

[*] WriteThrough(WT): Mapping WT MMIO on Kernel --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WT-MMIO-KERNEL-default

# 部署源码

make download

# 在 BiscuitOS/Broiler 中实践

make broilerBiscuitOS-CACHE-UNCACHE-WT-KERNEL-default Source Code on Gitee

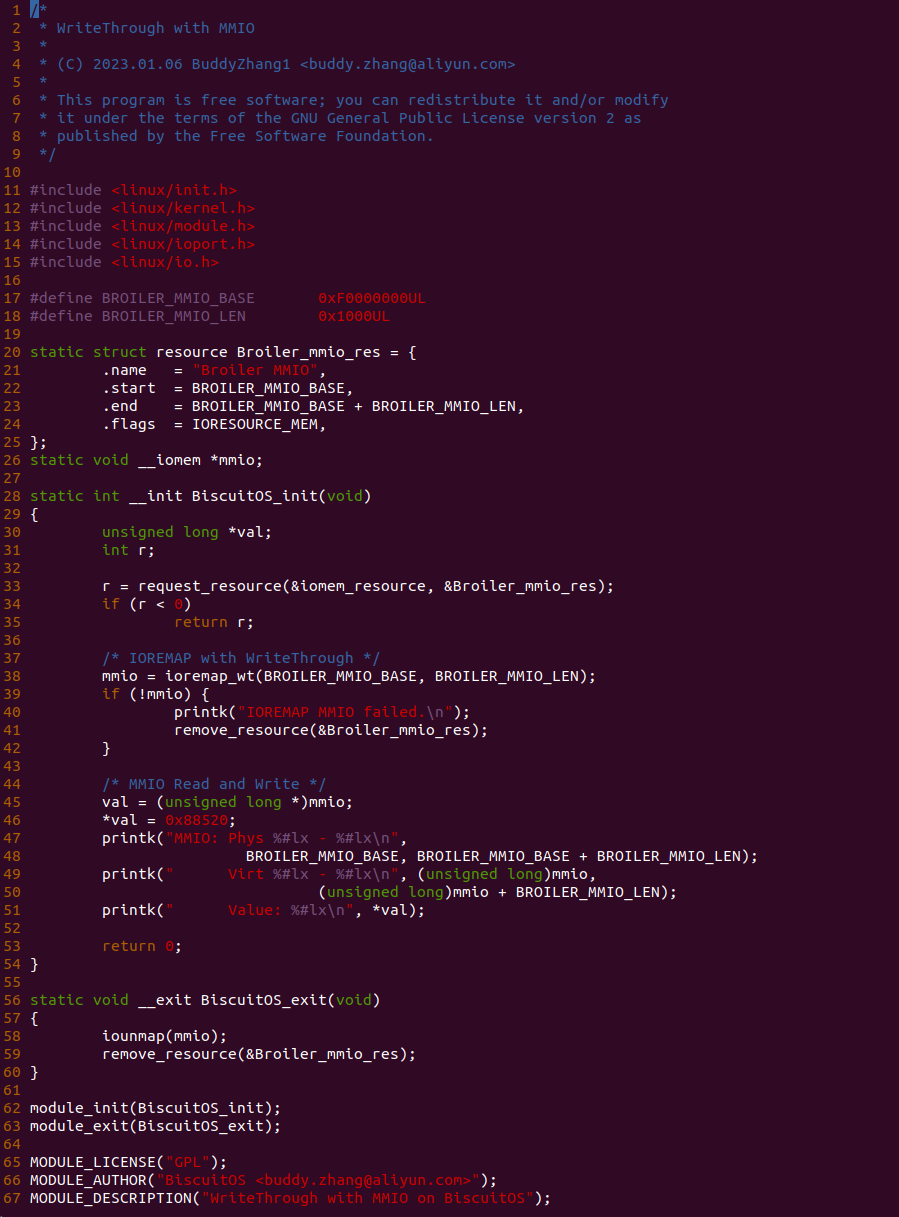

源码通过一个内核模块进行展示,模块有两部分组成,第一部分是 20-35 行,模块向系统资源总线注册了一段 MMIO,这段 MMIO 起始物理地址是 BROILER_MMIO_BASE, 长度为 BROILER_MMIO_LEN, 注册完毕之后可以在系统启动之后,通过 ‘/proc/iomem’ 接口查看到该段信息; 第二部分是 38-46 行,模块在 38 行调用 ioremap_wt() 函数将 BROILER_MMIO_BASE 开始且长度为 BROILER_MMIO_LEN 的 MMIO 区域,映射为 Write-Through 的 memory type, 映射完毕之后函数在 46 行对 MMIO 进行访问,此时并不会触发缺页,因为 ioremap_wt() 函数已为 MMIO 分配了对应的虚拟地址并建立了页表,因此模块可以直接访问 MMIO. 最后在 BiscuitOS 上实践模块,由于需要一段真实的 MMIO 才能运行模块,因此可使用 Broiler 模拟一段 MMIO,其起始物理地址为 0xF0000000(Broiler 已经模拟好硬件),开发者直接在源码目录执行 make broiler 即可:

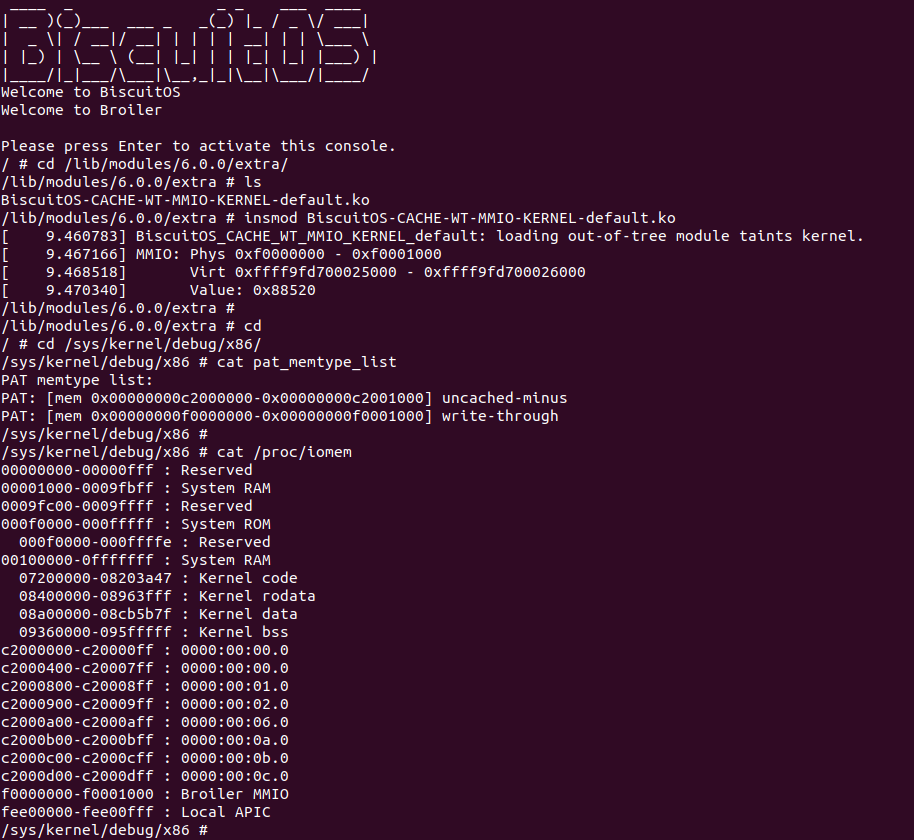

BiscuitOS 运行之后,加载 BiscuitOS-CACHE-WT-MMIO-KERNEL-default.ko 模块之后,从打印的内核信息可以看出模块已经映射了 MMIO,并且向 MMIO 写入 0x88520 之后可以读出正确的数据,最后查看 ‘/sys/kernel/debug/x86/pat_memtype_list’ 节点查看系统 MMIO memory_type 信息,可以看到模块映射的 MMIO [0xF0000000, 0xF0001000] 为 write-through, 另外查看 ‘/proc/iomem’ 节点查看物理地址空间信息,可以看到 [0xF0000000, 0xF0001000) 为 Broiler MMIO 区域, 实践符合预期. 接下来一个实践案例用于介绍如何将用户空间虚拟地址映射成 WT 的 MMIO,BiscuitOS 部署逻辑如下:

用户空间虚拟地址映射 WT MMIO

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support BiscuitOS Hardware Emulate

[*] CACHE --->

[*] WriteThrough(WT): Mapping WT MMIO on Userspace --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WT-MMIO-USERSPACE-default

# 部署源码

make download

# 在 BiscuitOS/Broiler 中实践

make broilerBiscuitOS-CACHE-WT-MMIO-USERSPACE-default Source Code on Gitee

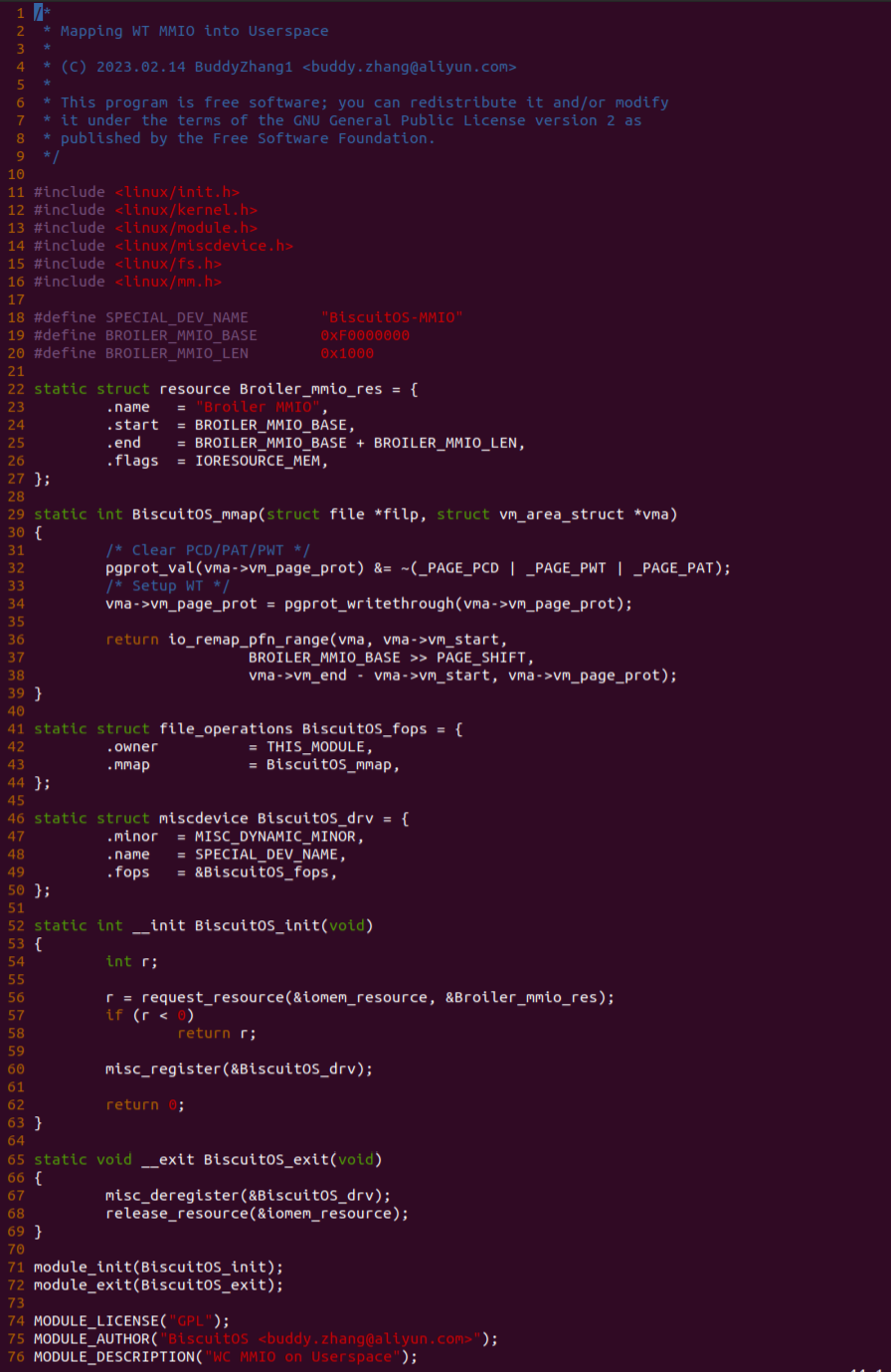

实践案例由两个部分组成,main.c 为内核模块部分,负责映射 MMIO 的底层逻辑。模块首先在 22-26 行定义了 MMIO 区域的信息,然后在 56-57 行通过调用 request_resource() 函数将 MMIO 区域添加到系统物理地址空间树里。模块通过注册一个 MISC 驱动,向用户空间提供 “/dev/BiscuitOS-MMIO” 接口,用户空间程序打开该接口,并调用 mmap() 映射 MMIO 时会调用到模块的 BiscuitOS_mmap() 函数,该函数首先在 32 行将虚拟地址对应的页表属性里的 _PAGE_PAT、_PAGE_PCD 和 _PAGE_PWT 标志清除,然后在 34 行调用 pgport_writethrough() 函数,将 WT 属性赋值到 vm_page_prot 成员,接下来调用 io_remap_pfn_range() 函数进行虚拟地址到 MMIO 的映射工作。映射完毕之后用户空间虚拟地址就可以以 WT 方式访问 MMIO.

实践案例的另外一部分位于 app.c 内,其为用户空间程序,用于映射虚拟地址到 MMIO 并进行访问. 程序首先在 29 行通过 open() 函数打开 “/dev/BiscuitOS-MMIO” 节点,然后在 36-46 通过 mmap() 函数将进程地址空间的虚拟地址映射到 MMIO,接下来在 49-51 行对映射之后对 MMIO 进行访问,最后在 56-57 行释放相应的资源. 源码分析完毕之后在 BiscuitOS 进行实践,由于 MMIO 绑定在具体的硬件上,此时可以使用 Broiler 进行模块,直接使用 “make broiler” 命令进行实践:

BiscuitOS Broiler 运行之后加载 BiscuitOS-CACHE-WT-MMIO-USERSPACE-default.ko, 接着运行用户态程序 APP,这里以后台方式运行,因此查看其他有用信息,运行之后可以看到正常访问 MMIO。接下来查看 /sys/kernel/debug/x86/pat_memtype_list 节点,可以看到 [0xF0000000, 0xF0001000) 区域映射为 write-through,最后查看 /proc/iomem 系统物理地址空间,可以看到 Broiler MMIO 对应的区域正好是 [0xF0000000, 0xF0001000)。实践结果符合预期. 那么接下来对普通物理内存映射为 WC 场景进行实践:

用户空间虚拟内存映射 WT 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] WriteThrough(WT): Mapping WT Memory on Userspace --->

-*- CACHE User-Page for Kernel Stub (Basic) --->

# 进入源码目录

# Userspace: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WT-MEM-USERSPACE-default/

# Kernel: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default/

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WT-MEM-USERSPACE-default/

# 部署源码

make prepare

make download

# 在 BiscuitOS 中实践

make buildBiscuitOS-CACHE-WT-MEM-USERSPACE-default Source Code on Gitee

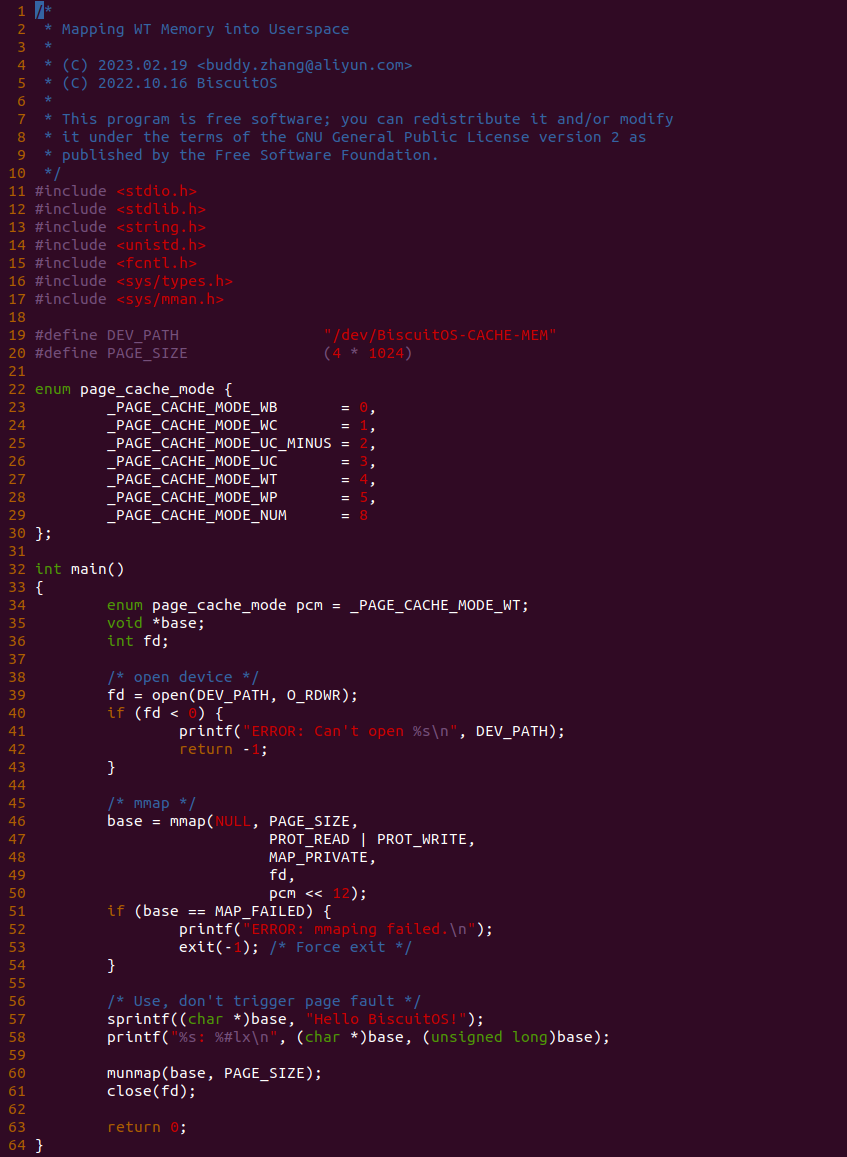

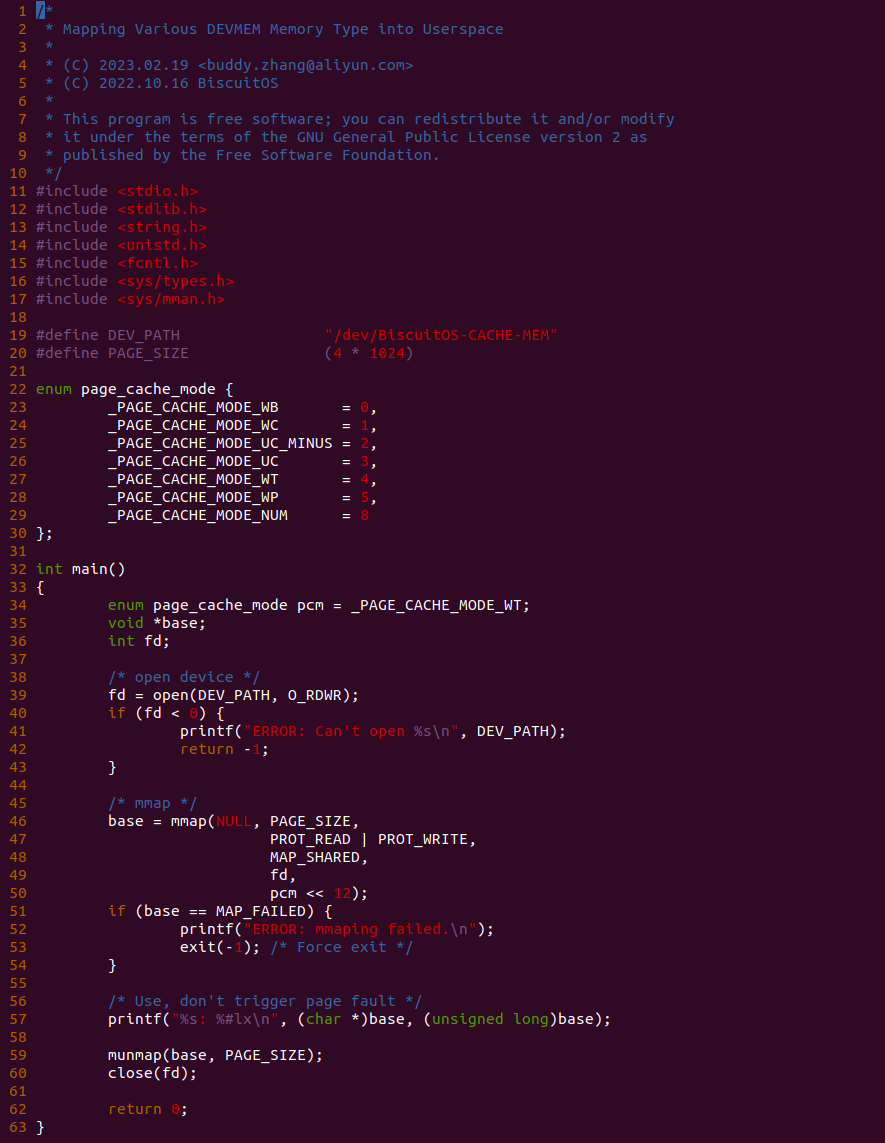

源码分成两部分,其中一部分为用户空间程序(上图所示), 用户空间代码的主要功能是映射一段虚拟内存,并将其缓存类型设置为 WT. 函数首先在 34 行将 pcm 变量设置为 _PAGE_CACHE_MODE_WT, 然后在 39 行打开 “/dev/BiscuitOS-CACHE” 节点,并基于该节点映射长度为 PAGE_SIZE 的虚拟内存,此时在函数 50 行将 pcm 传入到 mmap() 函数,映射完毕后函数在 58-59 行使用 WT 的内存,使用完毕在 61-62 行解除映射并关闭文件。

BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default Source Code on Gitee

源码的另外一部分位于内核空间,其主要功能是进行实际的映射任务。模块通过一个 MISC 驱动进行实现,其提供了 mmap 接口 BiscuitOS_mmap(), 当用户空间基于 “/dev/BiscuitOS-CACHE” 节点调用 mmap() 函数时,BiscuitOS_mmap() 函数就会别调用。模块首先在 60 行调用 mtrr_add() 函数将 [MTRR_MEM_BASE, MTRR_MEM_SIZE + MTRR_MEM_BASE) 区域的 MTRR 设置为 WB. 模块接着在 33 行在用户空间调用 mmap() 函数时从 vma 的 vm_pgoff 成员中获得 PAGE CACHE MODE 信息,接着在 36 行将 vma_page_prot 成员中移除 _PAGE_PCD、_PAGE_PWT 和 _PAGE_PAT 属性,并在 39 行调用 cachemode2protval() 函数将 PAGE CACHE MODE 转换成对应的页表属性,并重新存储到 vma 的 vm_page_prot, 以此作为用于空间设置的 memory type 页表属性,最后模块在 41 行调用 remap_pfn_range() 函数为虚拟内存建立页表并映射到 MTRR_MEM_BASE 对应的物理内存上. 接下来在 BiscuitOS 上实践该案例:

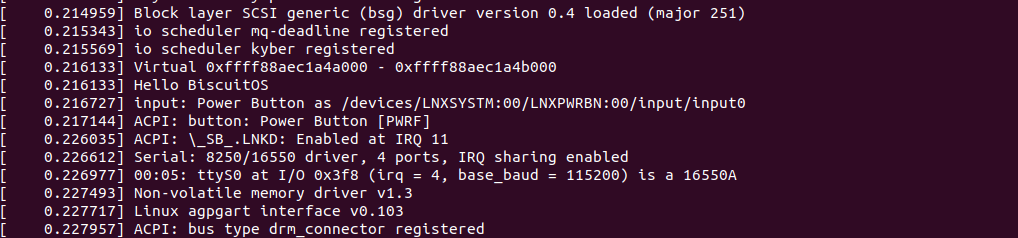

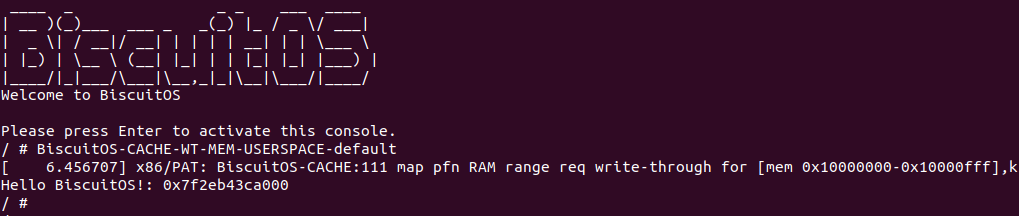

BiscuitOS 运行之后, 执行应用程序 BiscuitOS-CACHE-WT-MEM-USERSPACE-default,此时系统提示了程序预期将 [0x10000000-0x10000fff] 为 write-through,但是系统还是将对应的 memory type 设置为 write-back, 这个与预期不符合. 查看内核模块源码的 3 行提示需要将 [0x10000000, 0x10200000) 进行预留,那么在 CMDLINE(CMDLINE 位于 RunBiscuitOS.sh 文件中) 中添加预留字段后再次实践:

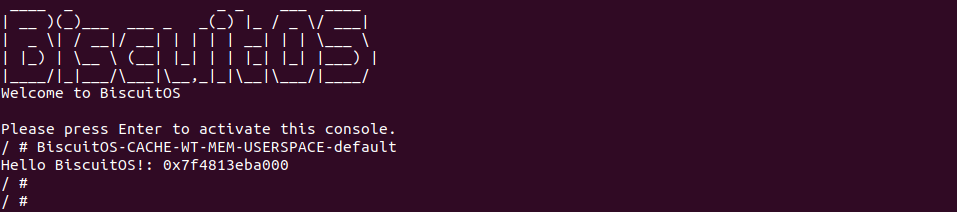

BiscuitOS 在次运行之后,运行应用程序,可以看到系统没有再提示修改信息了,那么用户进程已经成功将一段物理内存的 memory type 设置为 WT. 实践符合预期,那么接下来实践内核空间虚拟地址映射 WT 物理内存:

内核空间虚拟内存映射 WT 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] WriteThrough(WT): Mapping WT Memory on Kernel --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WT-MEM-KERNEL-default/

# 部署源码

make download

# 在 BiscuitOS 中实践

make build

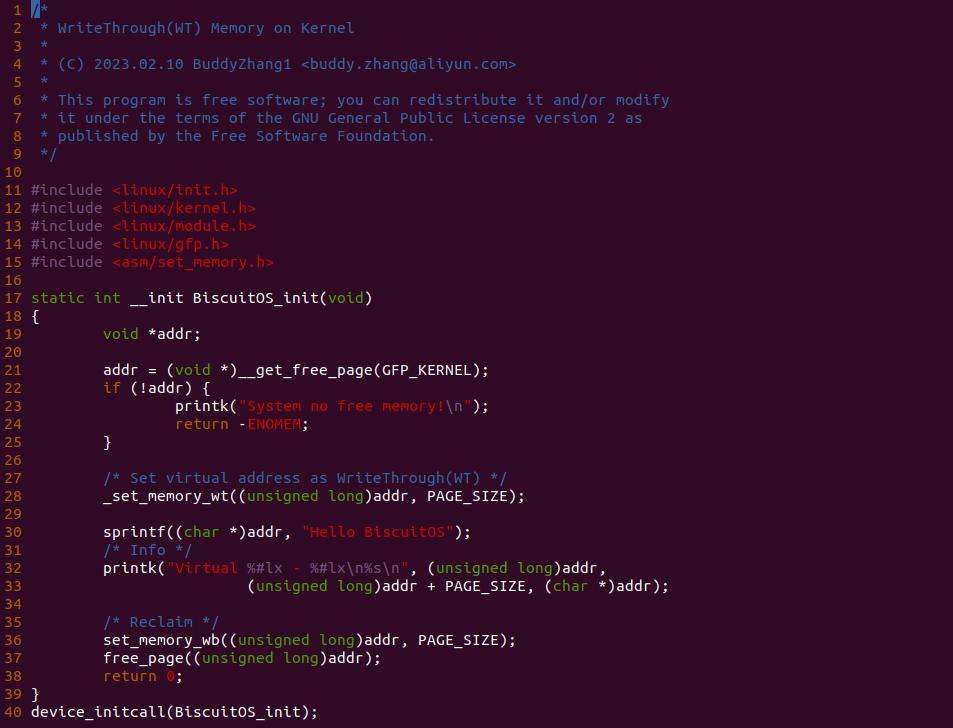

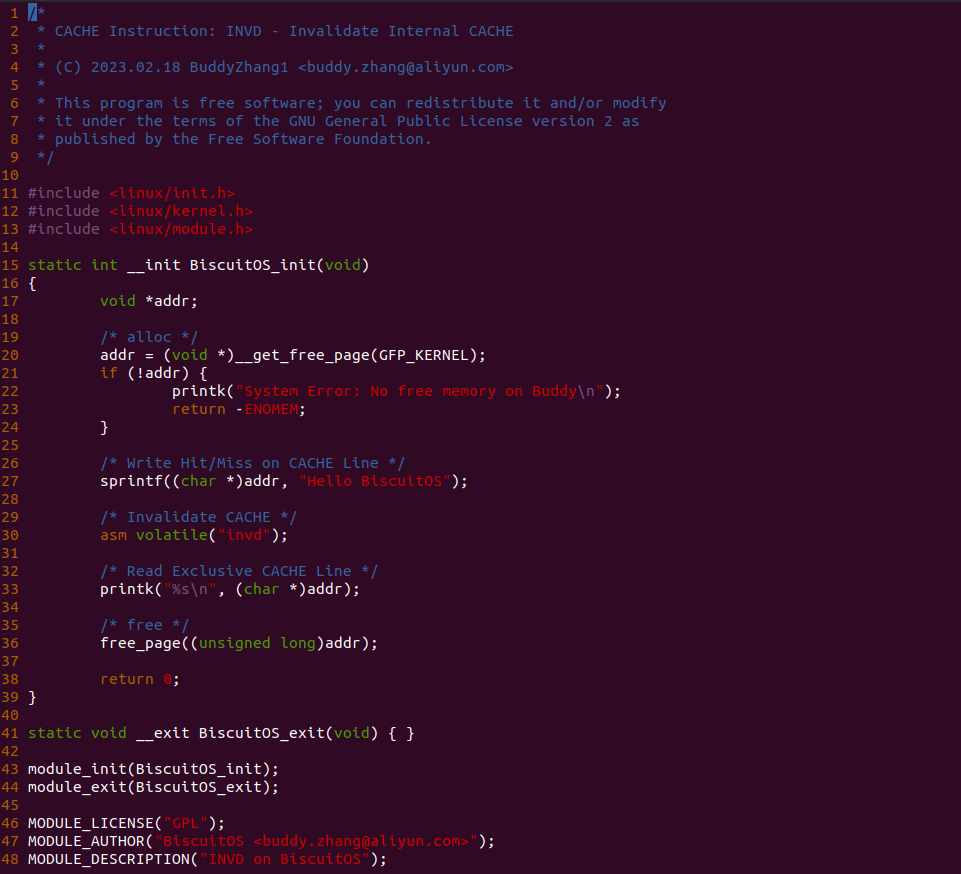

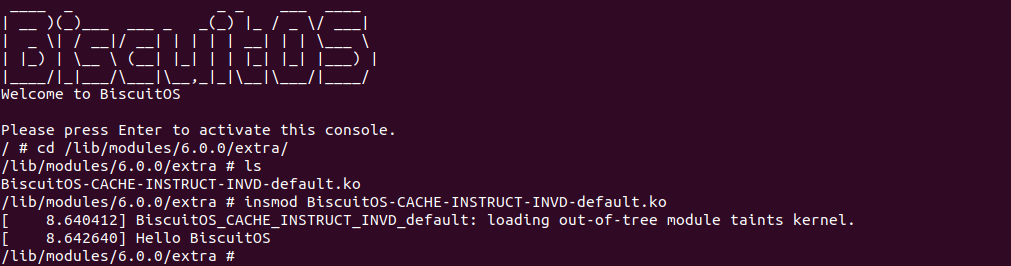

实践案例主要目的是在内核空间申请一段内存之后,将对应的虚拟地址以 WT 的方式映射到物理内存,并进行访问。案例在 21-25 行通过 __get_free_page() 函数分配一个物理页并获得对应的虚拟地址,然后在 28 行调用 _set_memory_wt() 函数进行 WT 方式的映射,案例接着在 30-33 行对映射之后的虚拟地址进行访问。最后在 36-37 行回收设置,值得注意的是当将内核空间虚拟地址设置为非 WB 之后,在回收时要主动设置为 WB, 接下来在 BiscuitOS 上实践该案例:

BiscuitOS 系统启动过程中,可以看到 dmesg 打印字符串 “Hello BiscuitOS”, 以及相应的虚拟地址,符合预期.

Write-Back (WB)

Write Back (WB): 回写类型,该类型会缓存读写请求。当 Read CACHE Hit 时直接从 CACHE Line 中读取数据,当 Read CACHE Miss 时先进行 CACHE Fill,然后再从 CACHE Line 中读取数据; 当 Write CACHE Hit 时,尽可能只更新 CACHE Line 的数据, 当 Write CACHE Miss 时会 CACHE Fills,并尽可能只更新 CACHE Line 中的数据. 当 WB 类型时预测读是允许的,并且 Write Combining 也是允许的。WB 类型内存由于写请求尽可能在 CACHE Line 中进行,很大程度上缓解了总线拥堵的问题. 与 WT 类型不同的是当写请求时不是立即写入到内存,而是尽可能的只写如到 CACHE Line,直到 Write-Back 信号到来时才把缓存中已经修改的数据更新到内存。Write-Back 操作可能发生在 CACHE 已经满的请求下,需要新分配一个 CACHE Line,那么被淘汰的 CACHE Line 就会执行 Write-Back 操作. 另外 CACHE 一致性协议针对其他核对 M 状态的 CACHE Line 进行读时也会触发 Write-Back 操作. WB 可以提供最好的性能,但其要求采用该类型的设备具有监听(snoop)内存访问,以此维护内存和 CACHE 的一致性. 那么接下来通过一组实践案例介绍内核和用户空间如何使用 WB 类型的内存:

用户空间虚拟地址映射 WB MMIO

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support BiscuitOS Hardware Emulate

[*] CACHE --->

[*] WriteBack(WB): Mapping WB MMIO on Userspace --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WB-MMIO-USERSPACE-default

# 部署源码

make download

# 在 BiscuitOS/Broiler 中实践

make broilerBiscuitOS-CACHE-WB-MMIO-USERSPACE-default Source Code on Gitee

实践案例由两个部分组成,main.c 为内核模块部分,负责映射 MMIO 的底层逻辑。模块首先在 22-26 行定义了 MMIO 区域的信息,然后在 56-57 行通过调用 request_resource() 函数将 MMIO 区域添加到系统物理地址空间树里。模块通过注册一个 MISC 驱动,向用户空间提供 “/dev/BiscuitOS-MMIO” 接口,用户空间程序打开该接口,并调用 mmap() 映射 MMIO 时会调用到模块的 BiscuitOS_mmap() 函数,该函数首先在 32 行将虚拟地址对应的页表属性里的 _PAGE_PAT、_PAGE_PCD 和 _PAGE_PWT 标志清除,然后在 34 行调用 cachemode2protval() 函数,将 WB 属性赋值到 vm_page_prot 成员,接下来调用 io_remap_pfn_range() 函数进行虚拟地址到 MMIO 的映射工作。映射完毕之后用户空间虚拟地址就可以以 WB 方式访问 MMIO.

实践案例的另外一部分位于 app.c 内,其为用户空间程序,用于映射虚拟地址到 MMIO 并进行访问. 程序首先在 29 行通过 open() 函数打开 “/dev/BiscuitOS-MMIO” 节点,然后在 36-46 通过 mmap() 函数将进程地址空间的虚拟地址映射到 MMIO,接下来在 49-51 行对映射之后对 MMIO 进行访问,最后在 56-57 行释放相应的资源. 源码分析完毕之后在 BiscuitOS 进行实践,由于 MMIO 绑定在具体的硬件上,此时可以使用 Broiler 进行模块,直接使用 “make broiler” 命令进行实践:

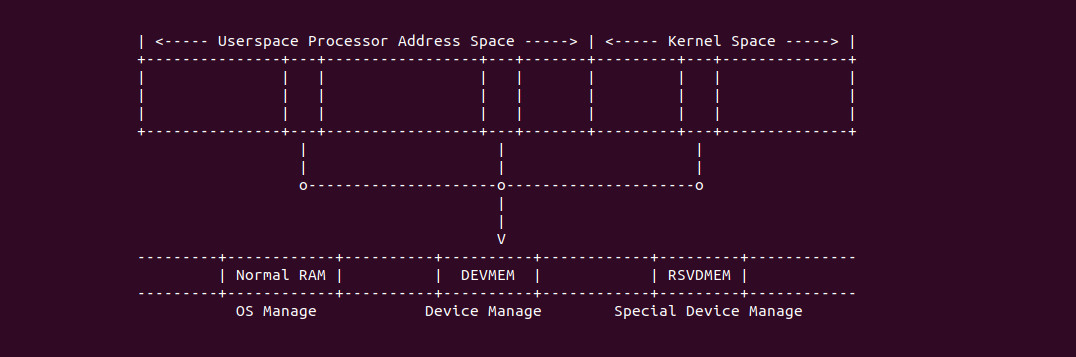

BiscuitOS Broiler 运行之后加载 BiscuitOS-CACHE-WB-MMIO-USERSPACE-default.ko, 接着运行用户态程序 APP,这里以后台方式运行,因此查看其他有用信息,运行之后可以看到正常访问 MMIO。接下来查看 /sys/kernel/debug/x86/pat_memtype_list 节点,可以看到 [0xF0000000, 0xF0001000) 区域映射为 uncached-minus,最后查看 /proc/iomem 系统物理地址空间,可以看到 Broiler MMIO 对应的区域正好是 [0xF0000000, 0xF0001000)。实践结果不符合预期,具体原因见. 那么接下来对普通物理内存映射为 WB 场景进行实践:

用户空间虚拟内存映射 WB 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] WriteBack(WB): Mapping WB Memory on Userspace --->

-*- CACHE User-Page for Kernel Stub (Basic) --->

# 进入源码目录

# Userspace: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WB-MEM-USERSPACE-default/

# Kernel: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default/

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WB-MEM-USERSPACE-default/

# 部署源码

make prepare

make download

# 在 BiscuitOS 中实践

make buildBiscuitOS-CACHE-WB-MEM-USERSPACE-default Source Code on Gitee

源码分成两部分,其中一部分为用户空间程序(上图所示), 用户空间代码的主要功能是映射一段虚拟内存,并将其缓存类型设置为 WB. 函数首先在 34 行将 pcm 变量设置为 _PAGE_CACHE_MODE_WB, 然后在 39 行打开 “/dev/BiscuitOS-CACHE” 节点,并基于该节点映射长度为 PAGE_SIZE 的虚拟内存,此时在函数 50 行将 pcm 传入到 mmap() 函数,映射完毕后函数在 58-59 行使用 WB 的内存,使用完毕在 61-62 行解除映射并关闭文件。

BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default Source Code on Gitee

源码的另外一部分位于内核空间,其主要功能是进行实际的映射任务。模块通过一个 MISC 驱动进行实现,其提供了 mmap 接口 BiscuitOS_mmap(), 当用户空间基于 “/dev/BiscuitOS-CACHE” 节点调用 mmap() 函数时,BiscuitOS_mmap() 函数就会别调用。模块首先在 60 行调用 mtrr_add() 函数将 [MTRR_MEM_BASE, MTRR_MEM_SIZE + MTRR_MEM_BASE) 区域的 MTRR 设置为 WB. 模块接着在 33 行在用户空间调用 mmap() 函数时从 vma 的 vm_pgoff 成员中获得 PAGE CACHE MODE 信息,接着在 36 行将 vma_page_prot 成员中移除 _PAGE_PCD、_PAGE_PWT 和 _PAGE_PAT 属性,并在 39 行调用 cachemode2protval() 函数将 PAGE CACHE MODE 转换成对应的页表属性,并重新存储到 vma 的 vm_page_prot, 以此作为用于空间设置的 memory type 页表属性,最后模块在 41 行调用 remap_pfn_range() 函数为虚拟内存建立页表并映射到 MTRR_MEM_BASE 对应的物理内存上. 接下来在 BiscuitOS 上实践该案例:

BiscuitOS 在次运行之后,运行应用程序,可以看到系统没有再提示修改信息,那么用户进程已经成功将一段物理内存的 memory type 设置为 WB. 实践符合预期,那么接下来实践内核空间虚拟地址映射 WB 物理内存:

内核空间虚拟内存映射 WB 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] WriteBack(WB): Mapping WB Memory on Kernel --->

# 进入源码目录

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WB-MEM-KERNEL-default/

# 部署源码

make download

# 在 BiscuitOS 中实践

make build

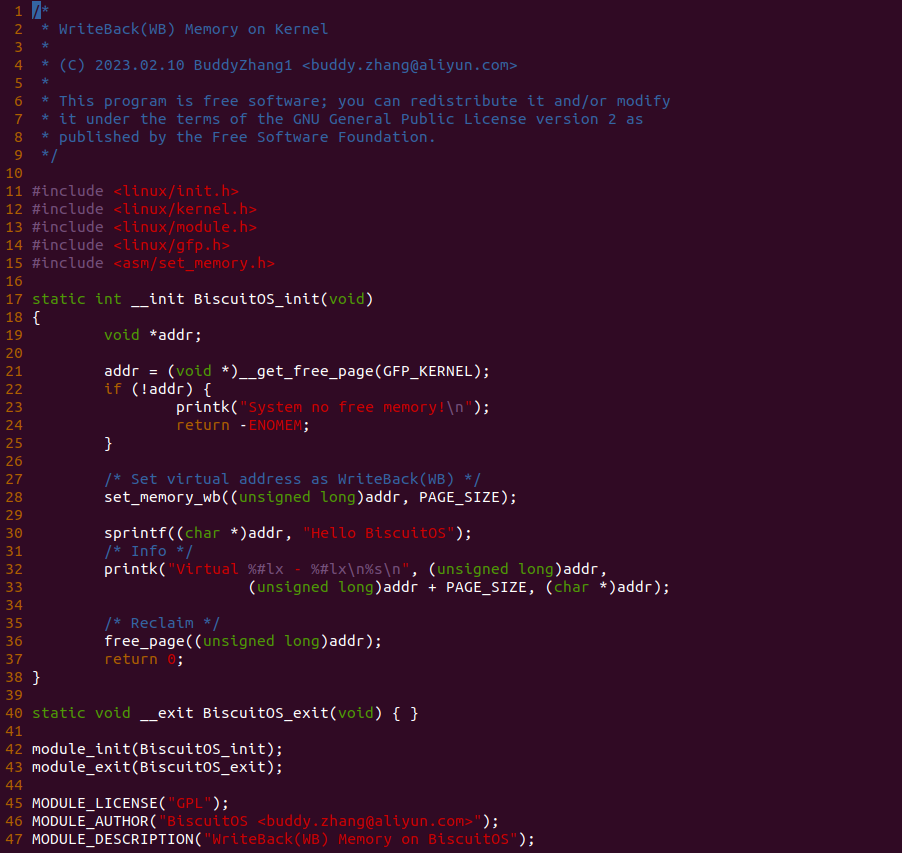

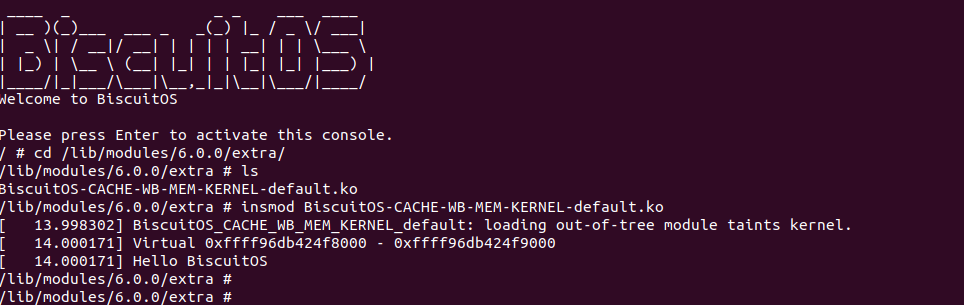

实践案例主要目的是在内核空间申请一段内存之后,将对应的虚拟地址以 WB 的方式映射到物理内存,并进行访问。案例在 21-25 行通过 __get_free_page() 函数分配一个物理页并获得对应的虚拟地址,然后在 28 行调用 set_memory_wb() 函数进行 WB 方式的映射,案例接着在 30-33 行对映射之后的虚拟地址进行访问。最后在 36-37 行回收设置, 接下来在 BiscuitOS 上实践该案例:

BiscuitOS 运行之后,加载 BiscuitOS-CACHE-WB-MEM-KERNEL-default.ko 模块,可以看到系统可以使用 WB 的虚拟内存,并打印字符串 “Hello BiscuitOS”, 符合预期.

Write-Protected (WP)

Write Protected (WP): 写保护类型,该类型读请求从 CACHE Line 中获得数据,当 Read CACHE Miss 时触发 CACHE Fill. 但写请求会广播到总线,让其他 CPU 缓存副本的 CACHE Line 在总线上的数据全部无效,这个场景优点类似于所有 CPU 对一个 Shared 状态的 CACHE Line 进行写操作时,每个 CPU 都有将 CACHE Line 设置为 Modify 的可能,但此时采用 WP 的 CPU 会让其他 CPU 的 Modify 都无效,只有自己的 CACHE Line 可以设置为 Modify。另外 WP 时分支读是允许的, 那么接下来通过一组实践案例介绍内核和用户空间如何使用 WP 类型的内存:

用户空间虚拟内存映射 WP 物理内存

cd BiscuitOS

make menuconfig

[*] Package --->

[*] DIY BiscuitOS/Broiler Hardware --->

[*] Support Host CPU Feature Passthrough

[*] CACHE --->

[*] WriteProtected(WP): Mapping WP Memory on Userspace --->

-*- CACHE User-Page for Kernel Stub (Basic) --->

# 进入源码目录

# Userspace: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WP-MEM-USERSPACE-default/

# Kernel: BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default/

cd BiscuitOS/output/linux-X.Y.Z-ARCH/package/BiscuitOS-CACHE-WP-MEM-USERSPACE-default/

# 部署源码

make prepare

make download

# 在 BiscuitOS 中实践

make buildBiscuitOS-CACHE-WP-MEM-USERSPACE-default Source Code on Gitee

源码分成两部分,其中一部分为用户空间程序(上图所示), 用户空间代码的主要功能是映射一段虚拟内存,并将其缓存类型设置为 WP. 函数首先在 34 行将 pcm 变量设置为 _PAGE_CACHE_MODE_WP, 然后在 39 行打开 “/dev/BiscuitOS-CACHE” 节点,并基于该节点映射长度为 PAGE_SIZE 的虚拟内存,此时在函数 50 行将 pcm 传入到 mmap() 函数,映射完毕后函数在 58-59 行使用 WP 的内存,使用完毕在 61-62 行解除映射并关闭文件。

BiscuitOS-CACHE-USER-PAGE-Kernel-Stub-default Source Code on Gitee

源码的另外一部分位于内核空间,其主要功能是进行实际的映射任务。模块通过一个 MISC 驱动进行实现,其提供了 mmap 接口 BiscuitOS_mmap(), 当用户空间基于 “/dev/BiscuitOS-CACHE” 节点调用 mmap() 函数时,BiscuitOS_mmap() 函数就会别调用。模块首先在 60 行调用 mtrr_add() 函数将 [MTRR_MEM_BASE, MTRR_MEM_SIZE + MTRR_MEM_BASE) 区域的 MTRR 设置为 WB. 模块接着在 33 行在用户空间调用 mmap() 函数时从 vma 的 vm_pgoff 成员中获得 PAGE CACHE MODE 信息,接着在 36 行将 vma_page_prot 成员中移除 _PAGE_PCD、_PAGE_PWT 和 _PAGE_PAT 属性,并在 39 行调用 cachemode2protval() 函数将 PAGE CACHE MODE 转换成对应的页表属性,并重新存储到 vma 的 vm_page_prot, 以此作为用于空间设置的 memory type 页表属性,最后模块在 41 行调用 remap_pfn_range() 函数为虚拟内存建立页表并映射到 MTRR_MEM_BASE 对应的物理内存上. 接下来在 BiscuitOS 上实践该案例:

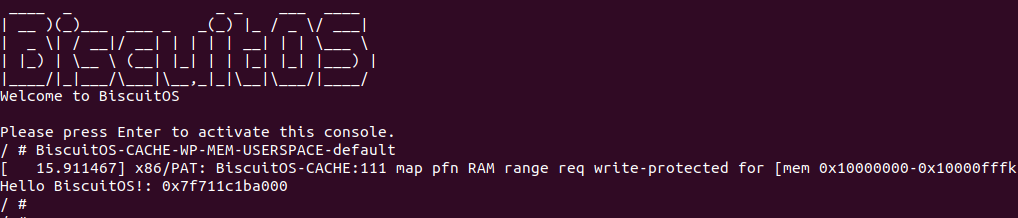

BiscuitOS 运行之后, 执行应用程序 BiscuitOS-CACHE-WP-MEM-USERSPACE-default,此时系统提示了程序预期将 [0x10000000-0x10000fff] 为 write-protected,但是系统还是将对应的 memory type 设置为 write-back, 这个与预期不符合. 查看内核模块源码的 3 行提示需要将 [0x10000000, 0x10200000) 进行预留,那么在 CMDLINE(CMDLINE 位于 RunBiscuitOS.sh 文件中) 中添加预留字段后再次实践:

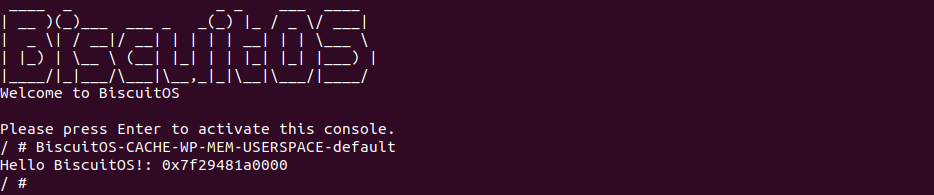

BiscuitOS 在次运行之后,运行应用程序,可以看到系统没有再提示修改信息,那么用户进程已经成功将一段物理内存的 memory type 设置为 WP. 实践符合预期,那么接下来实践内核空间虚拟地址映射 WP 物理内存:

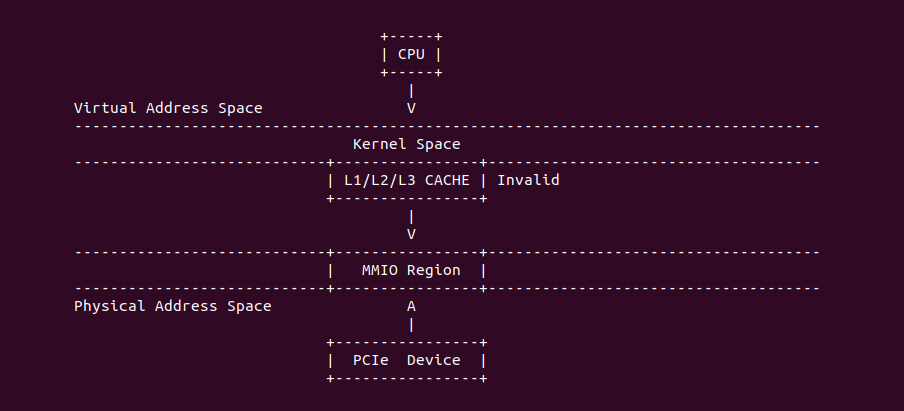

UC/UC-/WC/WT/WB/WP 横向对比

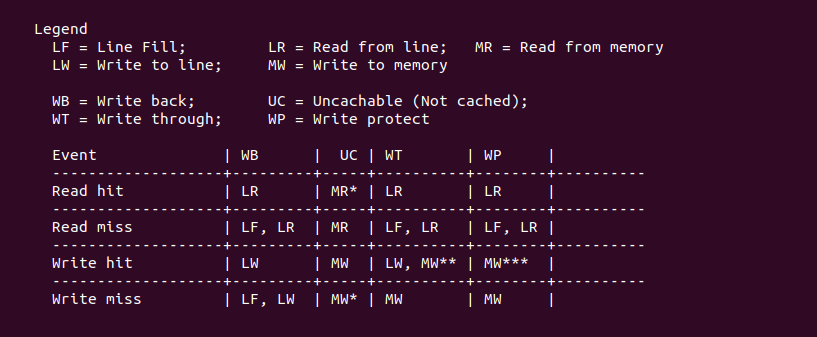

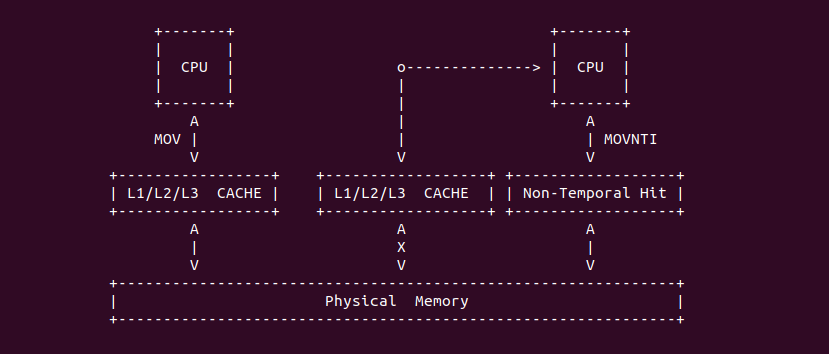

本节对不同的 memory type 进行横向对比,在上表中对于 Read/Write 请求是否缓存,UC、UC-、WC 全部不缓存,WT、WB 全部缓存,WP 只对读请求进行缓存; 只有 WB 支持 Writeback 不一定访问内存,其余类型 Write 都会访问内存; UC、UC- 不支持分支读预测功能,其余都支持分支读预测功能;

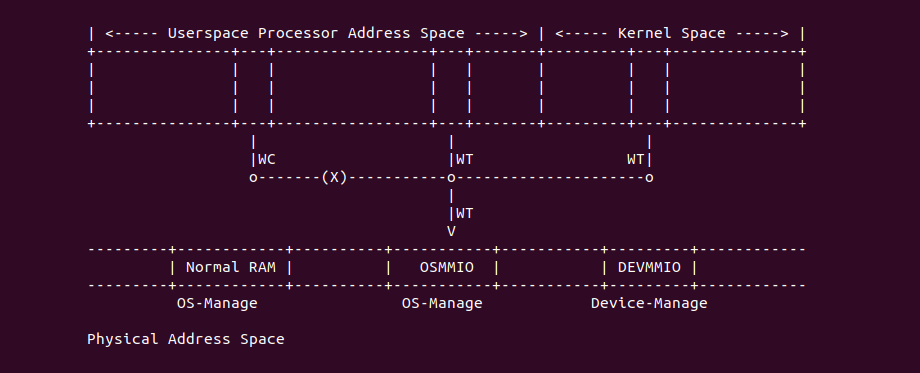

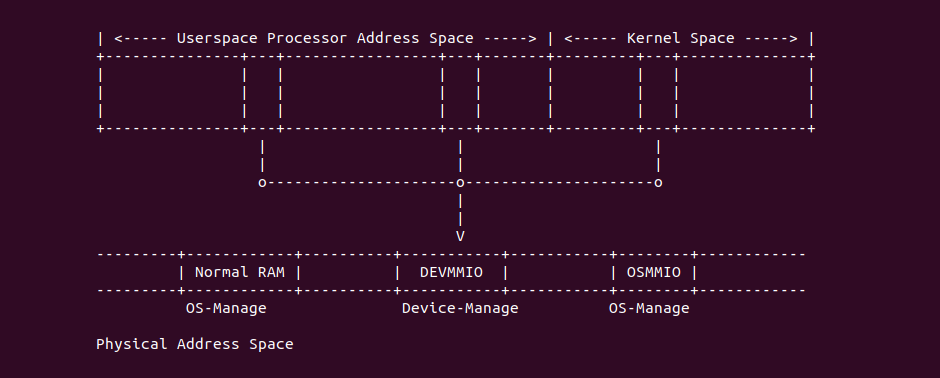

上图展示的是当 Read/Write Hit/Miss 时不同 memory type 的动作: WB Read/Write hit 仅仅访问 CACHE Line,而 Read/Write Miss 时都会先触发 CACHE Fill,然后在访问缓存; UC Read/Write 无视 Hit/Miss,直接访问内存; WT Read Hit 只访问 CACHE Line,Write Hit 是不仅访问 CACHE Line,还会更新内存,Read Miss 是先触发 CACHE Fill 再访问 CACHE Line,Write Miss 时仅仅访问内存; WP Read Hit 直接访问 CACHE Line,Read Miss 触发 CACHE Fille 再访问 CACHE Line,Write Hit 时直接访问内存并让其他 CACHE Line 副本 Invalid,Write Miss 直接访问内存.

Memory Type 适用场景

不同的 Memory Type 适用与不同的场景,本节用于分析系统推荐的 memory type 场景, 总结如下:

- 普通物理内存(不包括 Frame Buffer) memory type 均采用 WB.

- 具有 IO Agent 且能维护 CACHE 一致性的外设,其能 DMA 的物理内存 memory type 采用 WB.

- MMIO 采用 UC/UC-

- Dual-ported Memory 可以采用 UC/UC-/WT/WC

- Frame Buffer 可以采用 UC/UC-/WT/WC. 其特点就是大量的写而很少的读操作.

Uncacahed Memory 编程

Intel® CACHE Coherency Protocol

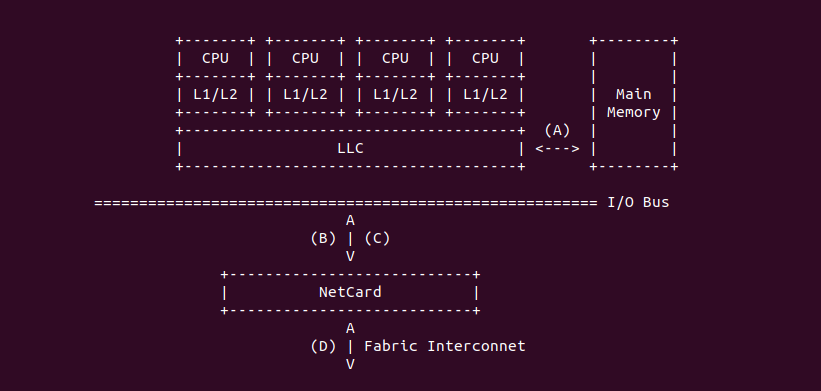

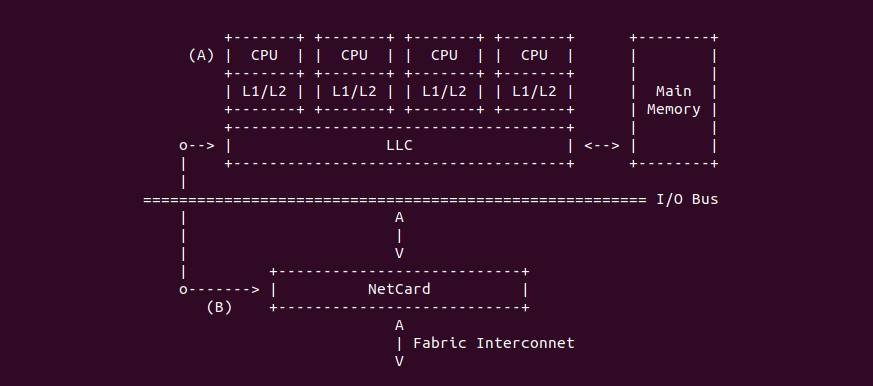

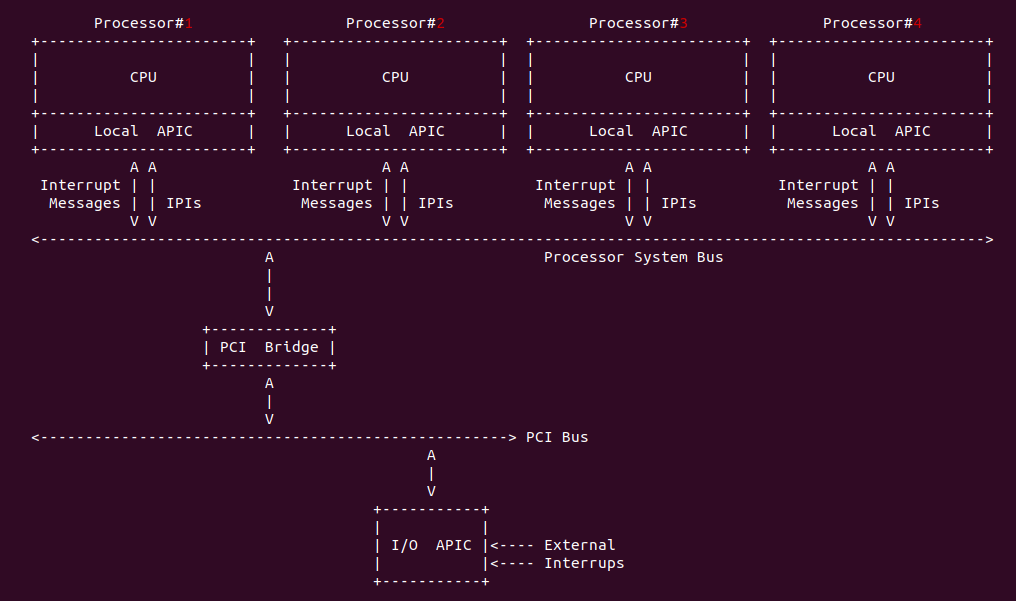

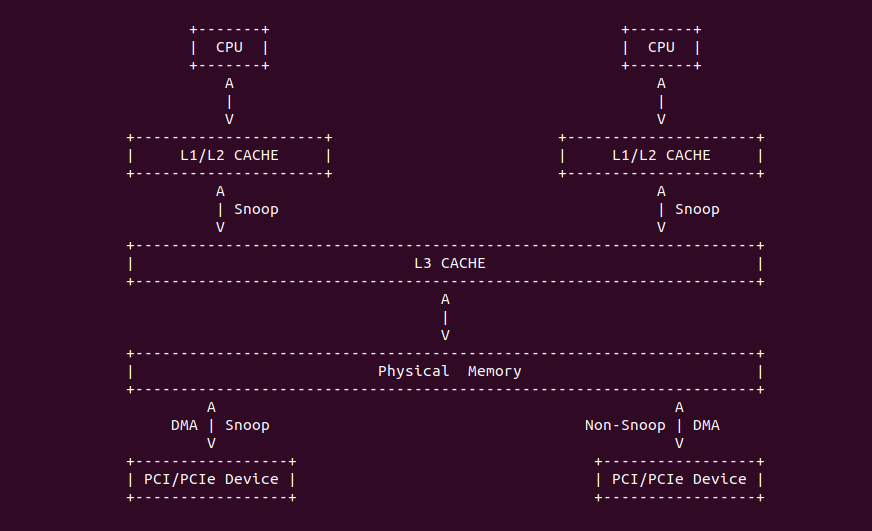

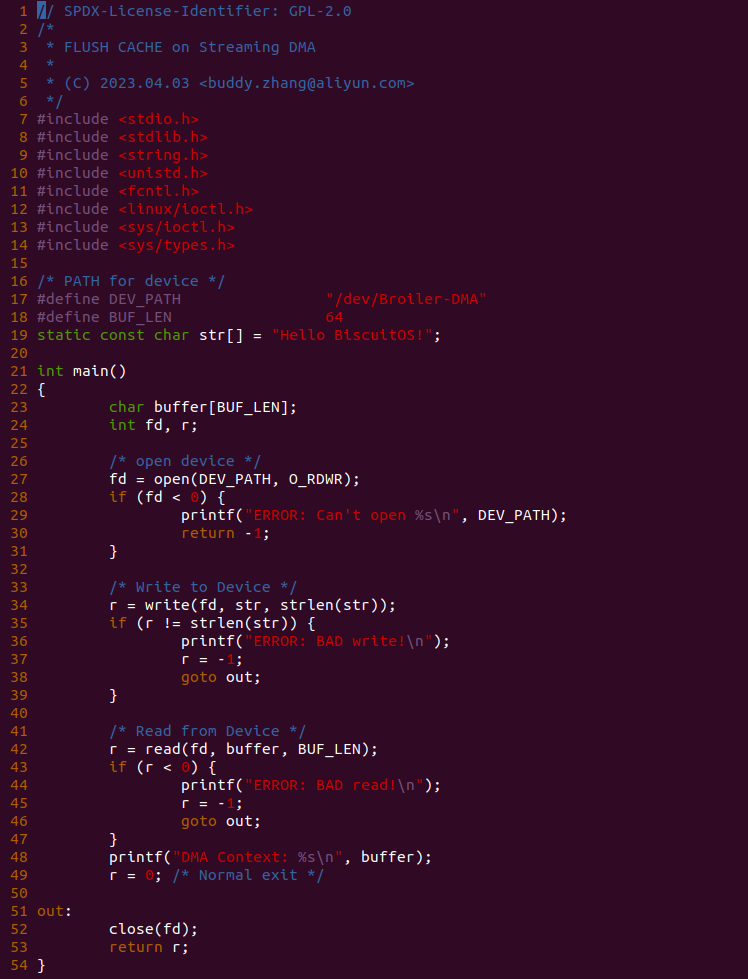

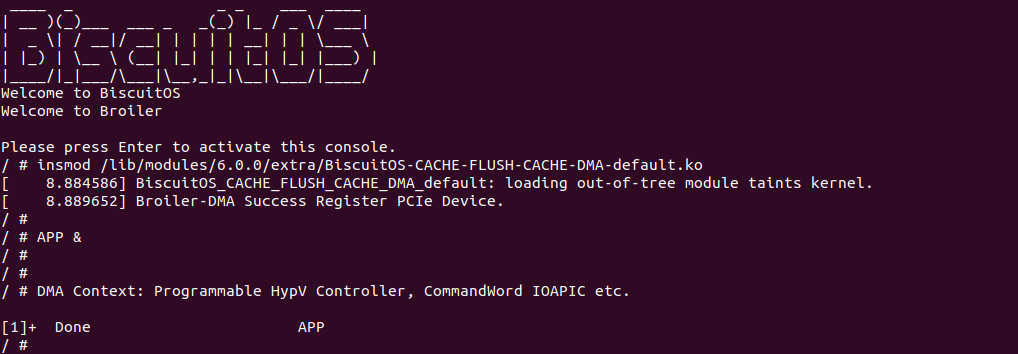

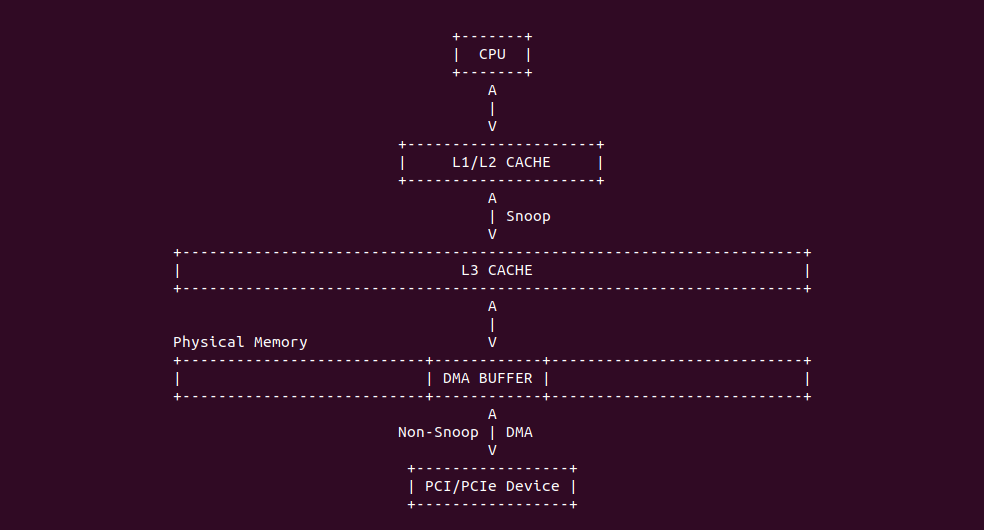

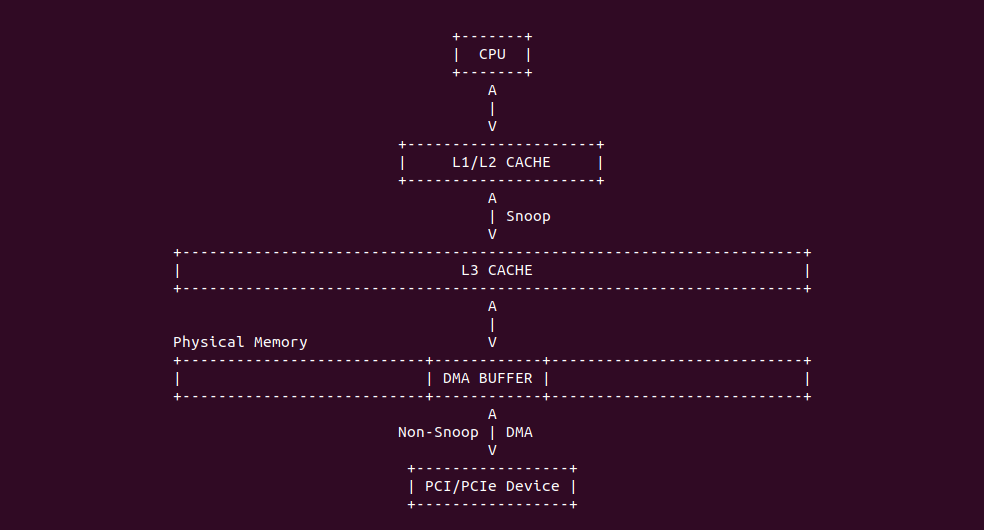

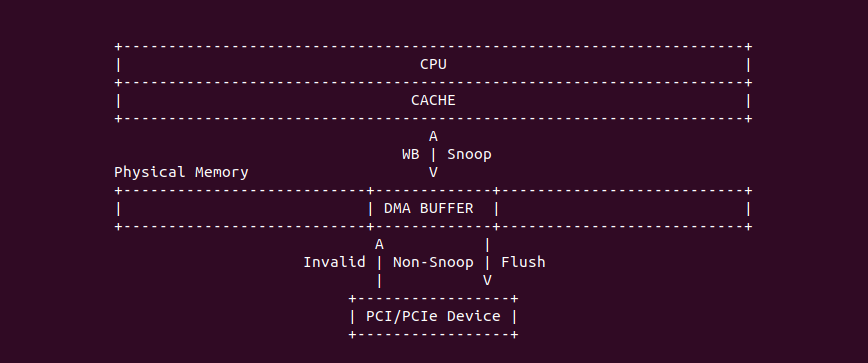

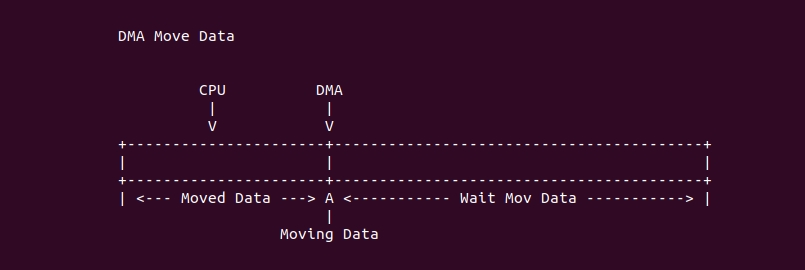

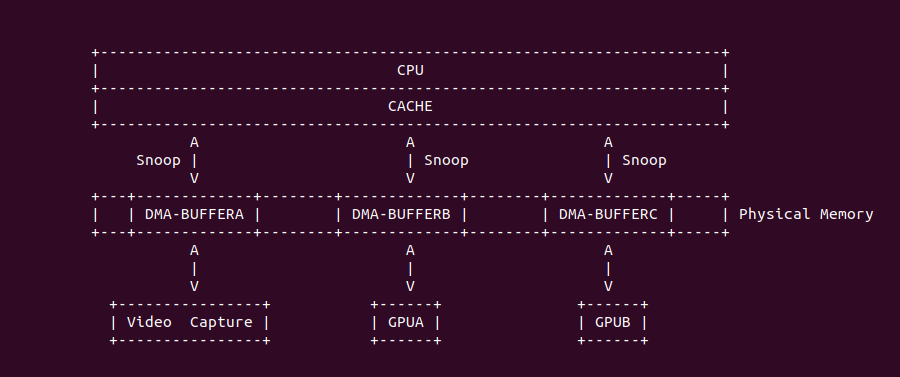

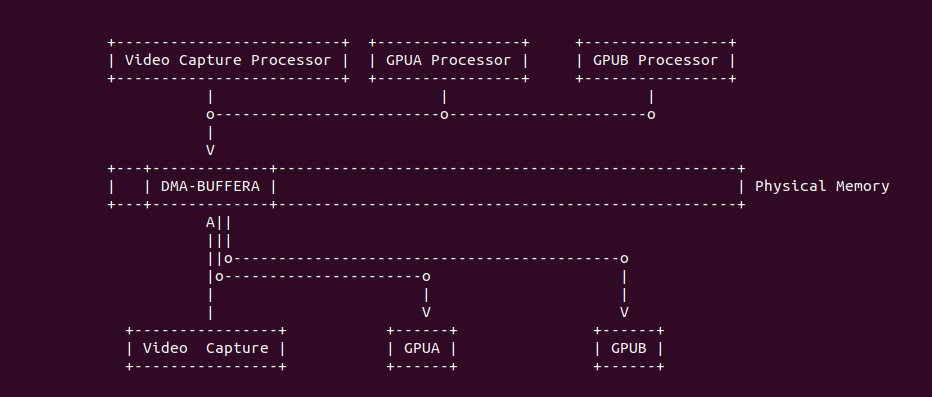

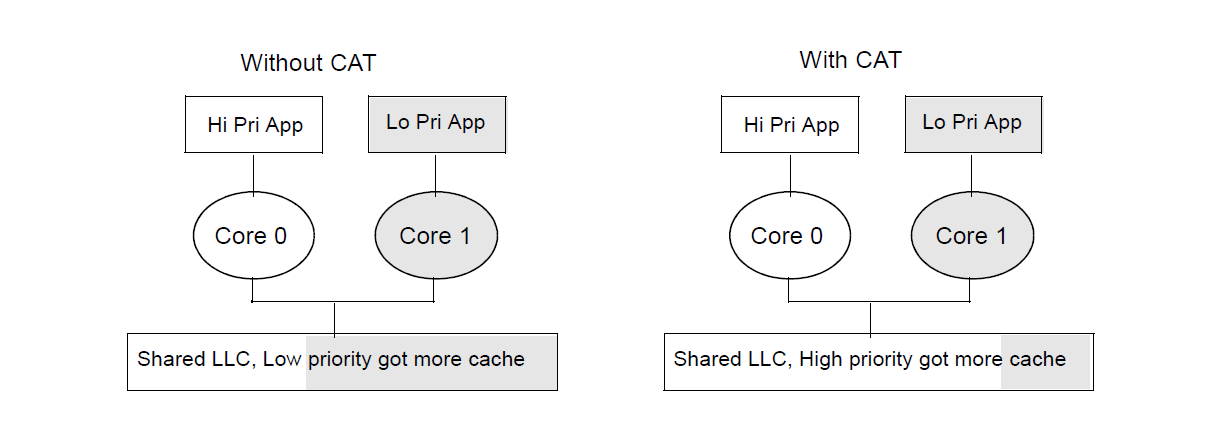

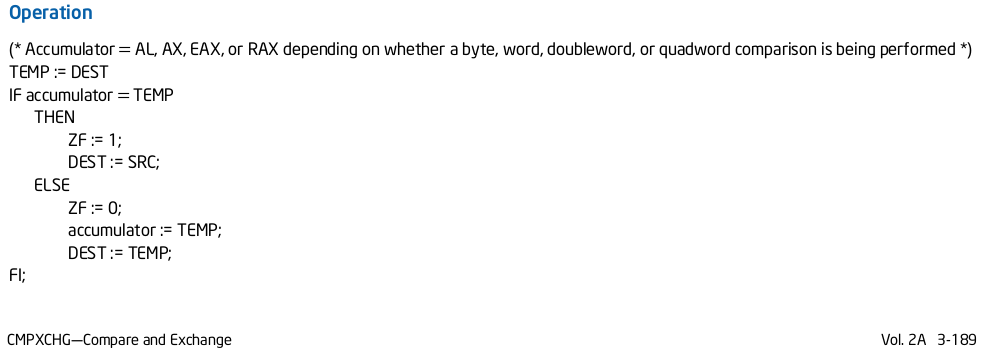

在 Intel 64 和 IA-32 架构里,L1 Data CACHE、L2 和 L3 Unified CACHE 支持 MESI(Modify、Exclusive、Shared、Invalid) CACHE Line 状态,以此维护 CACHE 一致性. L1 Data CACHE、L2 和 L3 Unified CACHE 的每个 CACHE Line 具有两个 MESI 状态,每个 CACHE Line 可以标记为上图中的四种状态。同理在 X86 架构下 MESI 状态对软件依旧透明. 在 L1 Instruction CACHE 因为是只读的,因此 CACHE Line 只支持了 SI(Shared、Invalid) 状态。在多核架构里,IA-32 和 Intel 64 架构有能力监听(Snoop) 其他处理器访问内存和各自内部 CACHE. 处理器利用监听能力,保证了其内部的 CACHE 与内存和其他处理其内部 CACHE 的一致性.

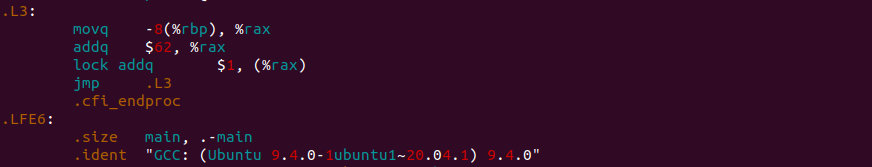

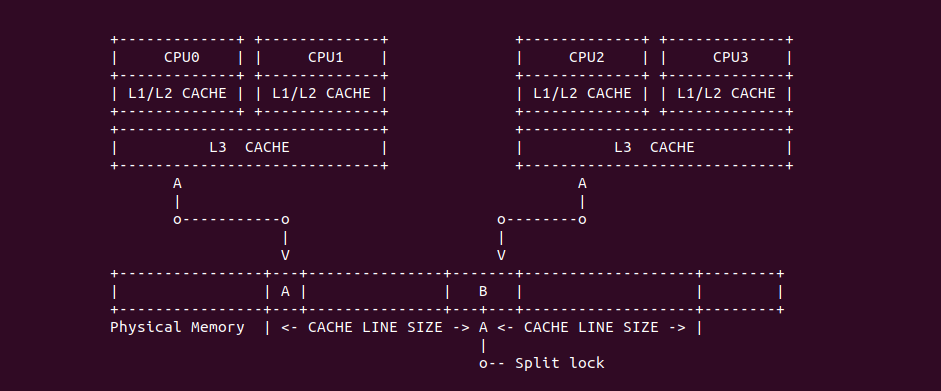

Intel P6 之后的架构,原子操作不再发出任何的 LOCK# 信号,一切都由 CACHE 一致性协议完成。上图是典型的多核架构下的 CACHE 缓存结构,L1/L2 CACHE 为 CORE 私有 CACHE,L3 则由同一个 Socket 上的多个 Core 共享的,那么就存在 CACHE Coherent 问题,通过之前的文章可以知道,硬件通过 MESI 机制保证 CACHE Coherent。对于 X86 则使用了增强版 MESIF, F 代表 Forwarding. 引入 F 的原因是对于一个处于 Shared 状态的 CACHE Line,在多个 Core 中都有一份备份,那么有一个新的 Core 需要读取该 CACHE Line 内存中数据,发现多个 Core 都有副本,那么此时由哪个 Core 提供副本呢? 如果每个 Core 都应答新 Core 会造成冗余数据,所以将 S 状态下的某个 Core 的 CACHE Line 标记为 F,并且只由 F 负责应答,通常最后持有备份的为 F.

Intel® MTRRs Technology

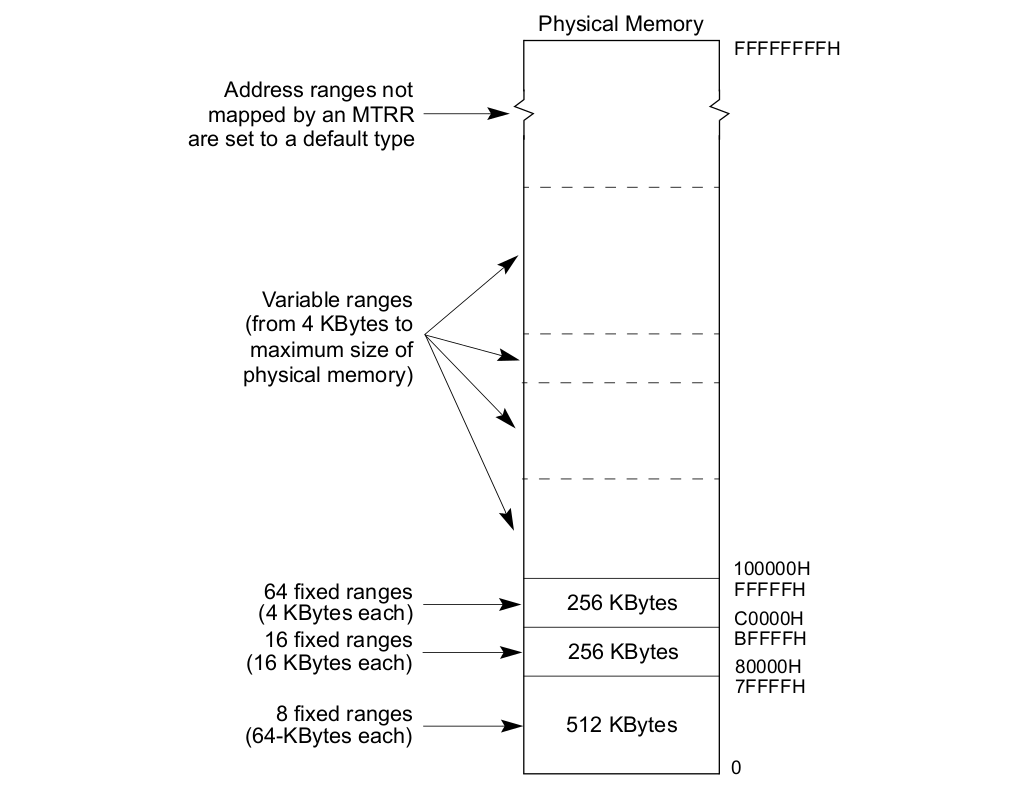

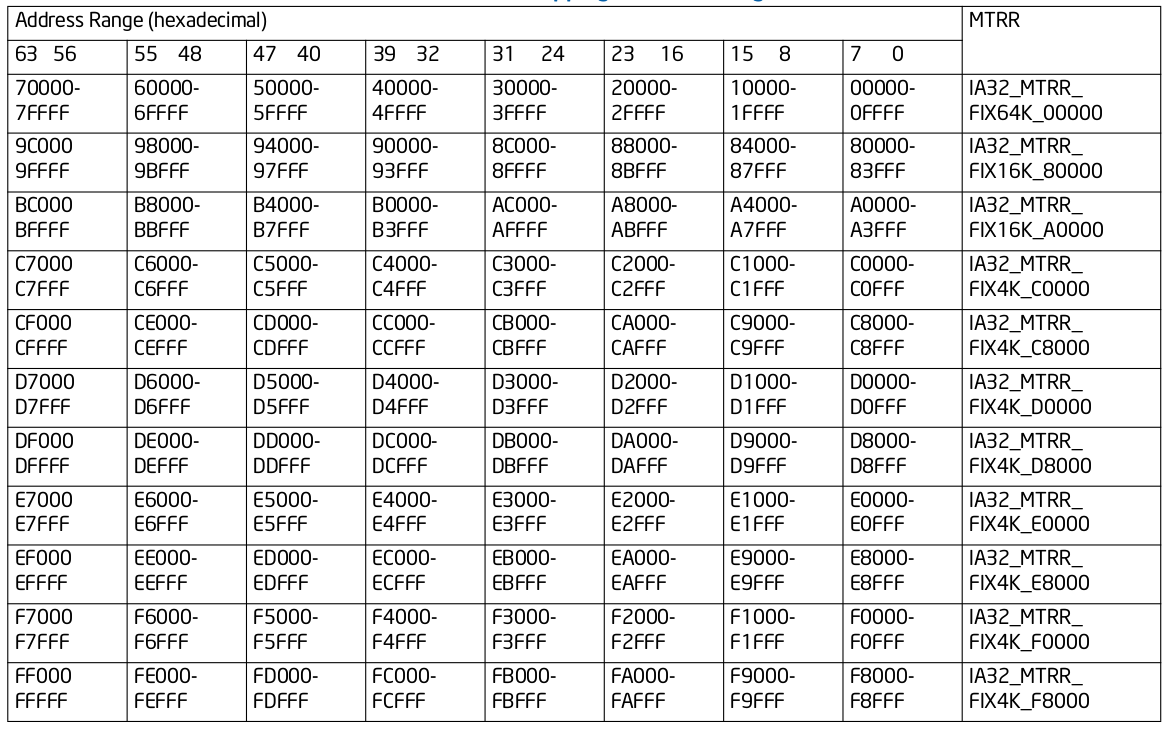

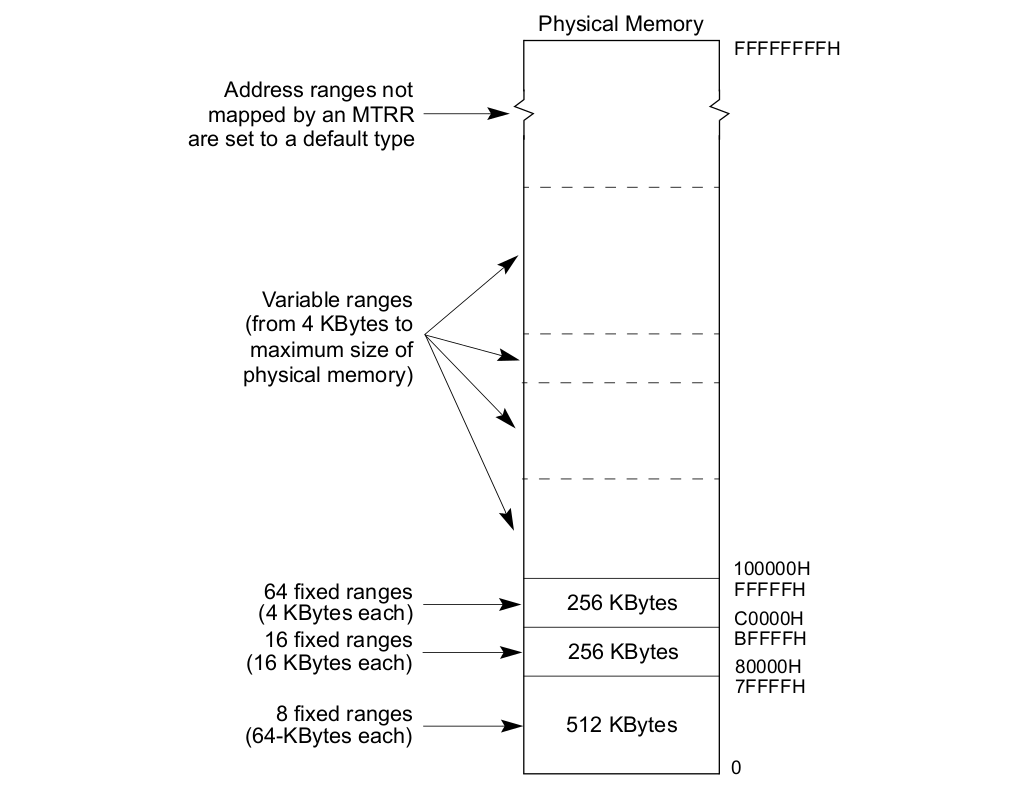

MTRRs The memory type range registers: Intel® 在 P6 之后向系统提供了 MTRRs 技术,MTRRs 运行为 RAM、ROM、Frame-Buffer 内存和 MMIO 对应的物理区域设置不同的 Memory Type. MTRRs 机制通过提供一系列的 MSR 寄存器用于指定物理区域范围和 Memory Type,上表描述了 MTRR 映射物理区域的范围,可以分为三类:

- 固定物理区域 MTRRs(Fixed MTRRs), MTRRs 提供了多个 MSR 寄存器,这些寄存器针对固定的物理区域可以设置指定的 Memory Type

- 可变物理区域 MTRRs(Variable MTRRs), MTRRs 提供了多对 MSR 寄存器,每一对寄存器可以设置物理区域和 Memory Type

- 默认 MTRR(Default MTRRs), MTRRs 提供了一个 MSR 用于设置默认的 Memory Type,针对不在前两种覆盖范围的物理区域,均采用默认的 Memory Type.

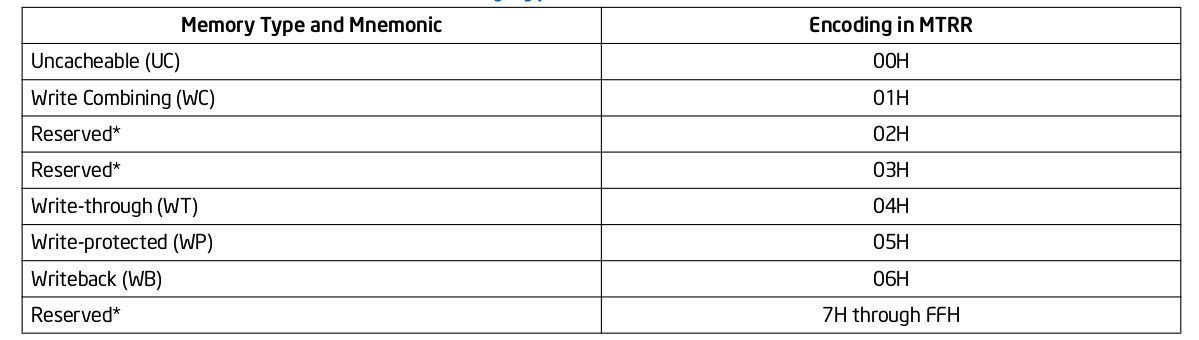

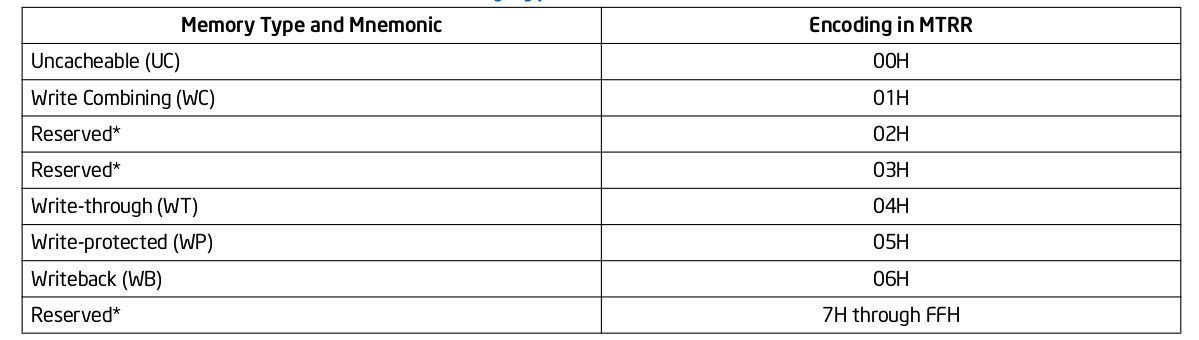

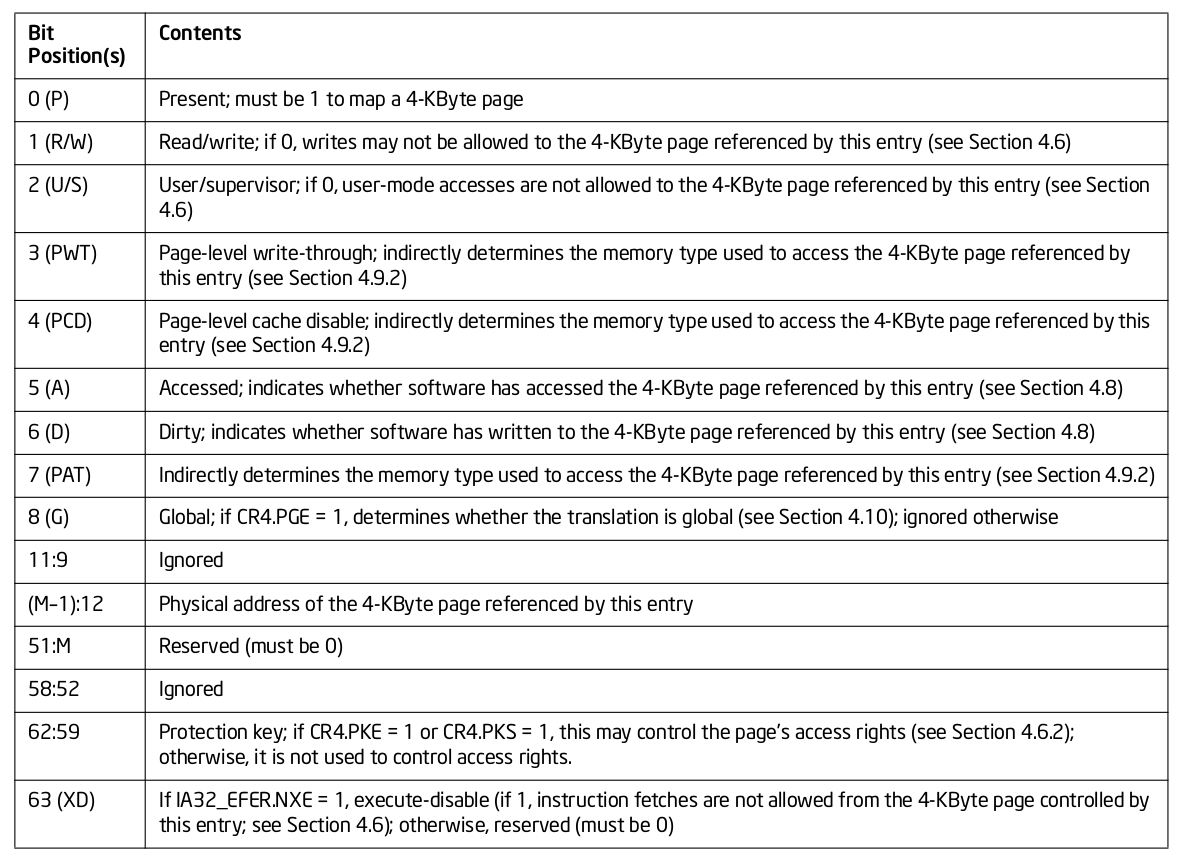

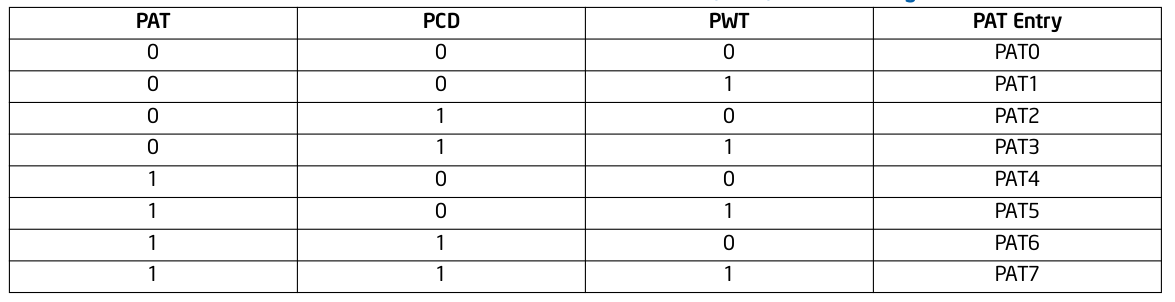

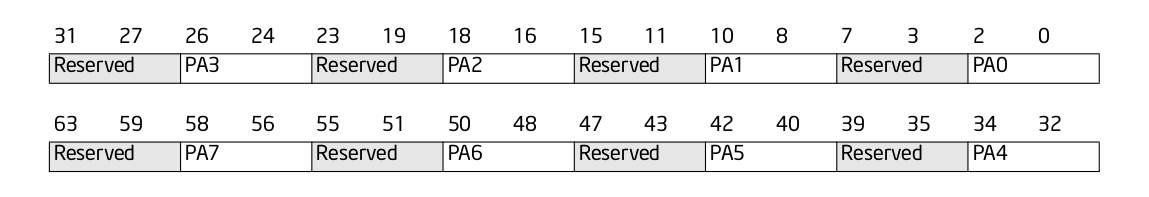

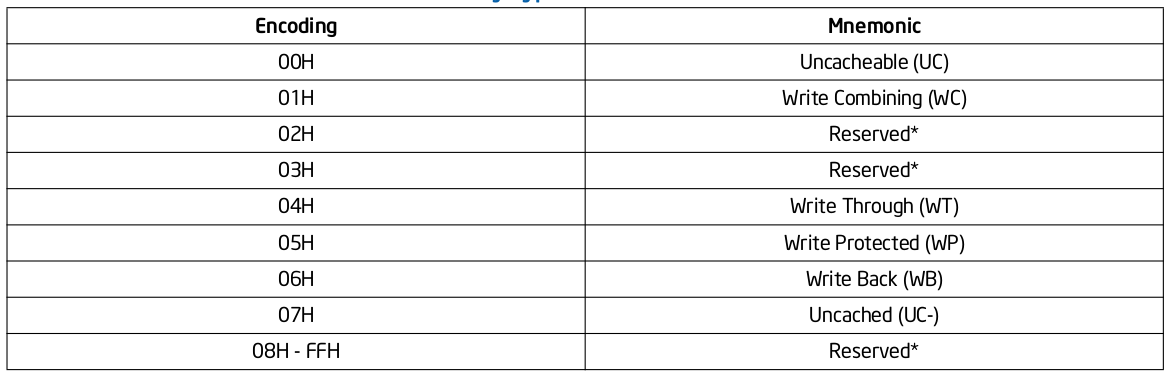

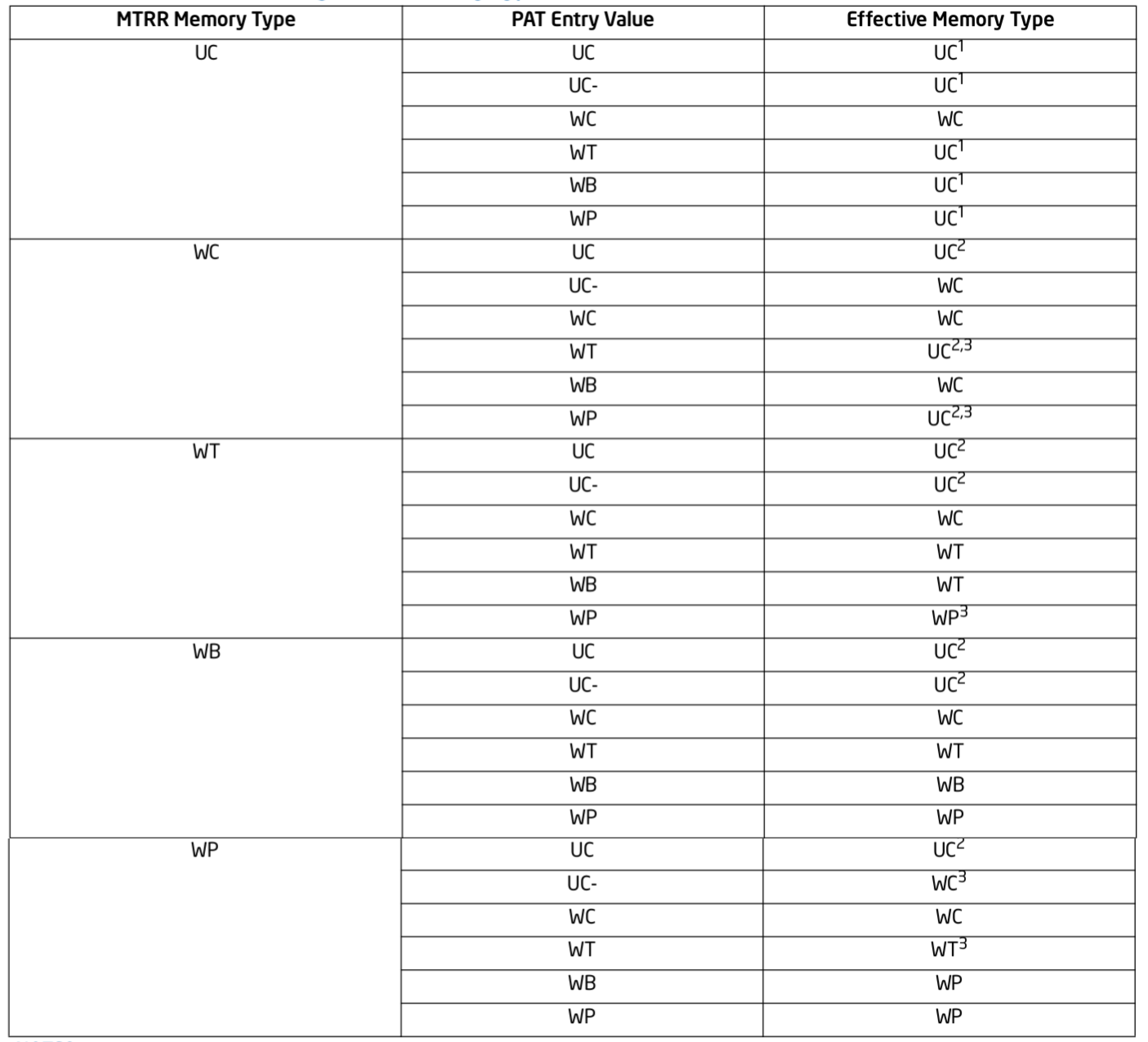

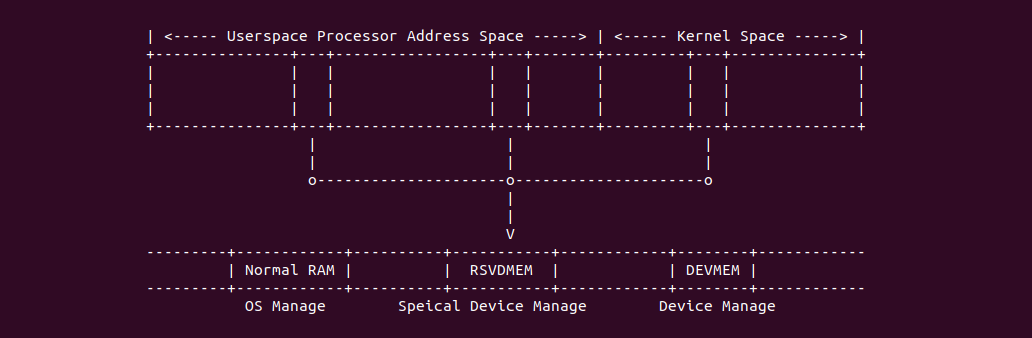

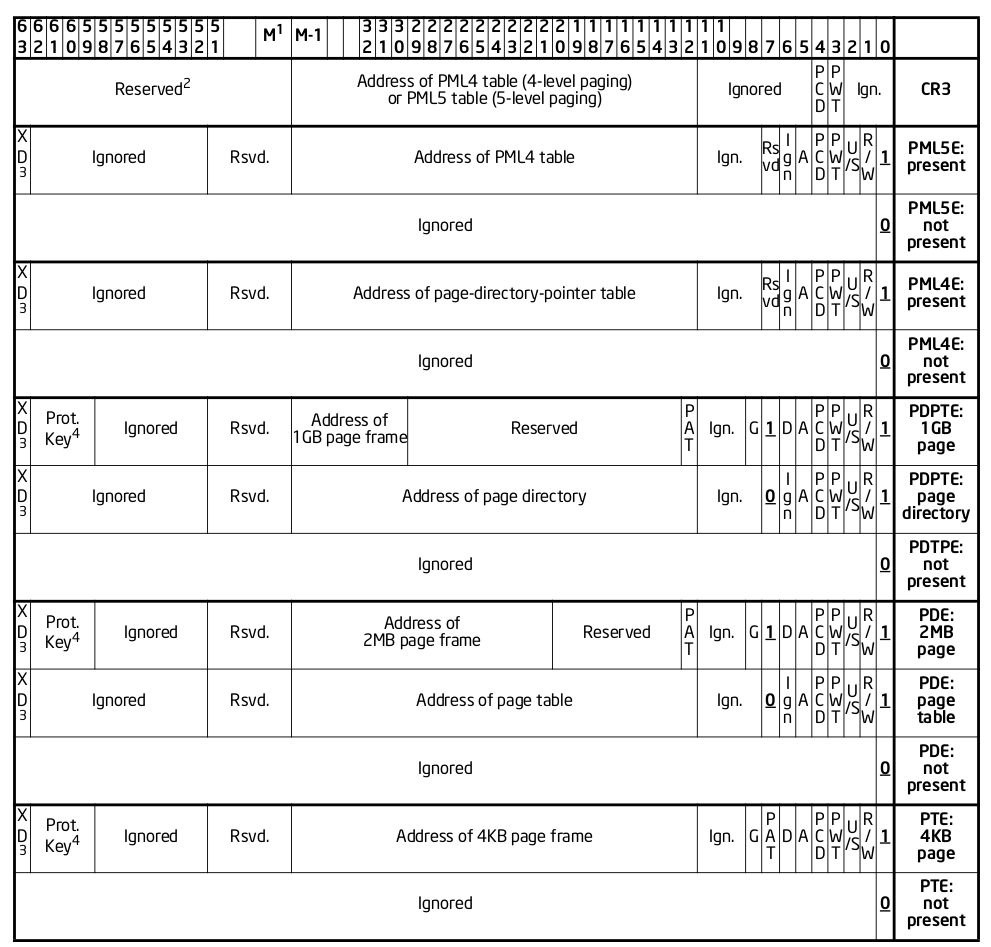

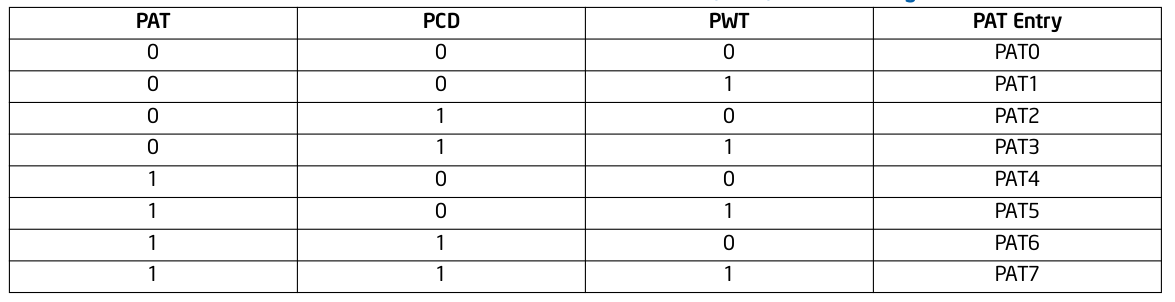

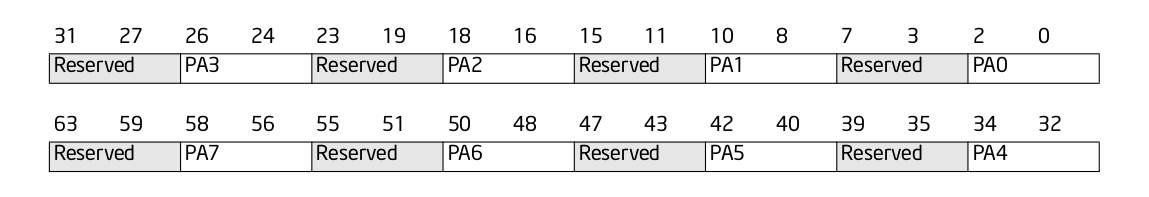

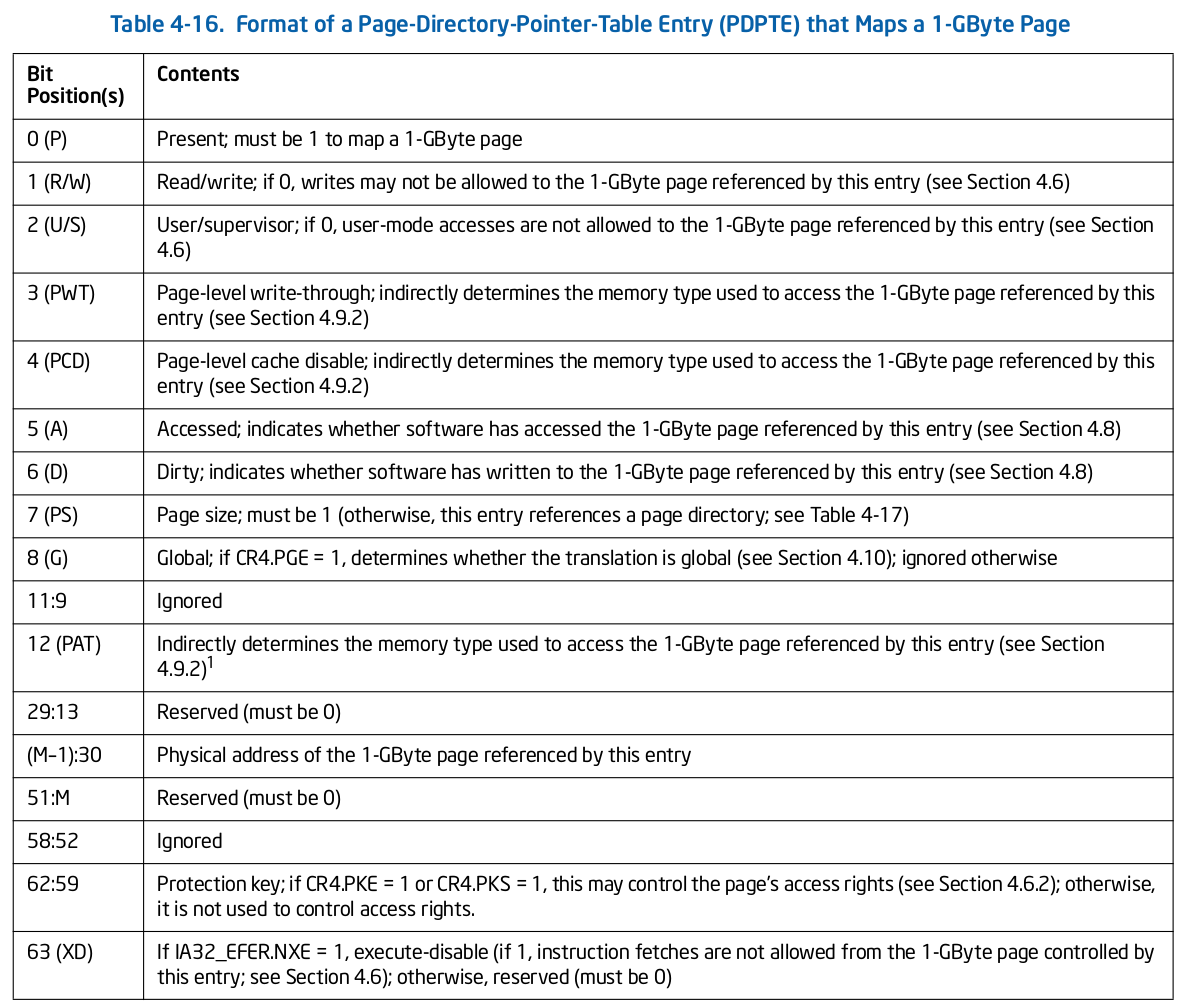

上表描述了 MTRRs 可以配置的 Memory Type 种类,以及每种类型的编码. MTRRs 支持 UC、WC、WT、WP 和 WB 五种 Memory Type,当在 MTRRs 寄存器中配置了 Reserved 之后会引起 general-protection exception (#GP). 当系统 Reset 之后,硬件会 Disable 所有的 Fixed 和 variable MTRRs,并将所有物理区域设置为 Uncached,因此系统初始化需要为指定的物理区域设置指定的 Memory Type, 典型的做法是 BIOS 负责 MTRRs 的初始化,然后操作系统或软件再结合 PAT 设置最终的 Memory Type。PAT(Page Attribute Table) 技术可以提供页级的 Memory Type 设置能力,PAT 与 MTRRs 组合形成最终的 Memory Type,因此 MTRRs 机制只是设置物理区域的 Memory Type,但不能决定最终的 Memory Type。

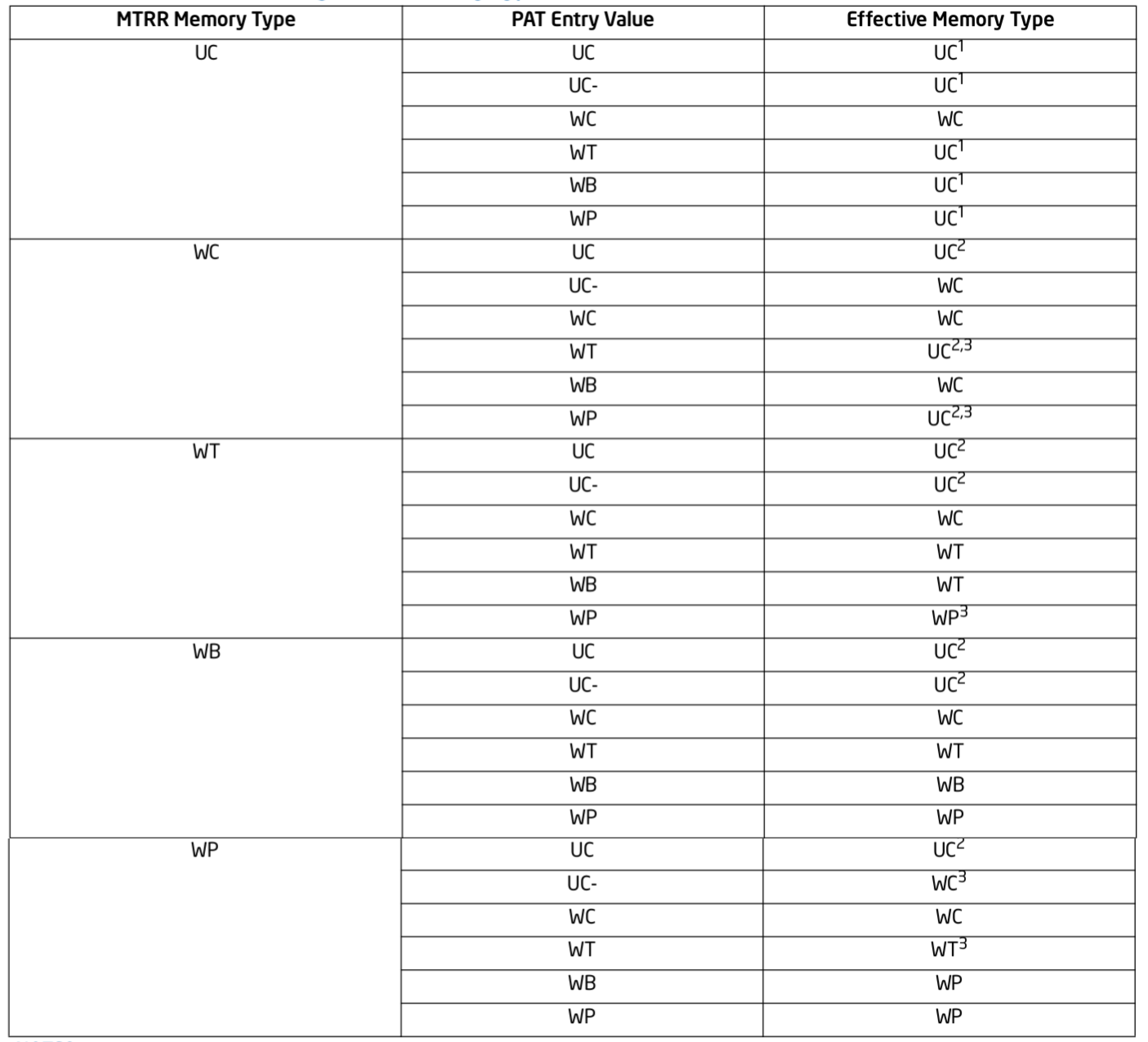

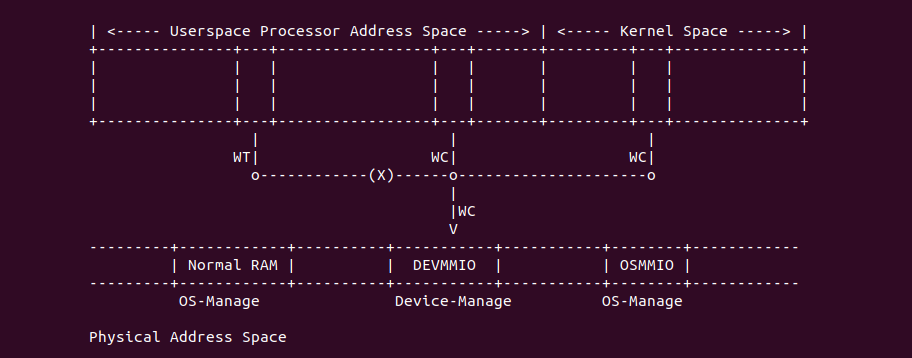

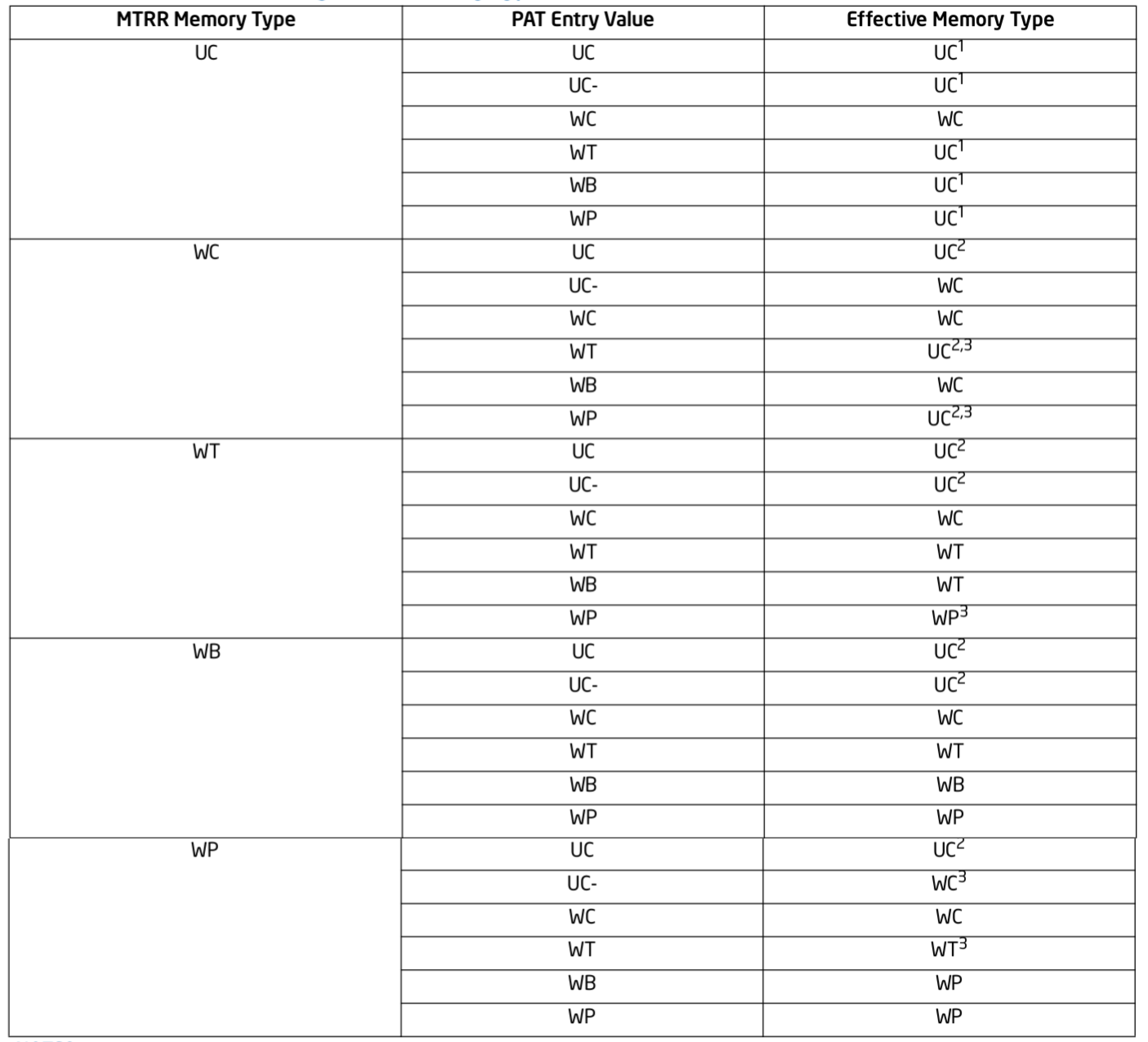

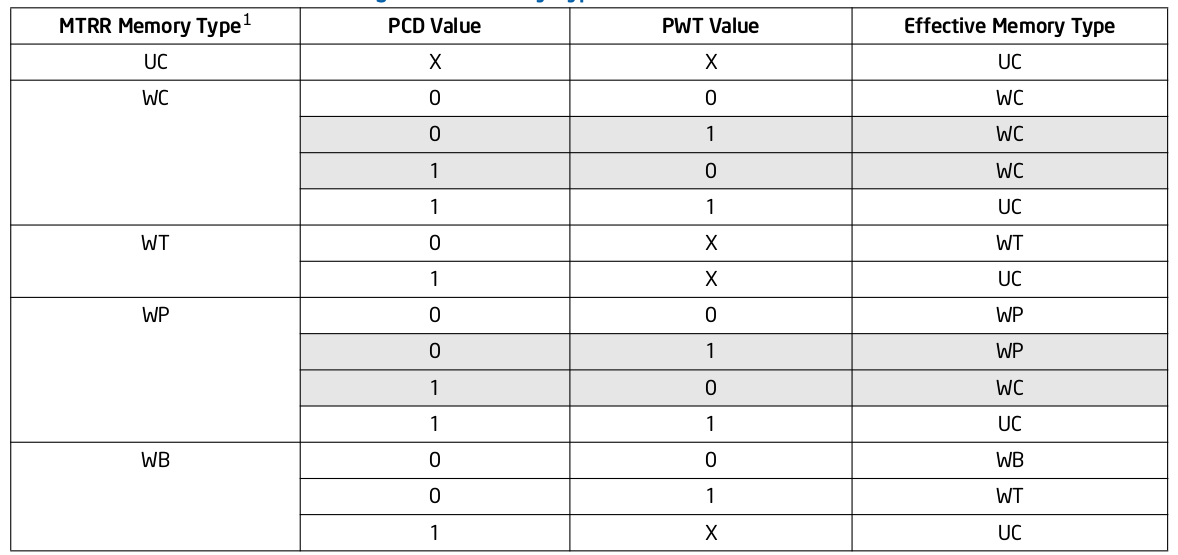

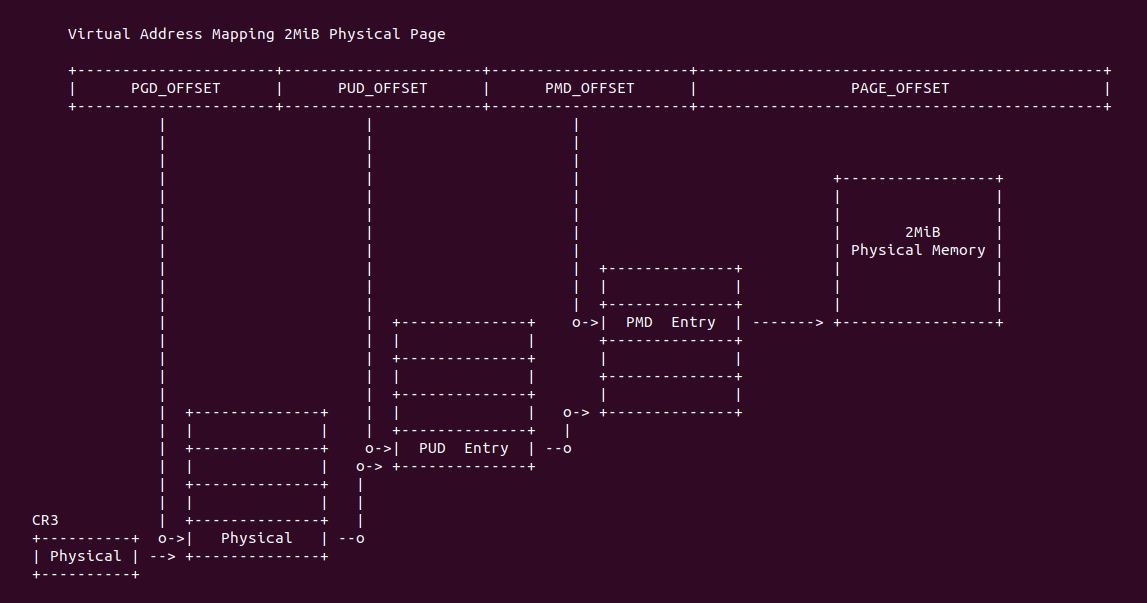

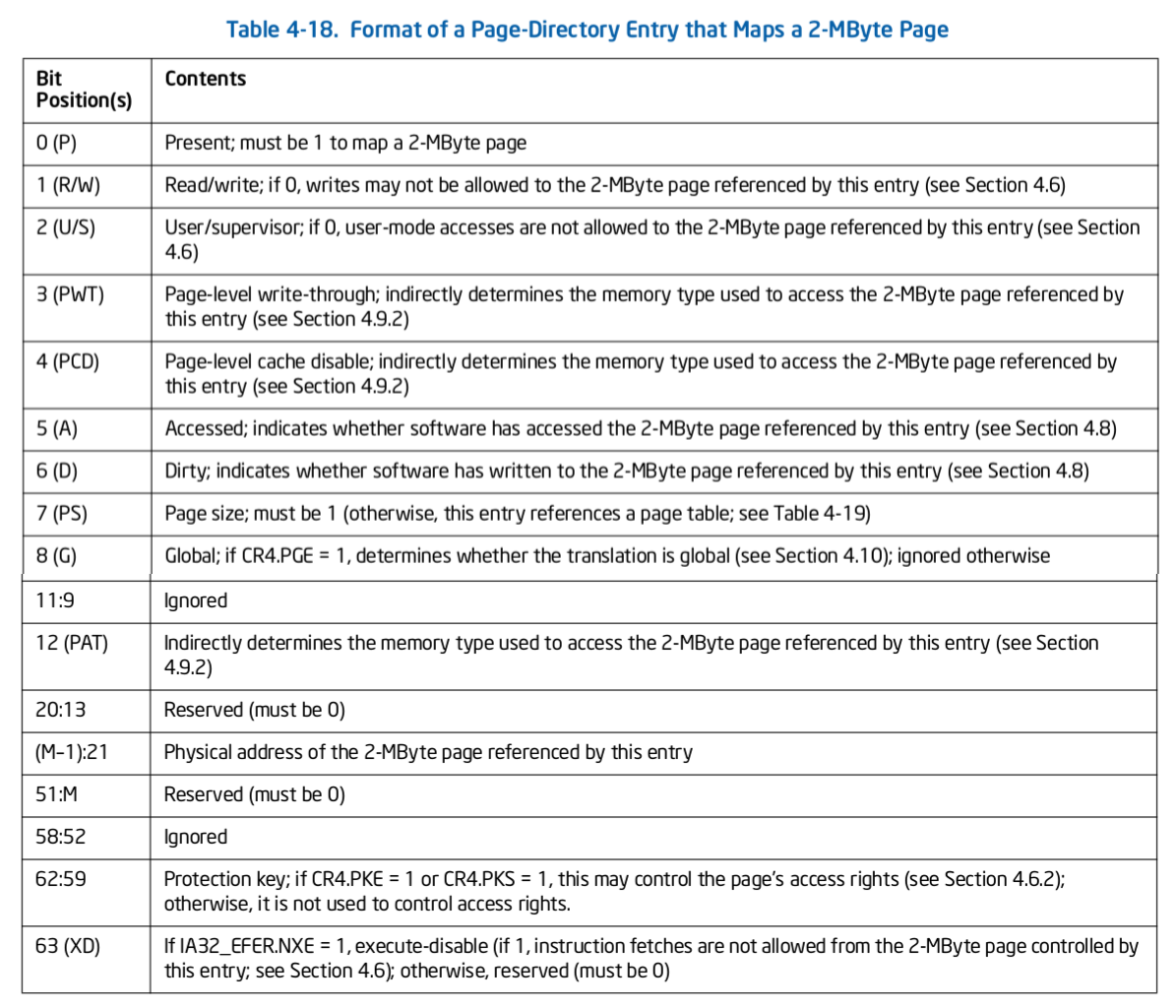

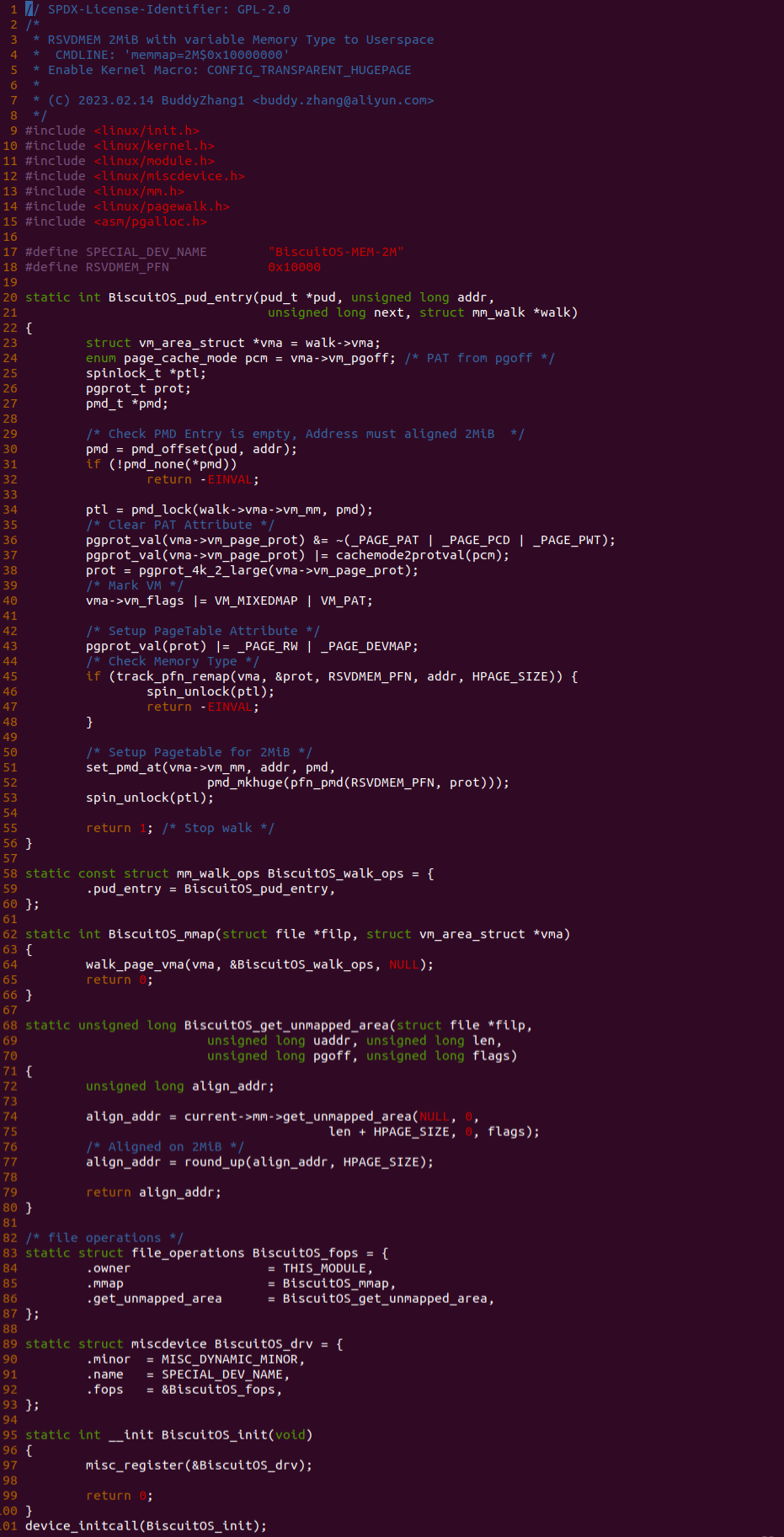

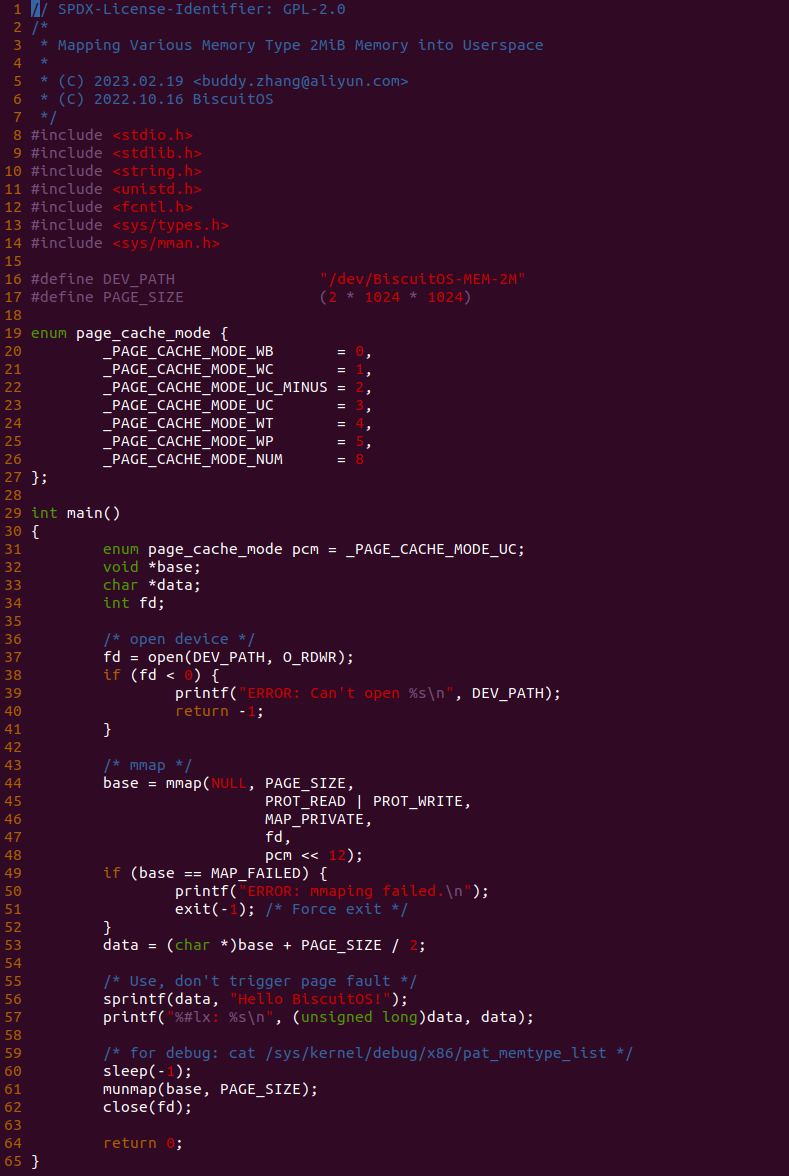

MTRR Memory type 指明通过 MTRRs 机制对某段物理区域设置的 Memory Type,PAT Entry Value 通过页表的 PAT、PWT、PAT 属性进行设置的 Memory Type,两者结合形成 Effective Memory Type, 其为最终生效的 Memory Type.

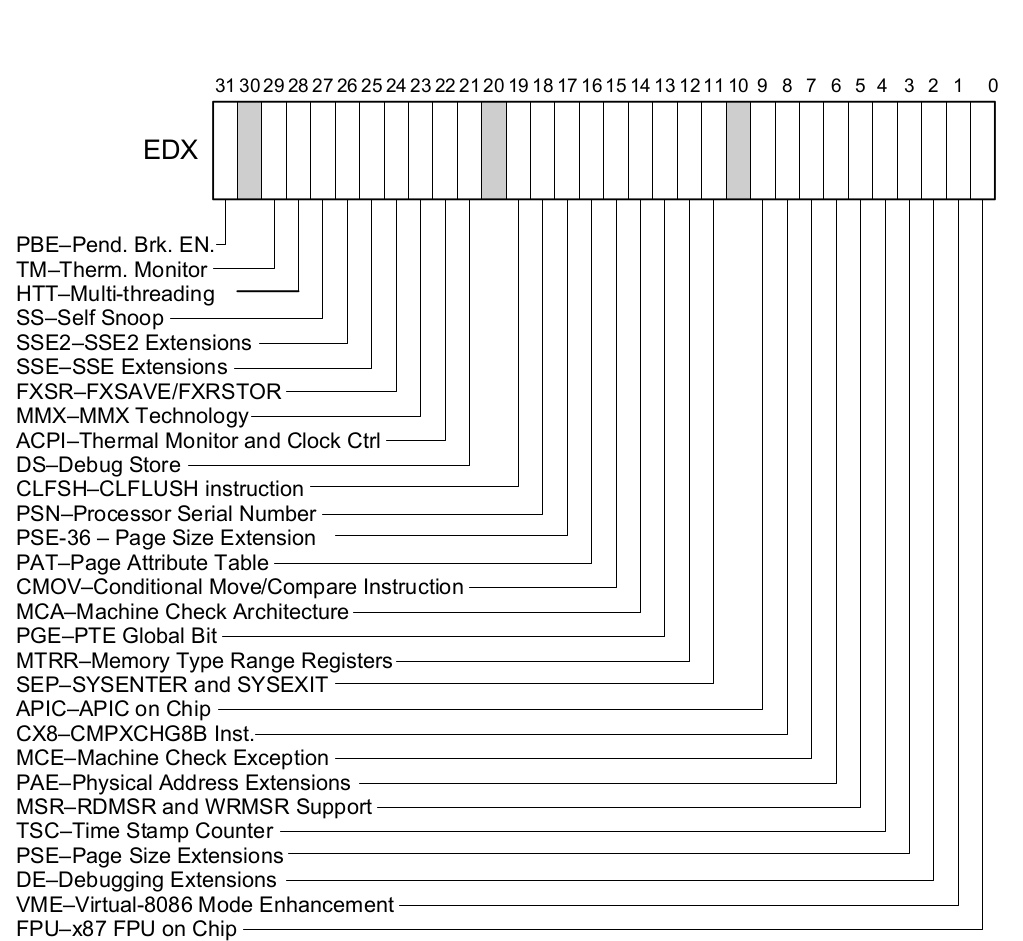

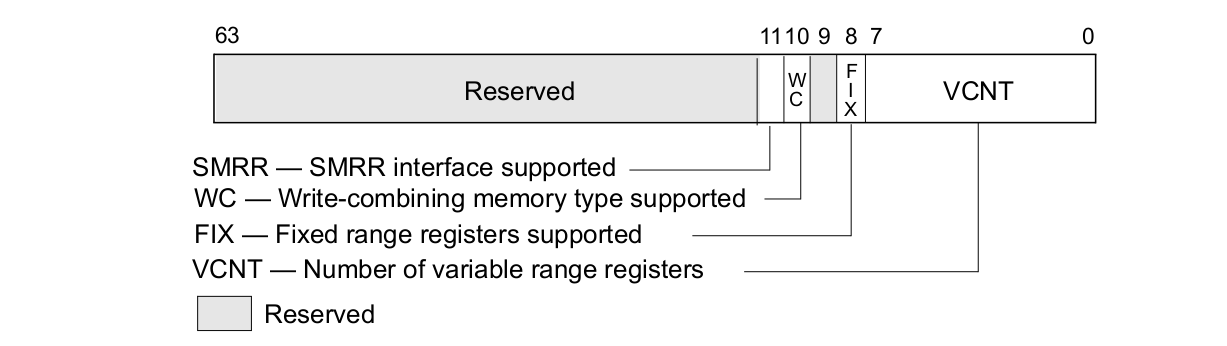

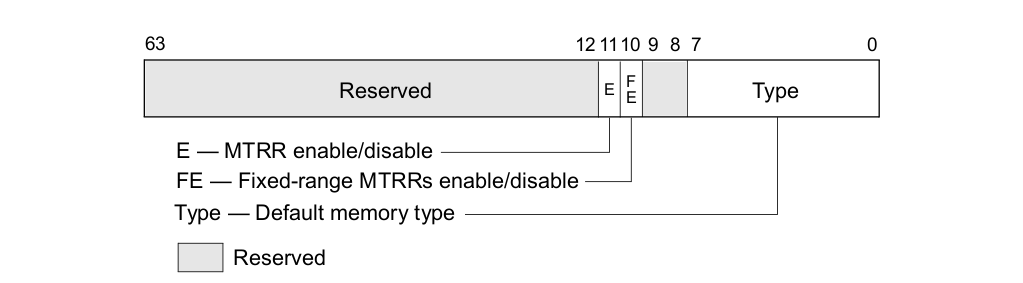

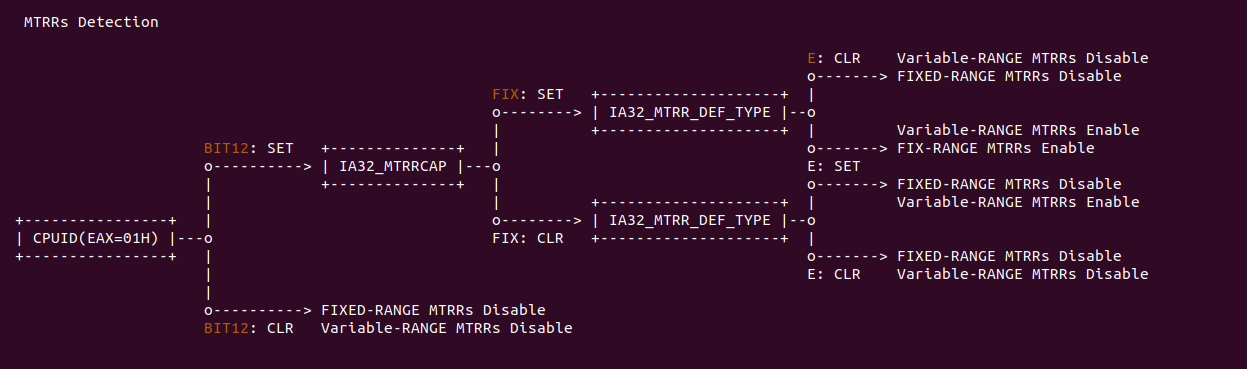

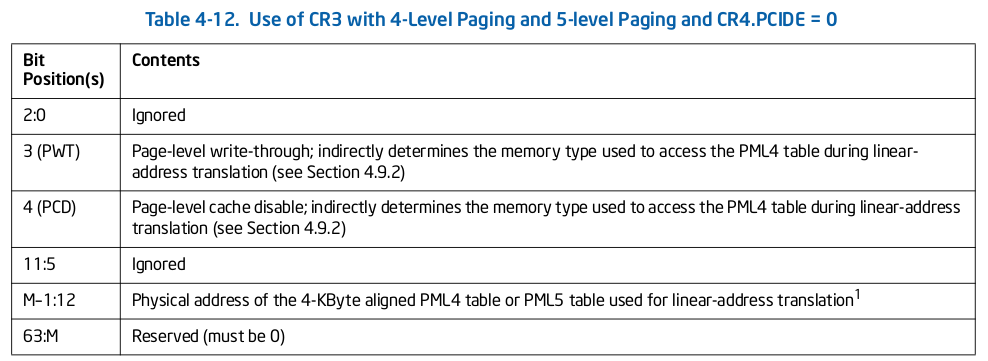

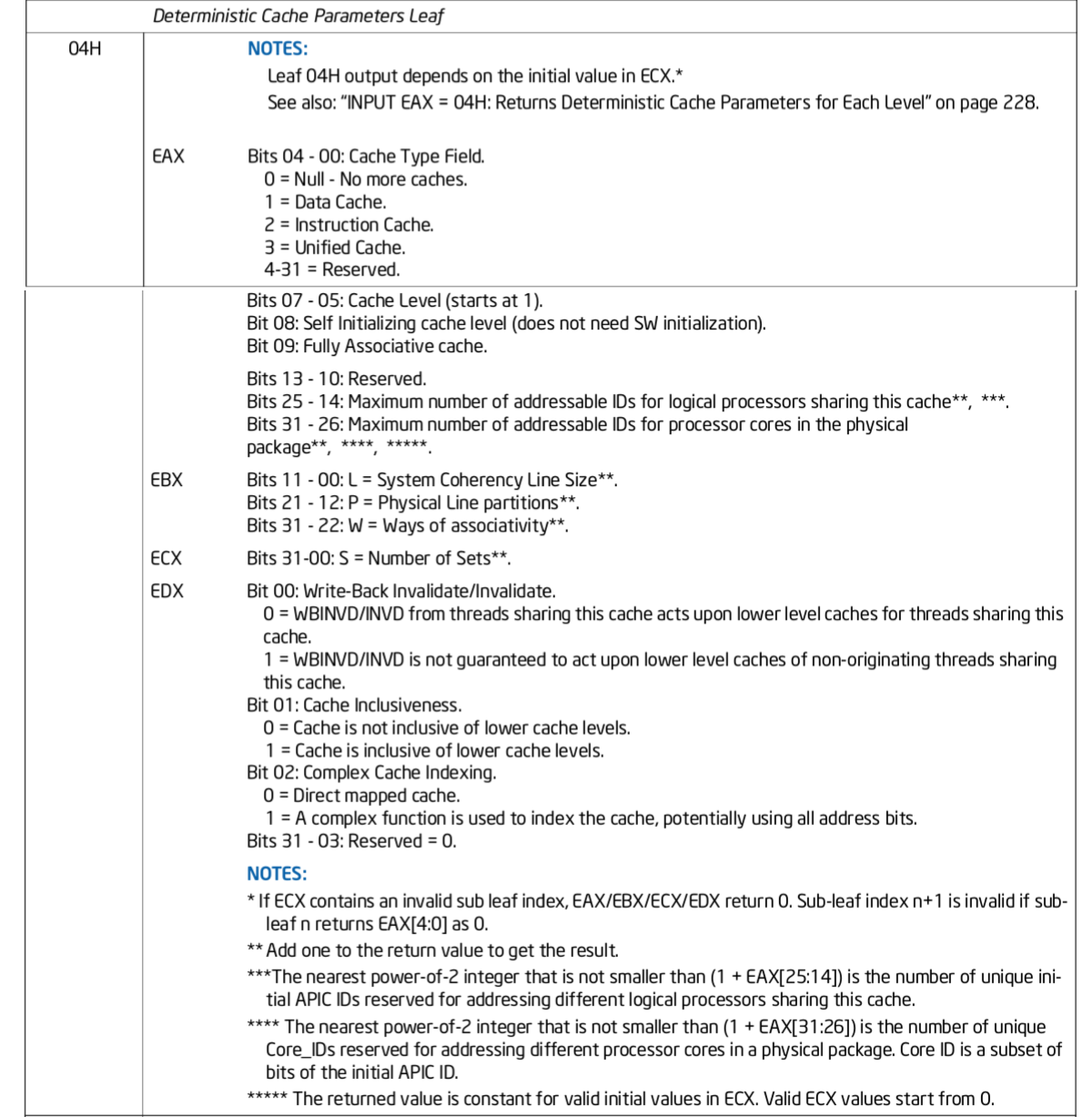

MTRRs Feature Identification

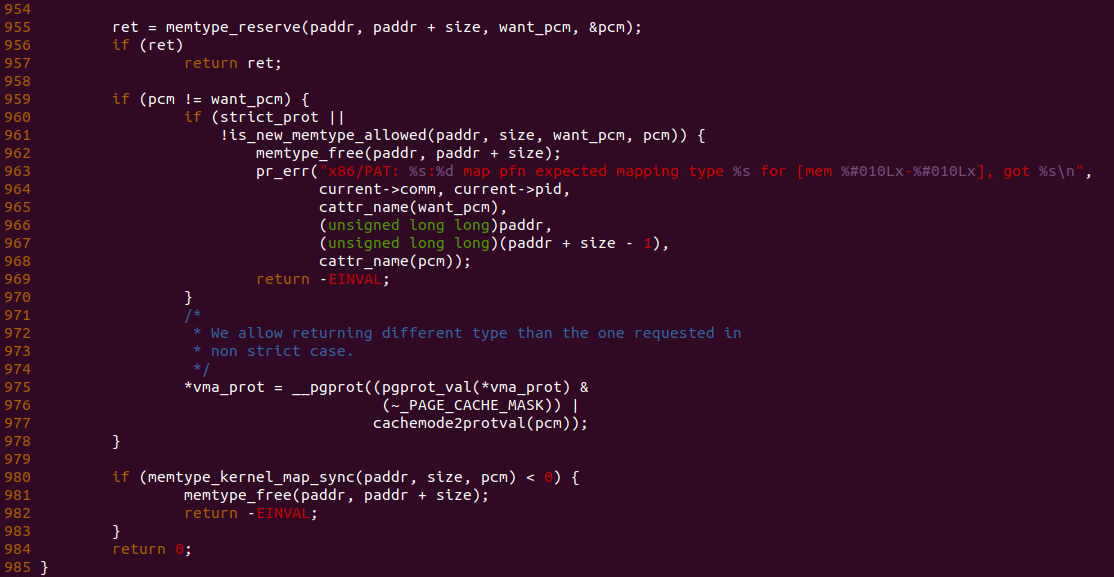

系统是否启用 MTRRs 机制可以通过查看 CPUID 指令(EAX=01H), 当指令返回时可以查看 EDX 寄存器,Bit12 MTRR 指明是否启用 MTRRs 机制,如果该标志位置位,那么 MTRRcap MSR 寄存器记录了 MTRRs 所支持的 Memory Type,以及多少个可变 MTRRs 寄存器等信息; 反之该标志位清零,那么系统不支持 MTRRs 机制.