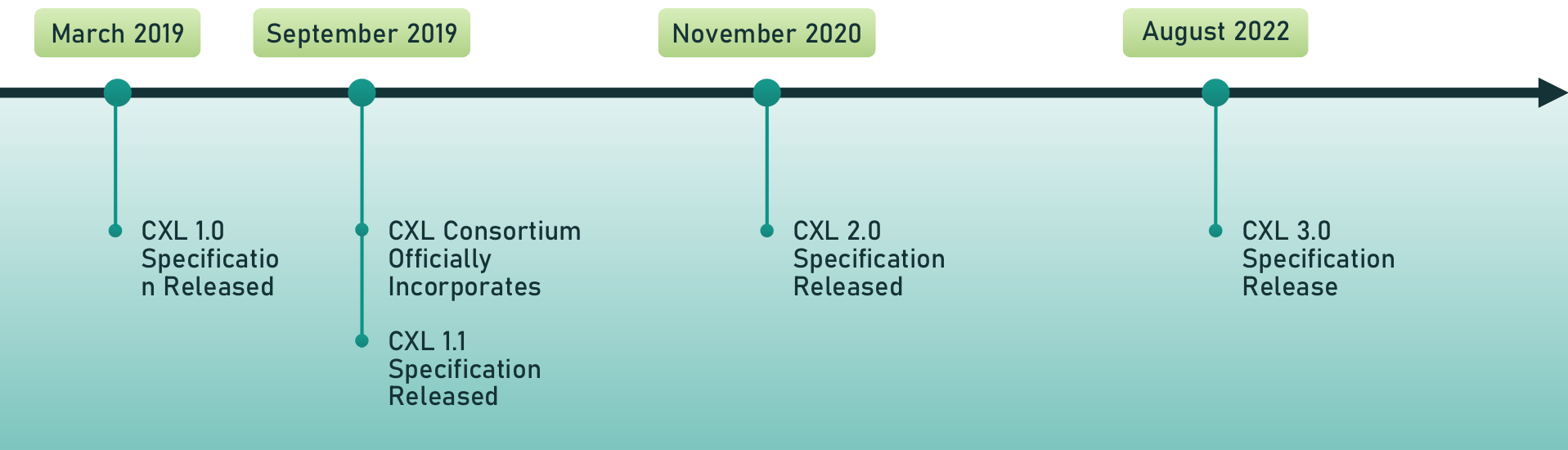

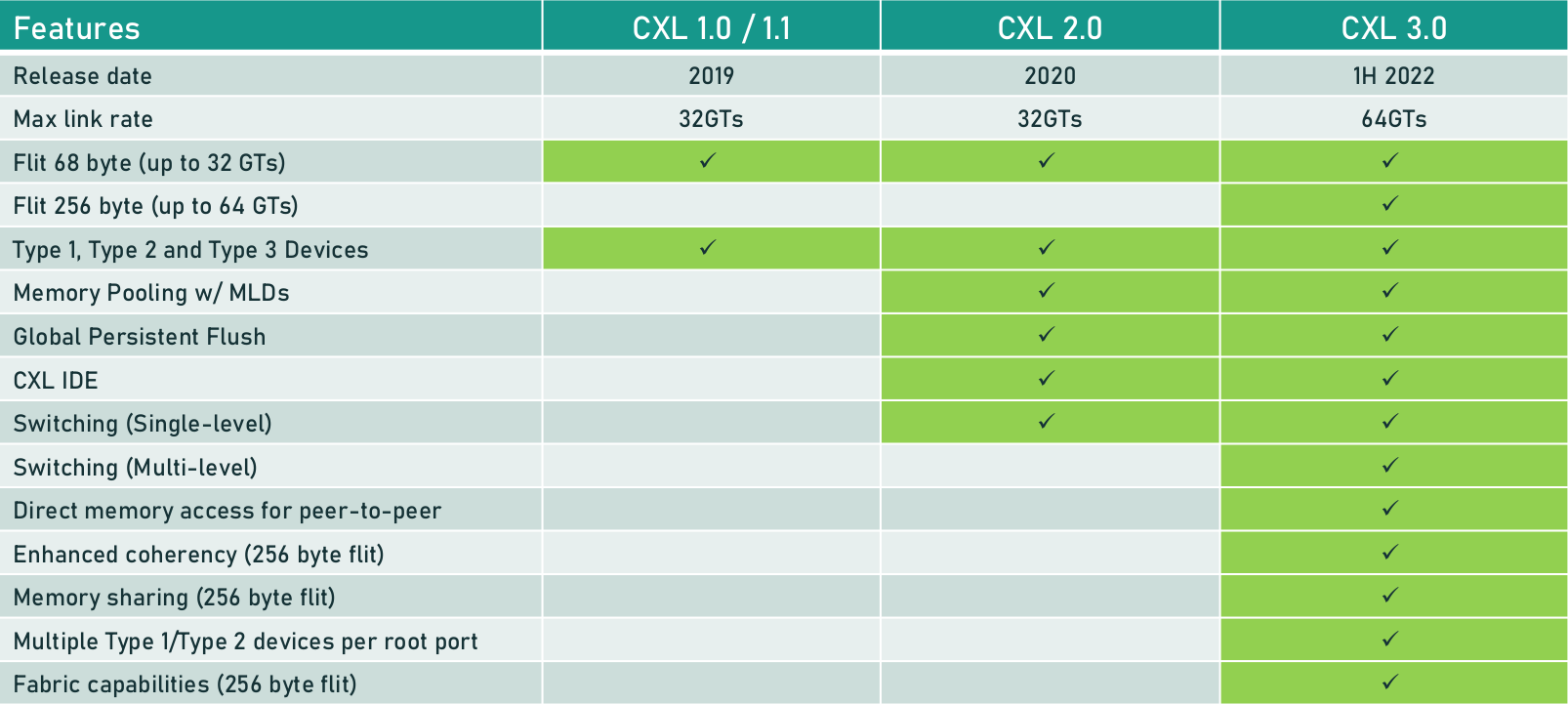

CXL(Compute Express Link) 是一种新的高速互连标准,旨在优化 CPU、内存和加速器之间的数据传输效率。自 2019 年 CXL 1.0 发布以来,CXL 标准迅速发展,并得到了广泛的行业支持。CXL 3.0 作为最新的版本,带来了显著的改进和新特性,进一步推动了高性能计算、数据中心和人工智能等领域的发展。CXL 的发展始于 2019 年,旨在提供一个统一的标准,使得不同厂商的 CPU、内存和加速器能够高效互连。以下是 CXL 的发展历程:

- 2019年: CXL 1.0 发布,提供了基础的互连功能。

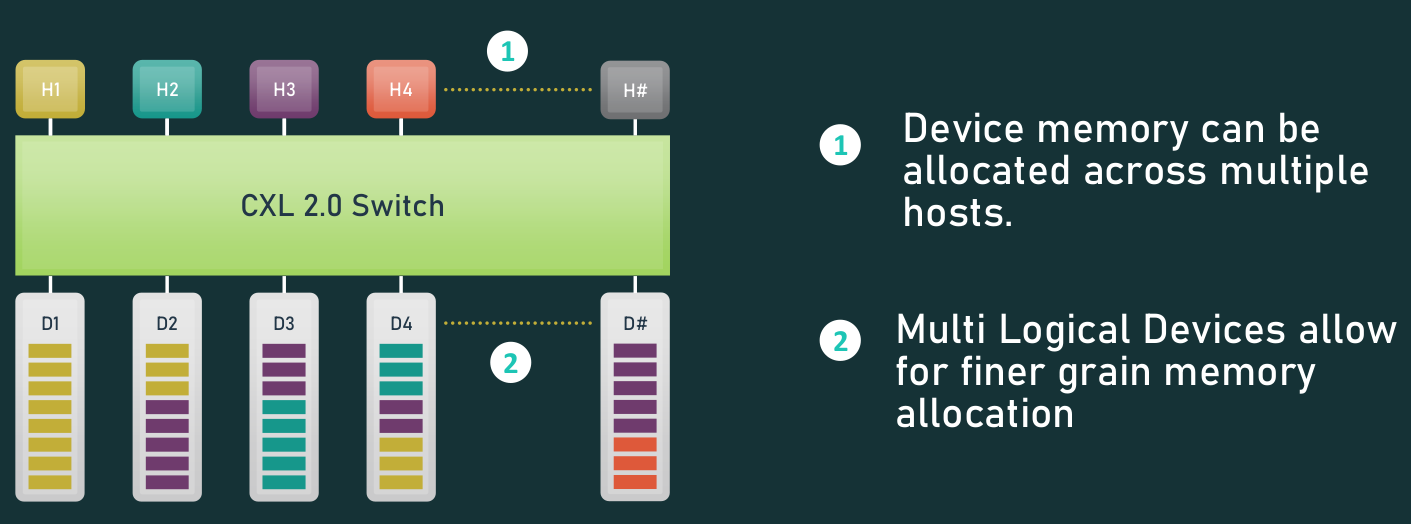

- 2020年: CXL 2.0 发布,增加了内存池化、多主机支持和持久性内存支持

- 2022年: CXL 3.0 发布,进一步增强了功能和性能,支持更复杂的系统架构和应用场景。

在现代计算系统中,数据传输效率对于整体性能至关重要。传统的互连技术如PCIe在面对不断增长的数据传输需求时显得力不从心。CXL 通过提供低延迟、高带宽的数据传输解决方案,显著提高了计算和存储资源的利用效率。

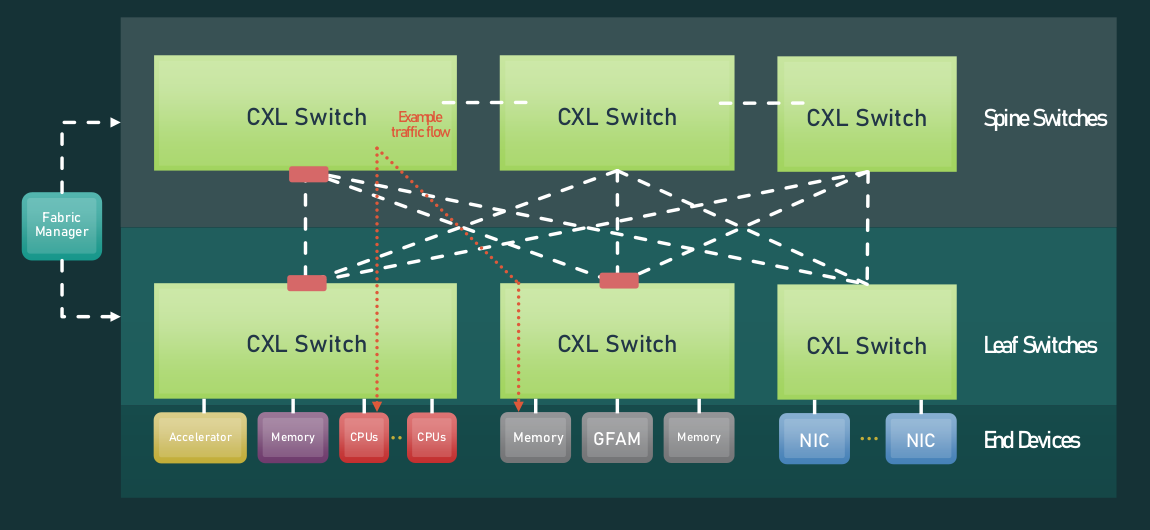

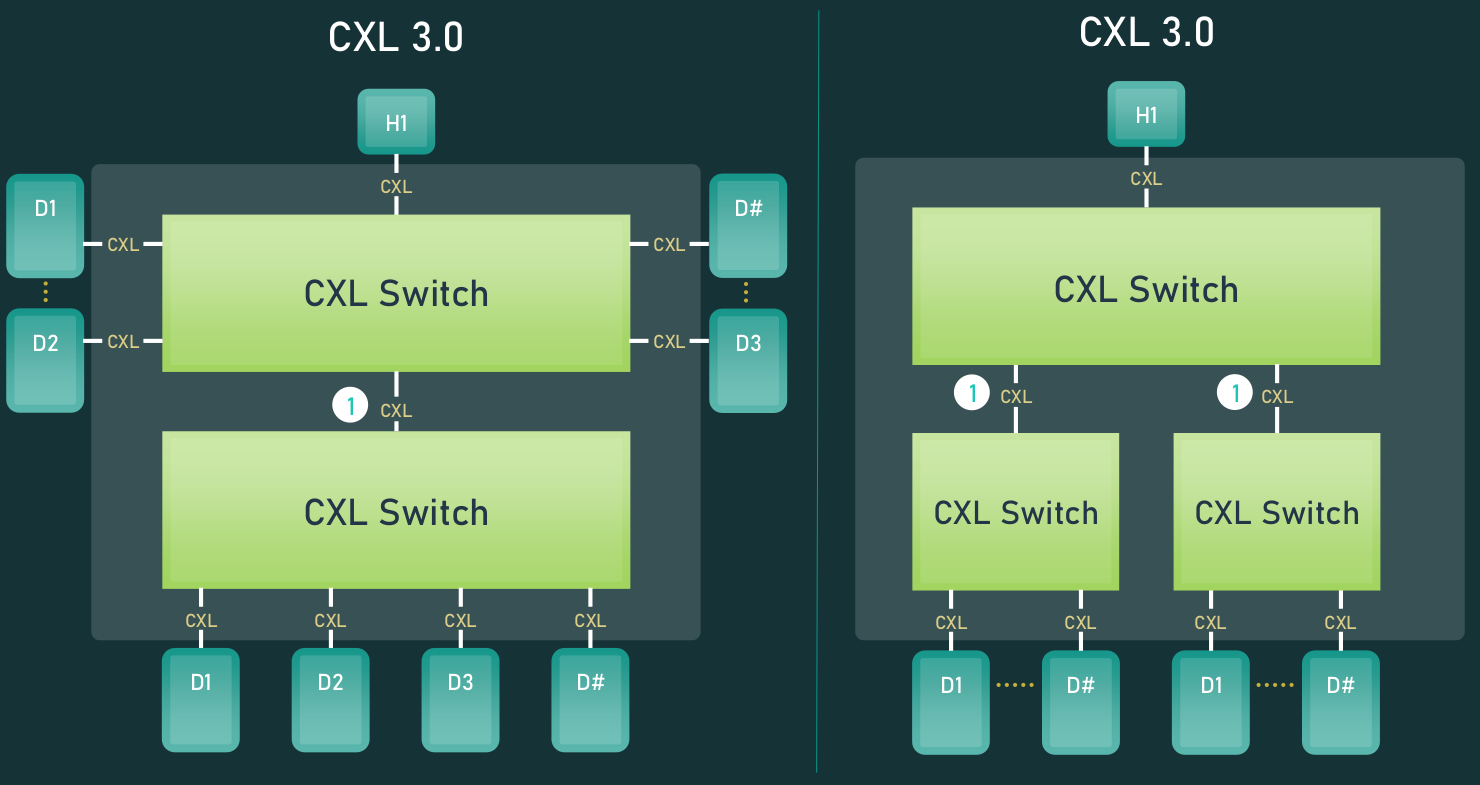

CXL 3.0 是 CXL 标准的最新版本,带来了许多新的特性和改进,进一步提升了系统的性能和可扩展性。CXL 3.0 的设计目标是在现有 CXL 2.0 的基础上,提供更高的带宽、更低的延迟和更强的安全性. CXL 3.0 的设计目标:

- 更高的性能: 进一步提高数据传输的带宽和降低延迟

- 更强的安全性: 增强数据传输的安全性,防止未经授权的访问

- 更好的可扩展性: 支持更大规模的系统和更多的设备。

- 简化的系统集成: 降低系统集成的复杂性,提供更好的兼容性和易用性

CXL 3.0 的新特性

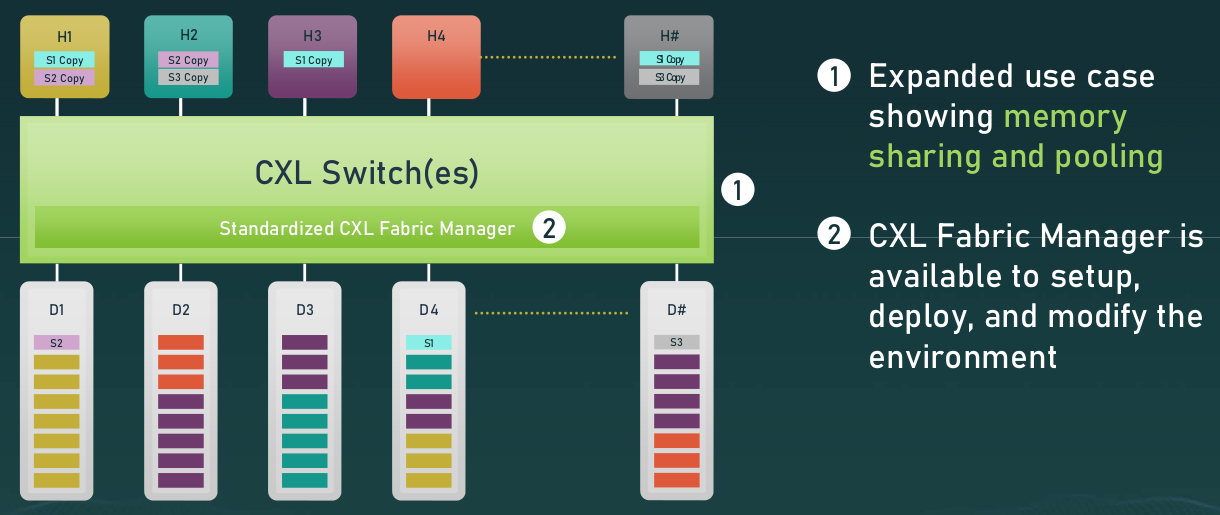

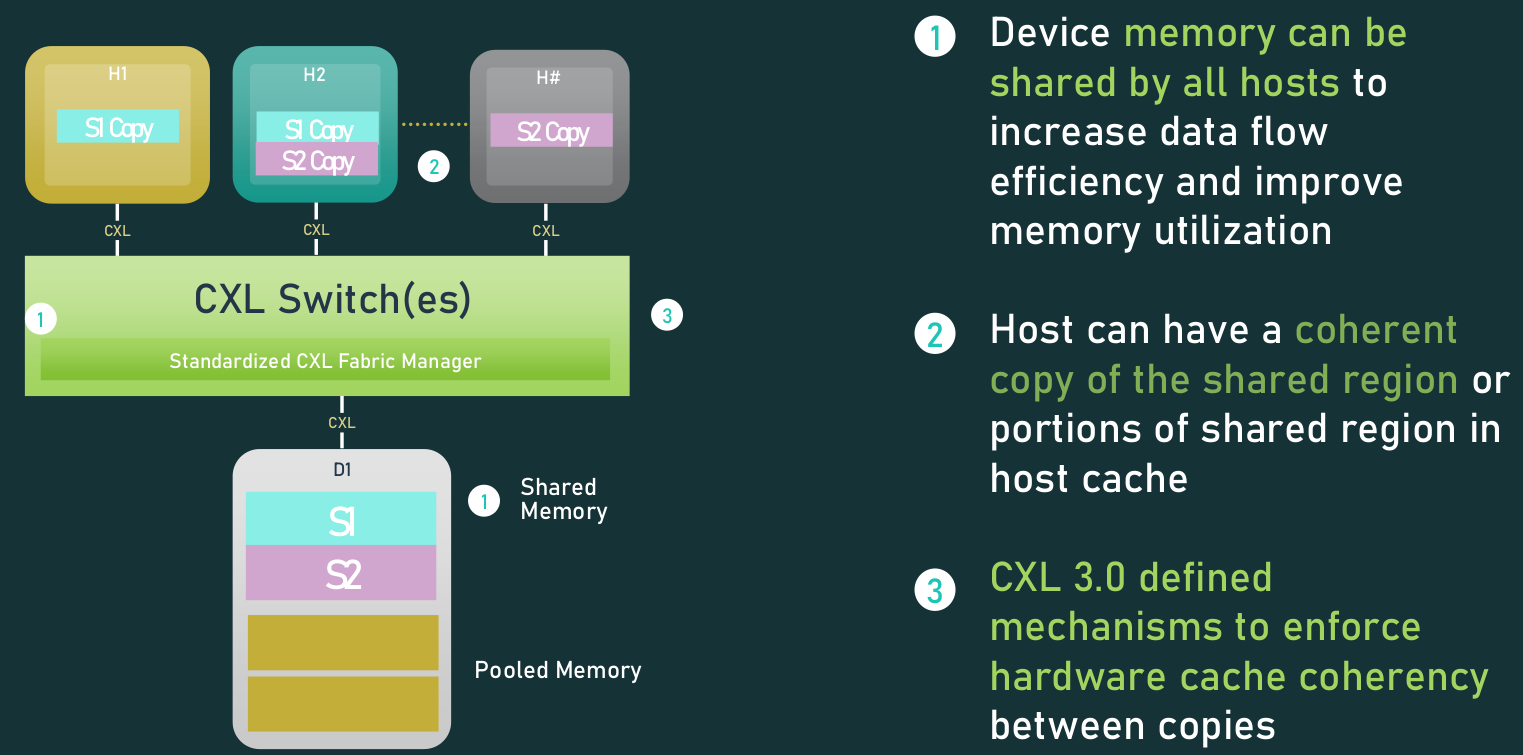

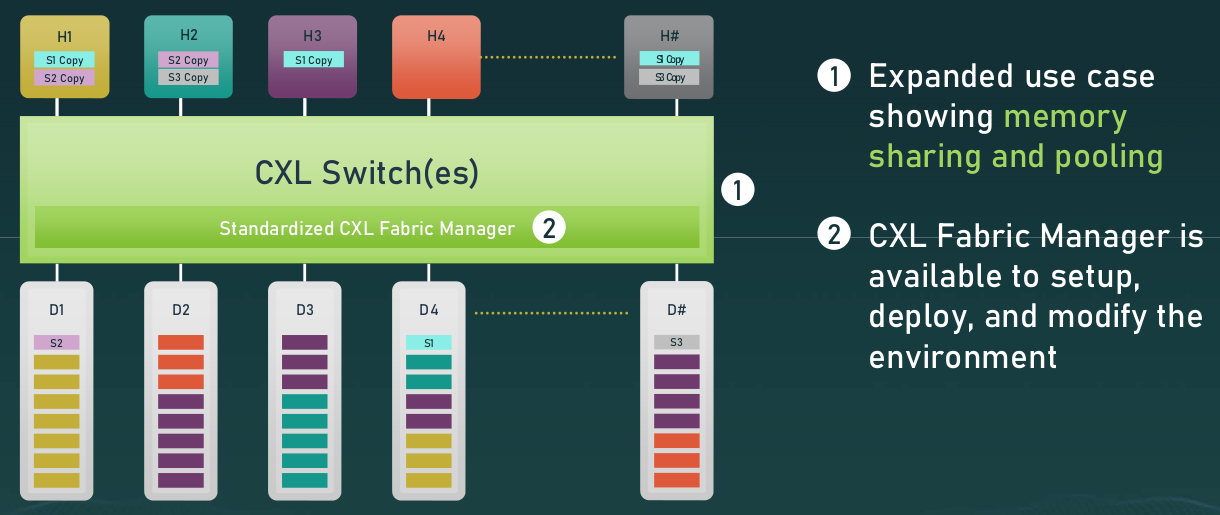

内存池化增强: CXL 3.0 在内存池化功能上进行了显著增强,支持更大规模的内存池和更多的主机。这意味着在大型数据中心和高性能计算环境中,多个主机可以高效地共享内存资源,进一步提高资源利用率和系统灵活性。

硬件管理能力: CXL 3.0 引入了增强的硬件管理能力,允许更精细地控制和管理硬件资源。这包括更好的资源分配、监控和调度机制,使得系统管理员可以更高效地利用硬件资源。

高速链路: CXL 3.0 进一步提升了数据传输的带宽和速度,通过优化协议和数据传输路径,实现了更高效的通信。这对于需要大量数据传输的应用,如人工智能训练和大数据分析,具有显著的性能提升。

硬件加速器支持: CXL 3.0 对硬件加速器的支持进行了增强,允许更多类型的加速器(如GPU、FPGA、专用AI芯片等)通过 CXL 接口连接。这使得系统能够更灵活地利用各种硬件加速器,提高计算性能和效率。

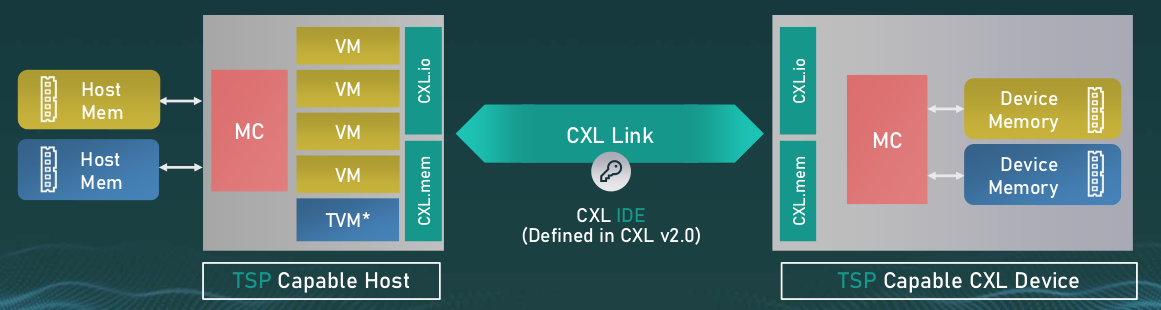

更强的安全性: CXL 3.0在安全性方面进行了显著增强,主要包括:

- 数据加密: 提供更强的数据加密机制,确保数据传输的安全性

- 访问控制: 引入更严格的访问控制机制,防止未经授权的访问

- 安全监控: 增加对数据传输的安全监控,及时检测和防止安全威胁

一致性协议: CXL 3.0 引入了改进的一致性协议,确保系统中所有设备之间的数据一致性。这对于分布式计算和大规模数据处理应用尤为重要,能够有效防止数据不一致和冲突问题

CXL 3.0 与 CXL 2.0 的对比

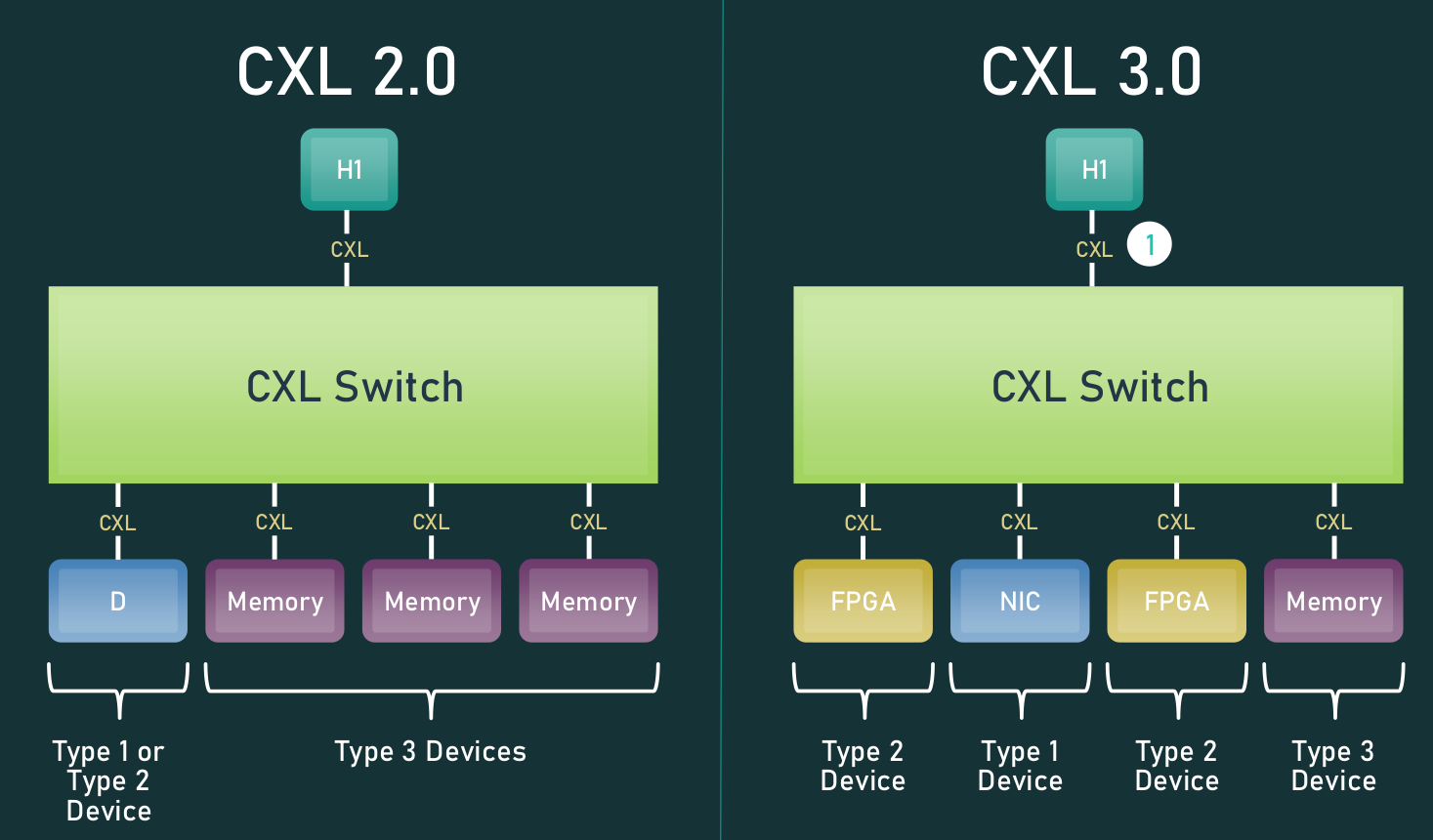

CXL 2.0 的架构主要由主机控制器、加速器和内存设备组成,支持内存池化、多主机和持久性内存。

CXL 3.0 在 CXL 2.0 的基础上进行了多项改进,主要包括:

- 扩展的内存池化: 支持更大规模的内存池和更多的主机

- 增强的硬件管理: 提供更精细的硬件资源管理能力

- 高速链路: 进一步提升数据传输带宽和速度

- 硬件加速器支持: 支持更多类型的硬件加速器

- 改进的一致性协议: 确保系统中所有设备之间的数据一致性

内存池化

CXL 2.0 支持内存池化,但规模有限

CXL 3.0 扩展了内存池化功能,支持更大规模的内存池和更多的主机。

持久性内存

CXL 2.0 支持持久性内存,但性能和可靠性有限

CXL 3.0 进一步增强了对持久性内存的支持,提供更高的性能和可靠性。