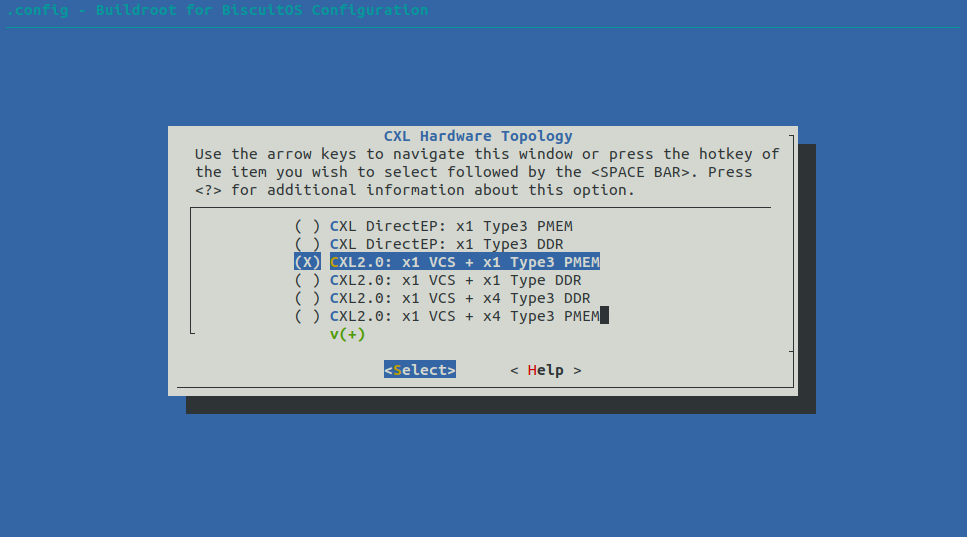

BiscuitOS 已经全量支持 CXL 2.0 实践环境,部署基于《BiscuitOS 用户手册 1.2 节》. BiscuitOS 提供了不用硬件拓扑的 CXL 实践环境,接下来对每种环境进行讲解:

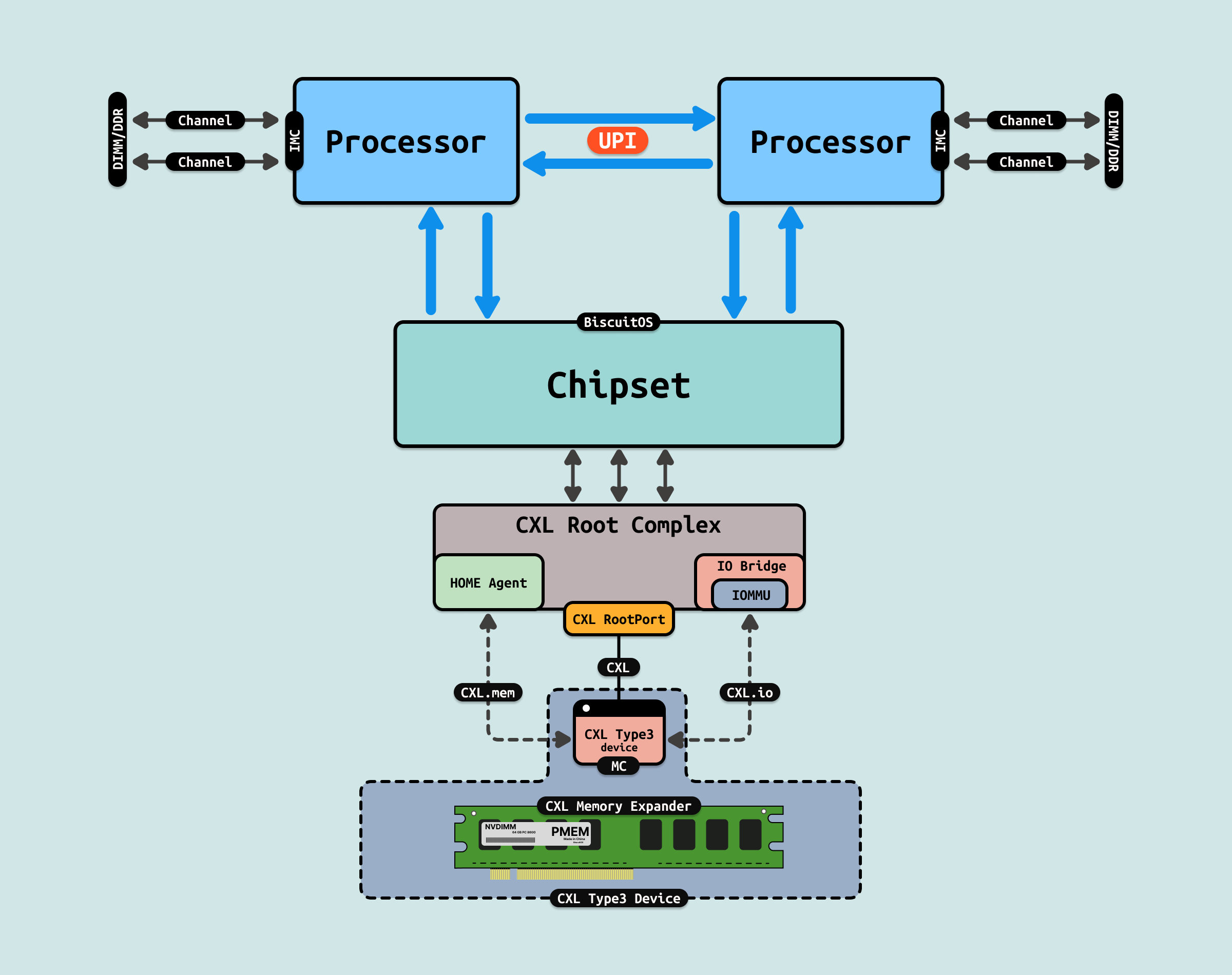

CXL DirectEP: x1 Type3 PMEM: 该选项对应的 CXL 硬件拓扑如上图,CXL Type3 设备直接连接到 CXL ROOTPORT 上,CXL BUS 使用 “PCI-C” 总线,因此 PootPort 的 BDF 为 “0C:00.0”, CXL Type3 设备的 BDF 则为 “0D:00.0”. CXL Type3 设备的内存颗粒是 PMEM.

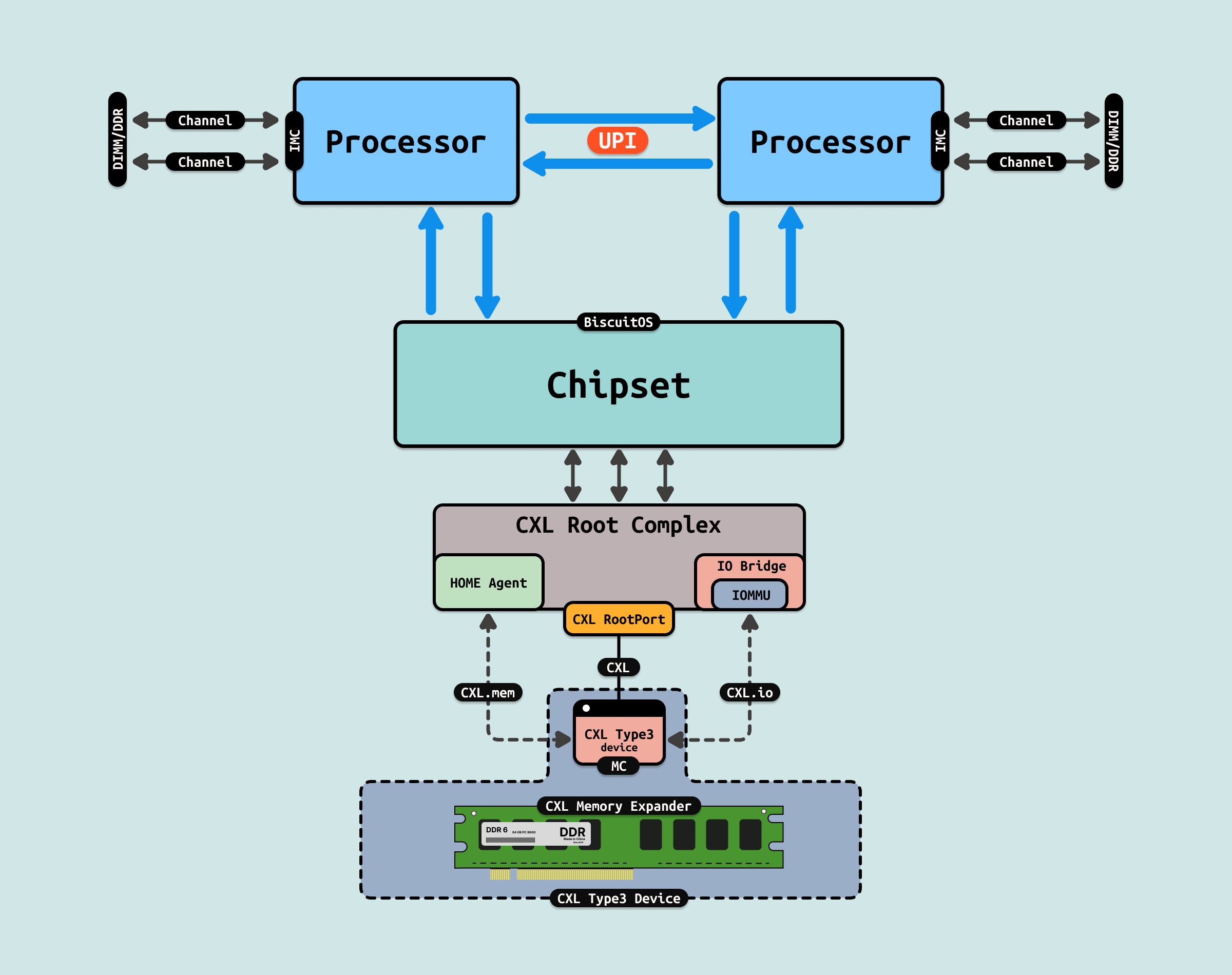

CXL DirectEP: x1 Type3 DDR: 该选项对应的 CXL 硬件拓扑如上图,CXL Type3 设备直接连接到 CXL ROOTPORT 上,CXL BUS 使用 “PCI-C” 总线,因此 PootPort 的 BDF 为 “0C:00.0”, CXL Type3 设备的 BDF 则为 “0D:00.0”. CXL Type3 设备的内存颗粒是 DDR.

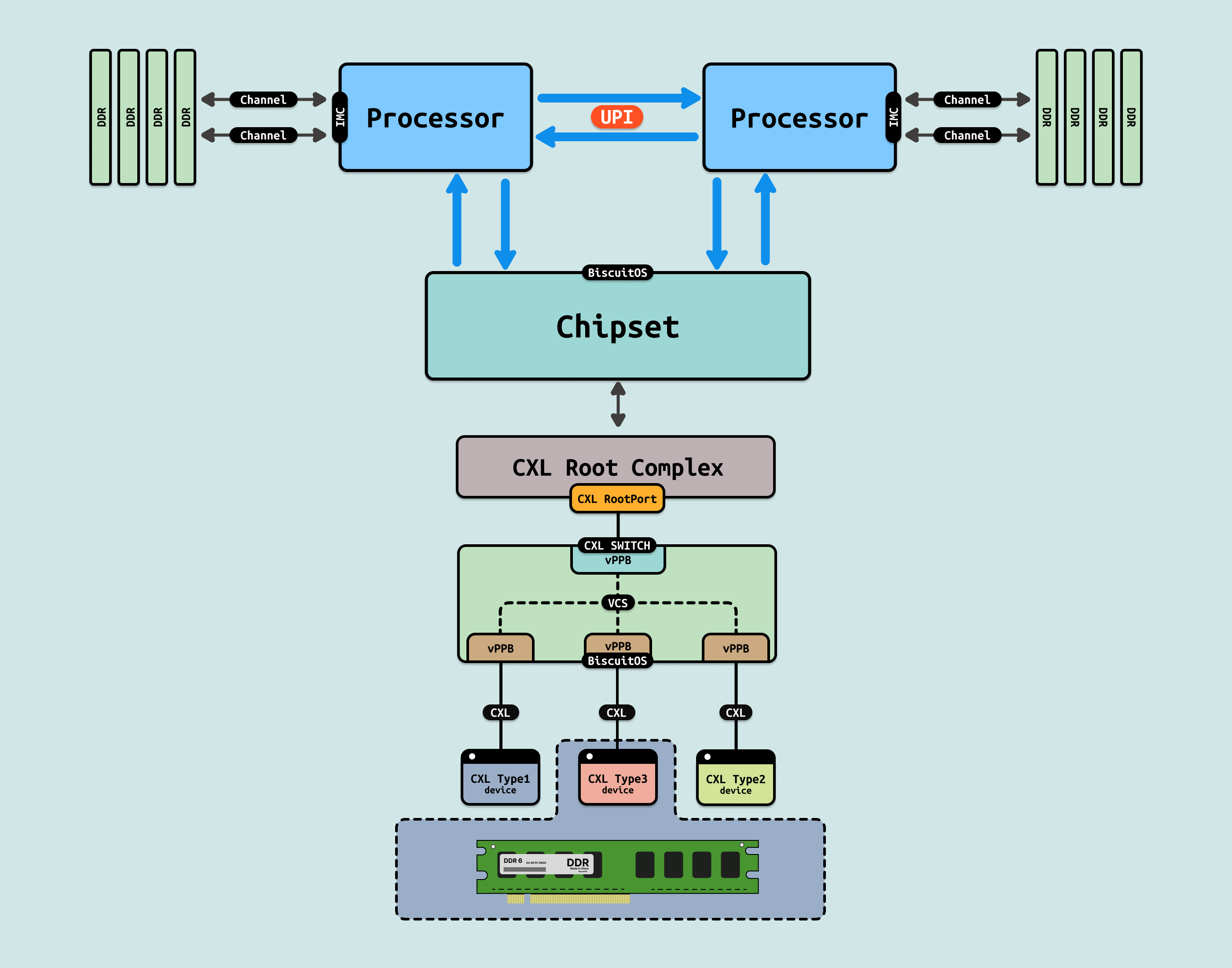

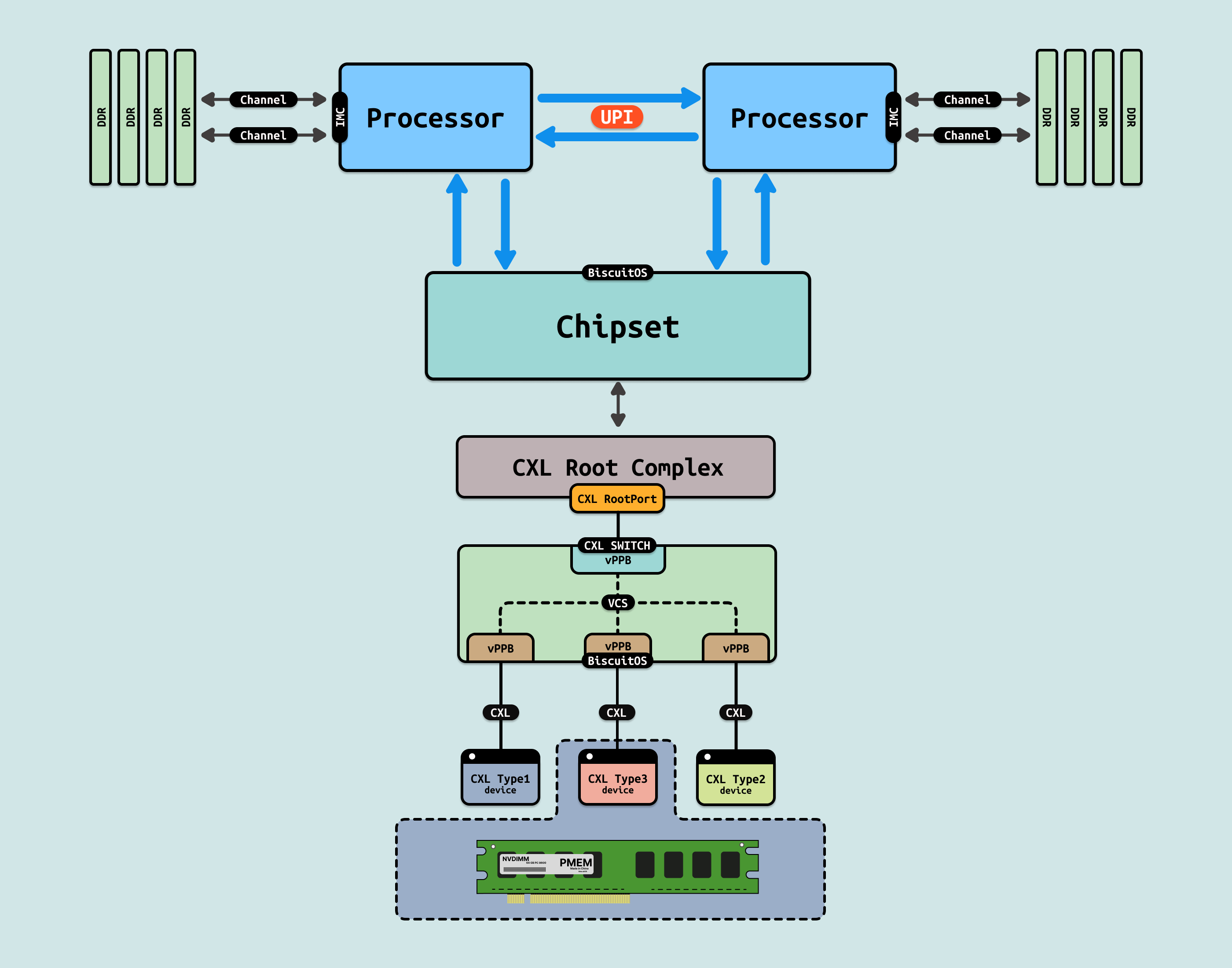

CXL2.0: x1 VCS + x1 Type3 PMEM: 该选项对应的 CXL 硬件拓扑如上图,包含了一台主机,CPU 通过南桥转 CXL Host Bridge,其引入 PCI:0C 总线,直接连接到 CXL Root Complex,CXL RC 里仅包含一个 CXL RootPort,此时 CXL RootPort 的 BDF 为 “0C:00.0”. RP 通过 “BUS-D” 总线连接到 CXL SWITCH 上,SWITCH 只虚拟了一个 VCS,那么 Upstream Port(UP vPPB) 的 BDF 为 “0D:00.0”, VCS 通过 “BUS-E” 总线连接 4 个 Downstream Port(DP vPPB), 每个 DP 都连接到一个 PCIe 插槽上插入一个 “CXL Type3” 设备,该设备的 BDF 为 “0F:00.0”,该设备的内存颗粒是 PMEM.

CXL2.0: x1 VCS + x1 Type DDR: 该选项对应的 CXL 硬件拓扑如上图,包含了一台主机,CPU 通过南桥转 CXL Host Bridge,其引入 PCI:0C 总线,直接连接到 CXL Root Complex,CXL RC 里仅包含一个 CXL RootPort,此时 CXL RootPort 的 BDF 为 “0C:00.0”. RP 通过 “BUS-D” 总线连接到 CXL SWITCH 上,SWITCH 只虚拟了一个 VCS,那么 Upstream Port(UP vPPB) 的 BDF 为 “0D:00.0”, VCS 通过 “BUS-E” 总线连接 4 个 Downstream Port(DP vPPB), 每个 DP 都连接到一个 PCIe 插槽上插入一个 “CXL Type3” 设备,该设备的 BDF 为 “0F:00.0”,该设备的内存颗粒是 DDR.