CXL Hardware Topology

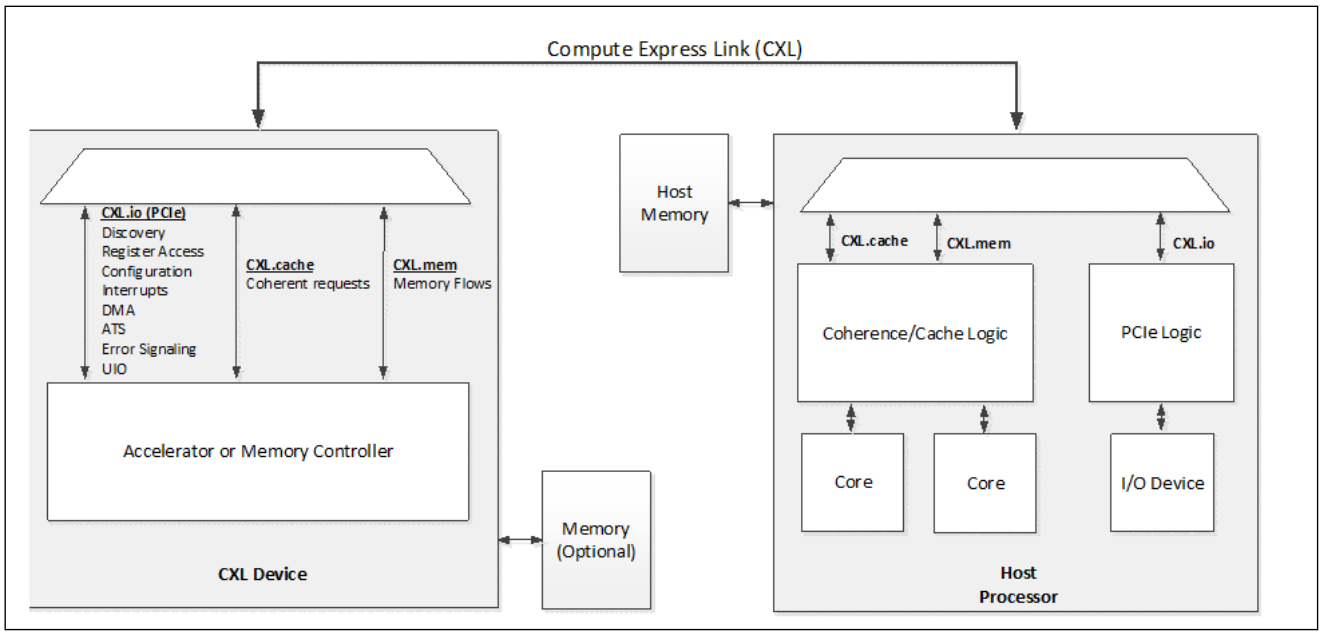

CXL1.0/1.1: CXL 是一种动态多协议技术,旨在支持加速器和内存设备。CXL 提供了一套丰富的协议,包括类似于 PCIe 的 I/O 语义(即 CXL.io)、缓存协议语义(即 CXL.cache)和内存访问语义(即 CXL.mem),可以通过离散或封装内连接实现。CXL.io 用于发现和枚举、错误报告、对 CXL 内存和主机物理地址(HPA) 进行点对点(P2P)访问。CXL.cache 和 CXL.mem 协议可以根据特定的加速器或内存设备使用模型选择性地实现. CXL 的一个重要优点是它为加速器访问系统和系统访问连接到 CXL 设备的内存提供了低延迟、高带宽的路径。上图显示通过 CXL 连接到主处理器的设备的概念图.

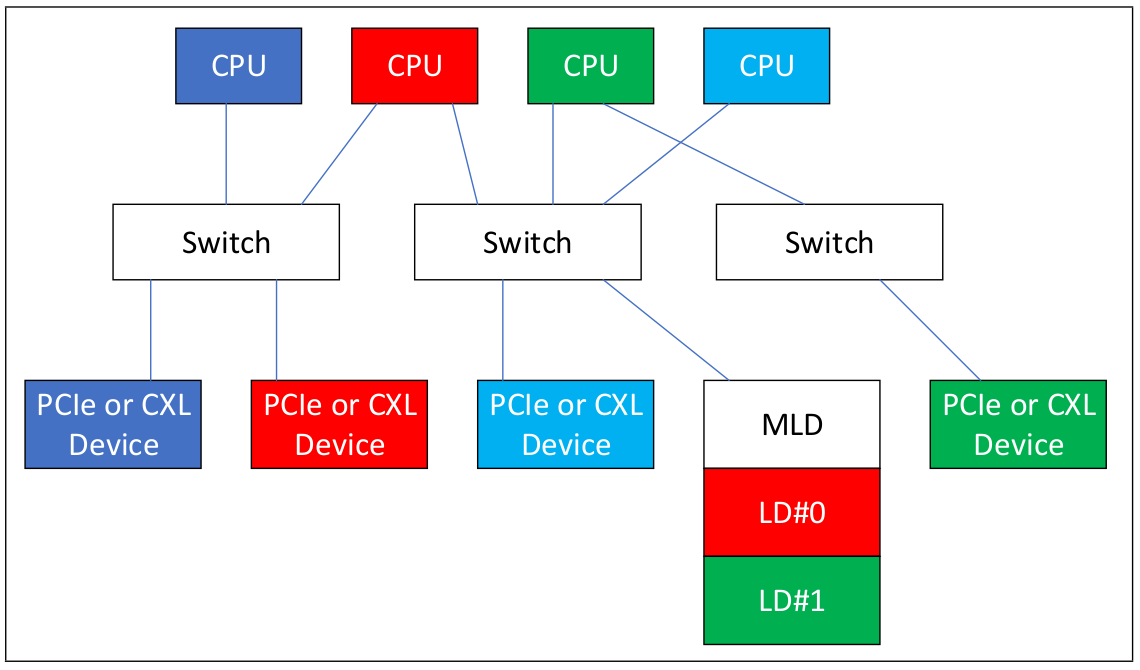

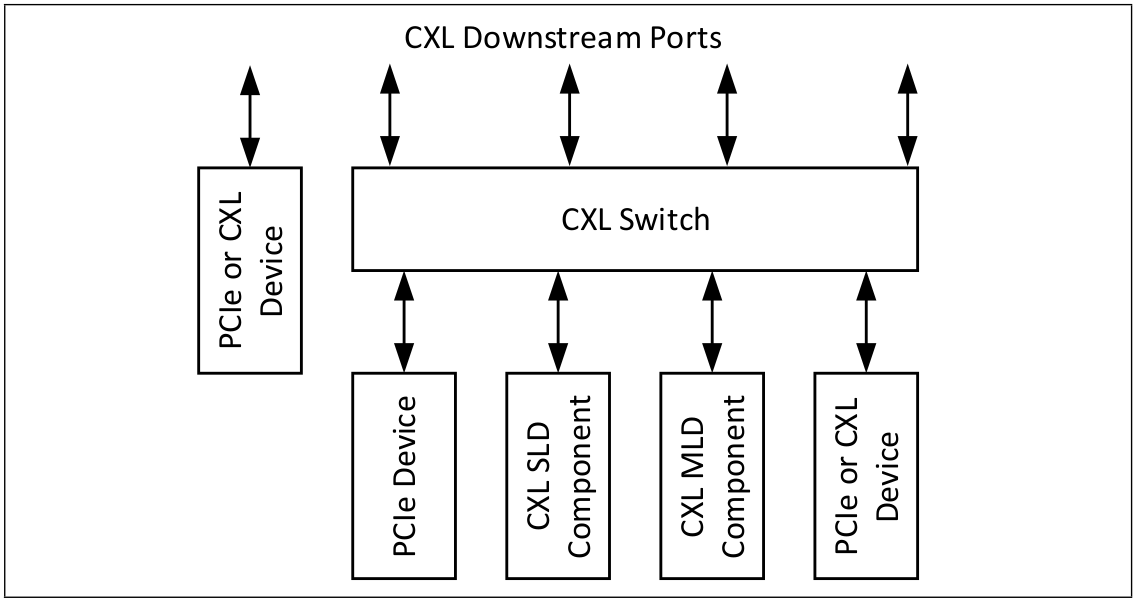

CXL2.0: CXL 2.0 规范在完全向后兼容 CXL 1.1(及 CXL 1.0)规范的同时,支持比 CXL 1.1 规范更多的使用模型。它支持托管热插拔、安全增强、持久内存支持、内存错误报告和遥测。CXL 2.0 规范还支持单级交换以实现扇出以及在多个虚拟层次结构中汇聚设备的能力,包括对内存设备的多域支持. 上图演示了通过单级交换实现的内存和加速器分离,除了扇出之外,还跨多个虚拟层次结构,每个层次结构用唯一颜色表示。CXL 2.0 规范还允许将这些资源(内存或加速器)从一个域下线并上线到另一个域,从而根据资源需求在不同虚拟层次结构之间进行时间复用.

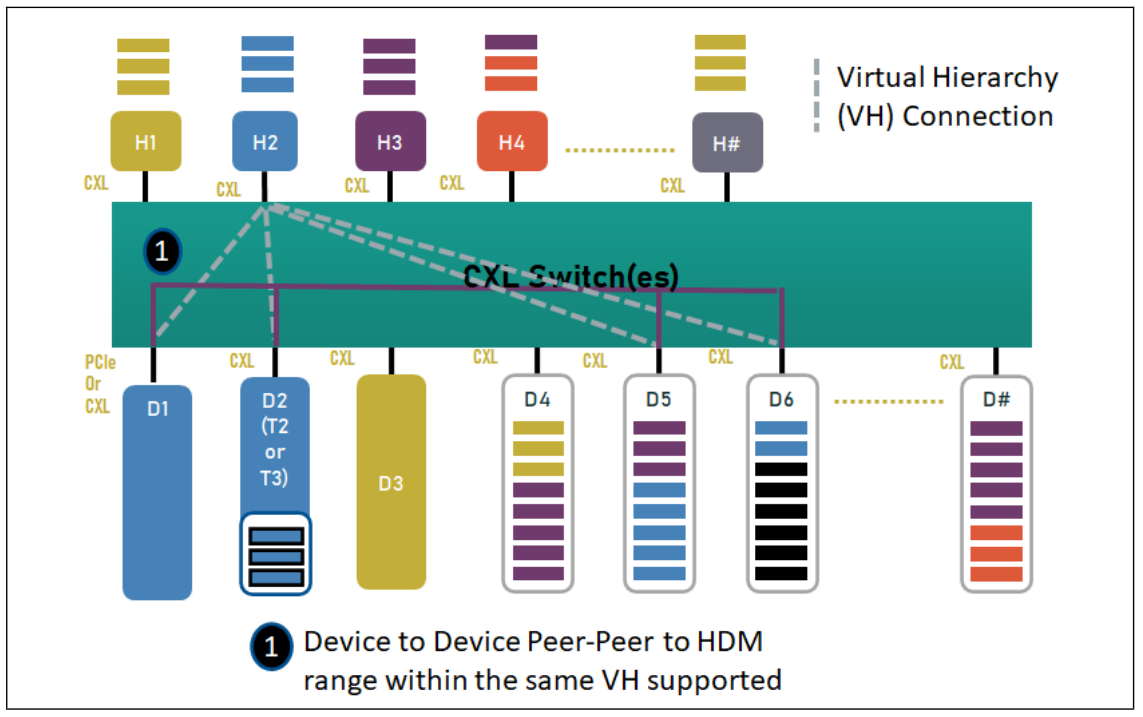

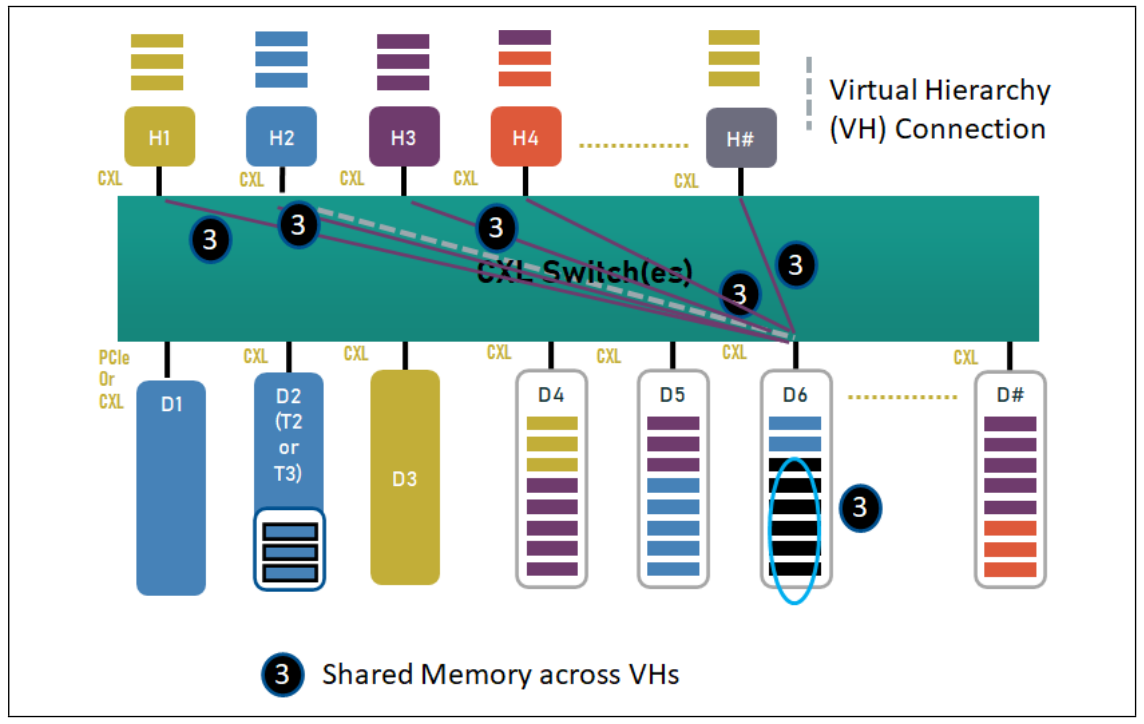

CXL3.0: CXL 3.0 规范在使带宽增加一倍的同时,支持超越 CXL 2.0 规范的其他使用模型。CXL 3.0 规范完全向后兼容 CXL 2.0 规范(因此也兼容 CXL 1.1 和 CXL 1.0 规范)。最大数据速率通过 PAM-4 信号增加到 64.0 GT/s,利用 PCIe 基础规范 PHY 及其 CRC 和 FEC,使带宽翻倍,并提供可选的 Flit 安排以实现低延迟。CXL 3.0 规范启用了多级交换,支持多达 4K 端口,使 CXL 发展为一种扩展到机架和数据中心的架构,包括非树形拓扑结构。CXL 3.0 规范使设备能够使用 UIO(除了之前存在的 MMIO 内存外)直接对 HDM 内存进行点对点访问,以在大规模上提供性能.

类型 2 和类型 3 设备可以实现 Snoop Filter 支持,以使用 CXL.mem 中引入的回退失效通道进行直接点对点访问。提供跨多个虚拟层次结构的共享内存支持,以实现跨多个虚拟层次结构的协同处理. CXL 协议兼容 PCIe CEM 外形规格(4.0 及更高版本)、所有与 EDSFF SSF-TA-1009(2.0 及更高版本)相关的外形规格以及支持 PCIe 的其他外形规格.

CXL Transaction Layer

Flex Bus

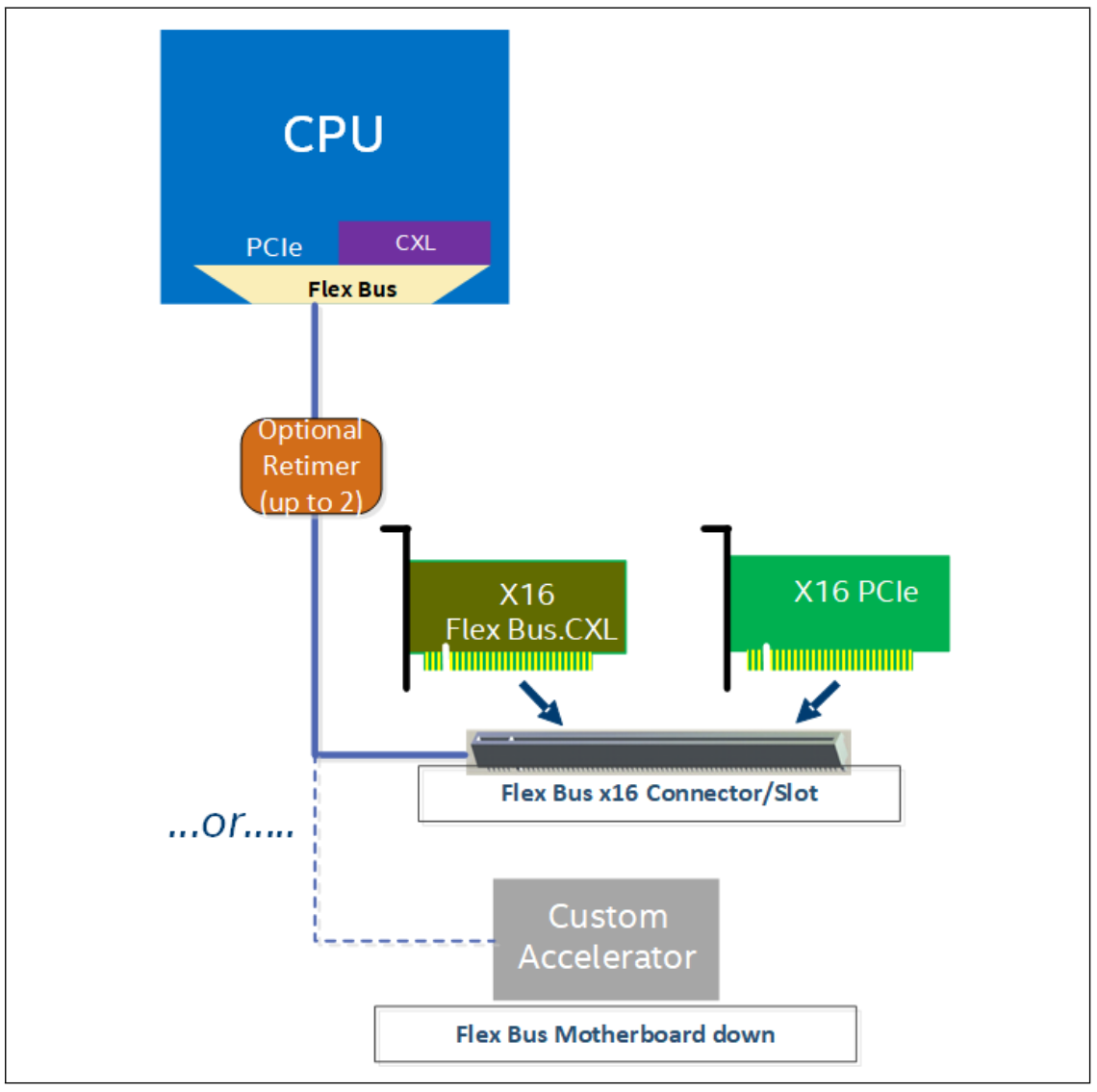

Flex Bus 端口允许设计在通过高带宽、封装外链接提供本地 PCIe 协议或 CXL 之间进行选择. 选择在链路训练期间通过替代协议协商进行,并取决于插入插槽的设备。Flex Bus 使用 PCIe 电气规范,使其与 PCIe 重定时器和支持 PCIe 的外形规格兼容。上图提供了 Flex Bus 端口实现的高层次示意图,展示了插槽实现和设备焊接在主板上的定制实现。插槽实现可以容纳 Flex Bus.CXL 卡或 PCIe 卡. 可以在 CPU 和设备之间插入一个或两个可选的重定时器以延长通道长度

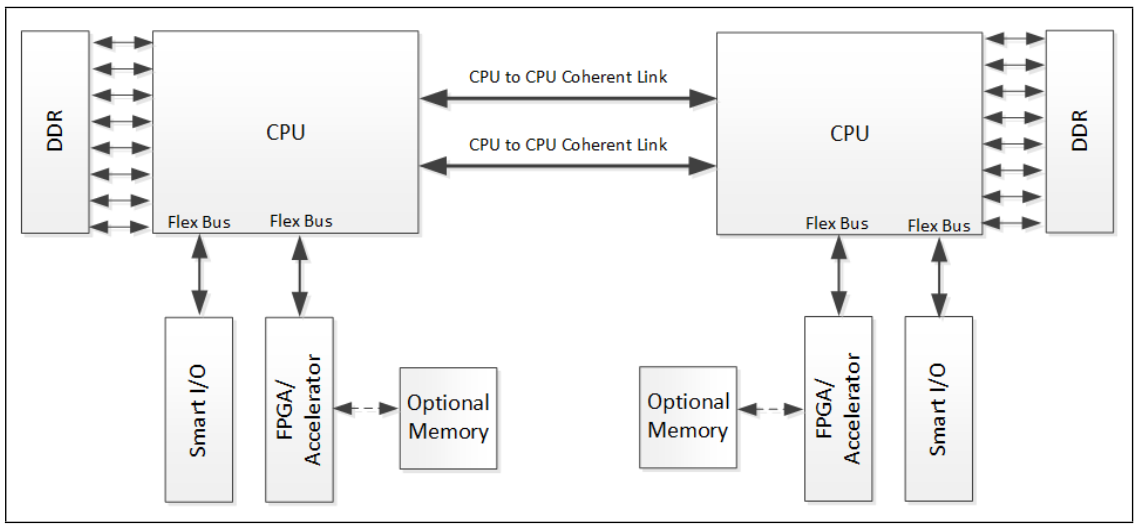

上图展示灵活的端口可以用于将一致性加速器或智能 I/O 连接到主处理器.

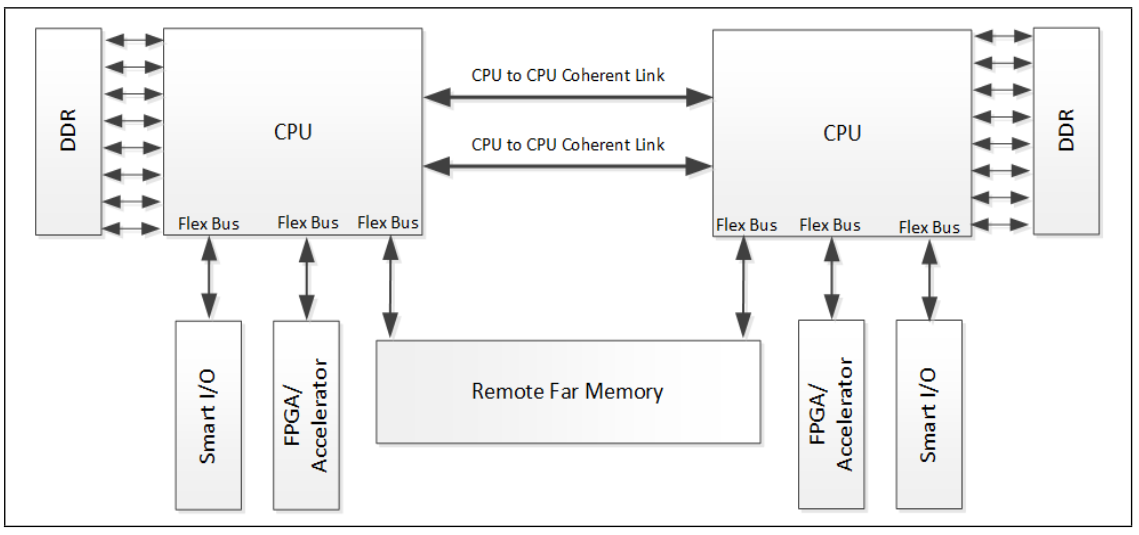

上图说明了如何将 Flex Bus.CXL 端口用作内存扩展端口.

上图展示在 CXL 下游端口下支持的连接.

Flex Bus Link Features

Flex Bus 提供了一种点对点互连,可以传输本地 PCIe 协议或动态多协议 CXL,以通过 PCIe 电气规范提供 I/O、缓存和内存协议。主要的链路属性包括支持以下特性:

- 本地 PCIe 模式,支持 PCIe 基础规范中定义的所有功能

- CXL 模式,按照本规范定义

- PCIe 与 CXL 协议模式的配置

- 在 CXL 模式下,使用 PAM4 信号速率为 64 GT/s,并且降级速率为 32 GT/s、16 GT/s 或 8 GT/s。否则,在 CXL 模式下信号速率为 32 GT/s,降级速率为 16 GT/s 或 8 GT/s

- 在 CXL 模式下,链路宽度支持 x16、x8、x4、x2(降级模式)和 x1(降级模式)

- 在 CXL 模式下支持分岔(又称链路细分)到 x4

Flex Bus Layer

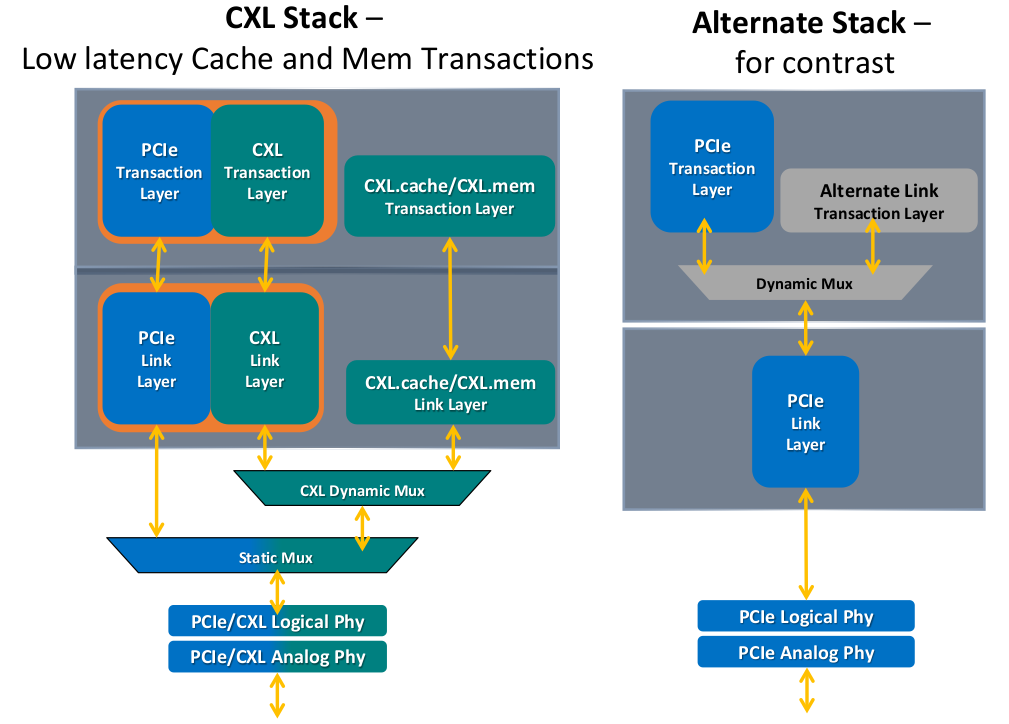

Flex Bus 架构组织为多个层次,如图上图. CXL 事务(协议)层细分为处理 CXL.io 的逻辑和处理 CXL.cache 与 CXL.mem 的逻辑. CXL 链路层也以相同的方式细分。CXL.cache 和 CXL.mem 的逻辑在事务层和链路层内是结合在一起的. CXL 链路层与 CXL ARB/MUX 接口,后者将来自两个逻辑流的流量交错。此外 PCIe 事务层和数据链路层是可选实现的,如果实现,允许分别与 CXL.io 事务层和链路层融合. 由于链路训练过程,事务层和链路层被配置为运行在 PCIe 模式或 CXL 模式。虽然主机 CPU 很可能实现这两种模式,但加速器 AIC 允许只实现 CXL 模式。Flex Bus 物理层的逻辑子块是一个融合的逻辑物理层,可以在 PCIe 模式或 CXL 模式下运行,具体取决于链路训练期间的替代模式协商结果.