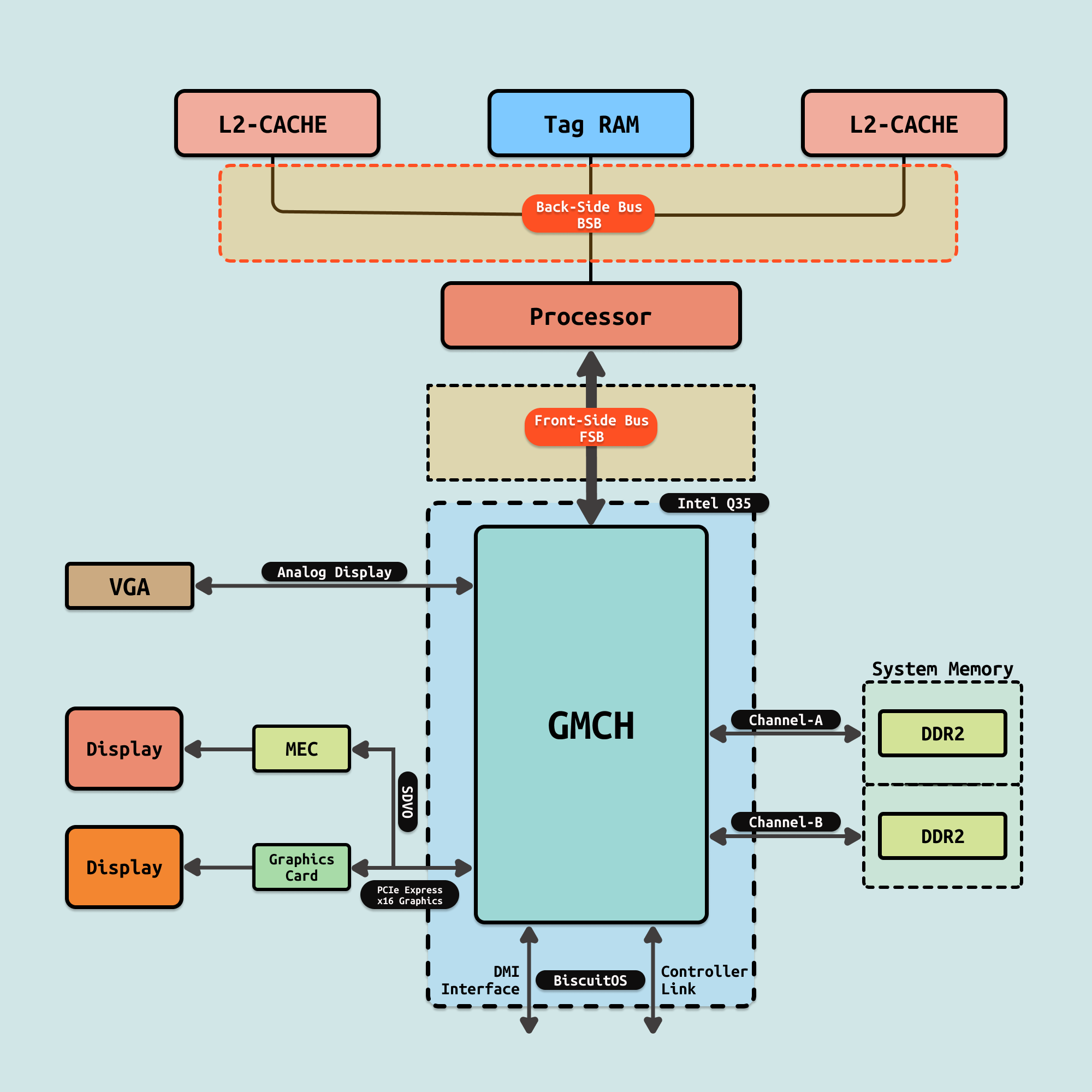

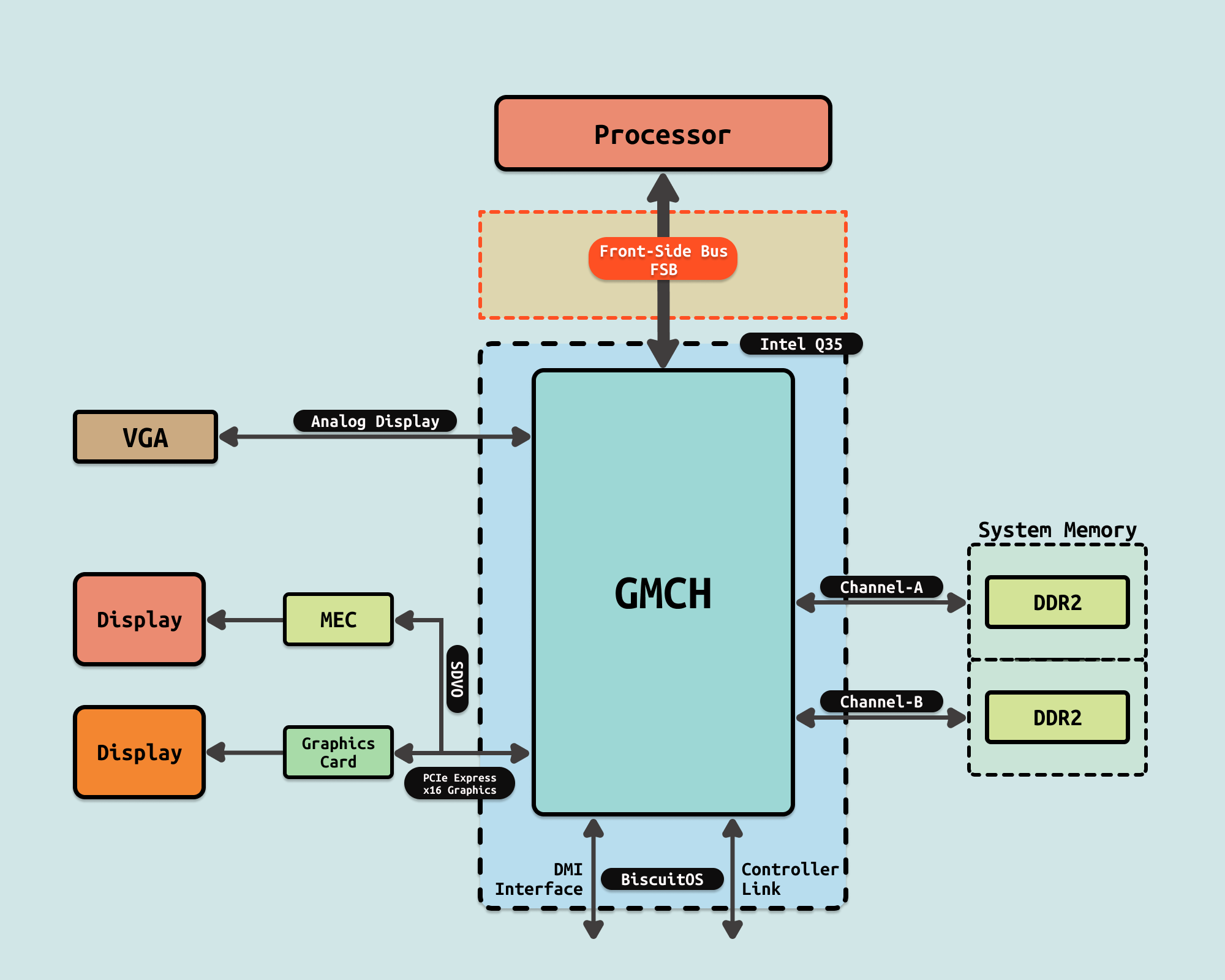

前端总线(FSB,Front Side Bus) 是计算机 CPU 和北桥芯片之间的主通信通道(内存控制器位于北桥芯片)。FSB 这个术语最初由英特尔公司在 1990 年代使用,大约是 Pentium Pro 和 Pentium II 产品发布的时候. “前端”指的是处理器到计算机系统其余部分的外部接口,与“后端”相对,后端通过后端总线连接缓存(以及可能的其他CPU). 前端总线(FSB)主要用于与个人电脑和服务器相关的主板上。它们很少在嵌入式系统或类似的小型计算机中使用。FSB 设计比前几十年单一系统总线的设计有性能提升,但这些前端总线有时也被称为“系统总线(System Bus)”.

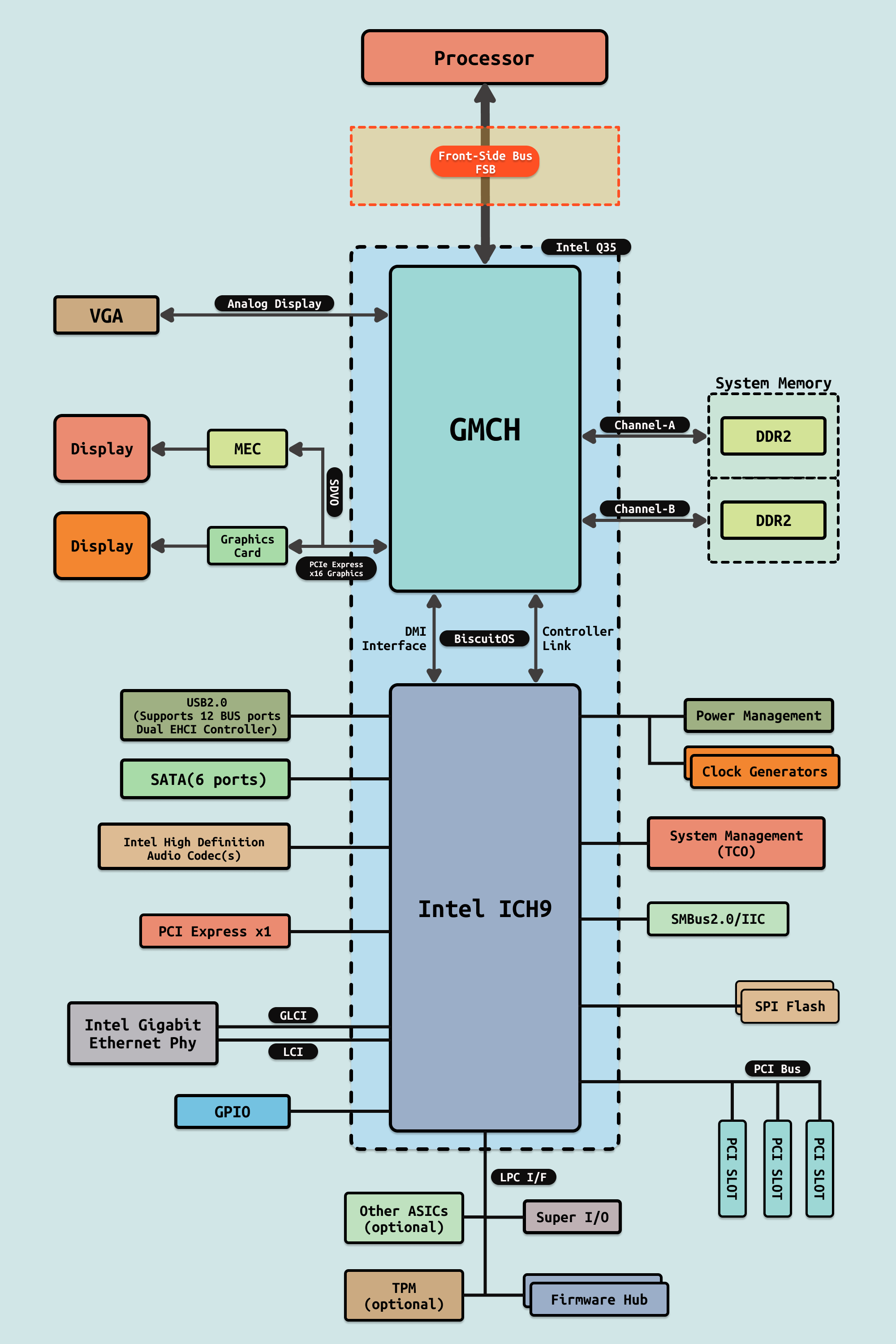

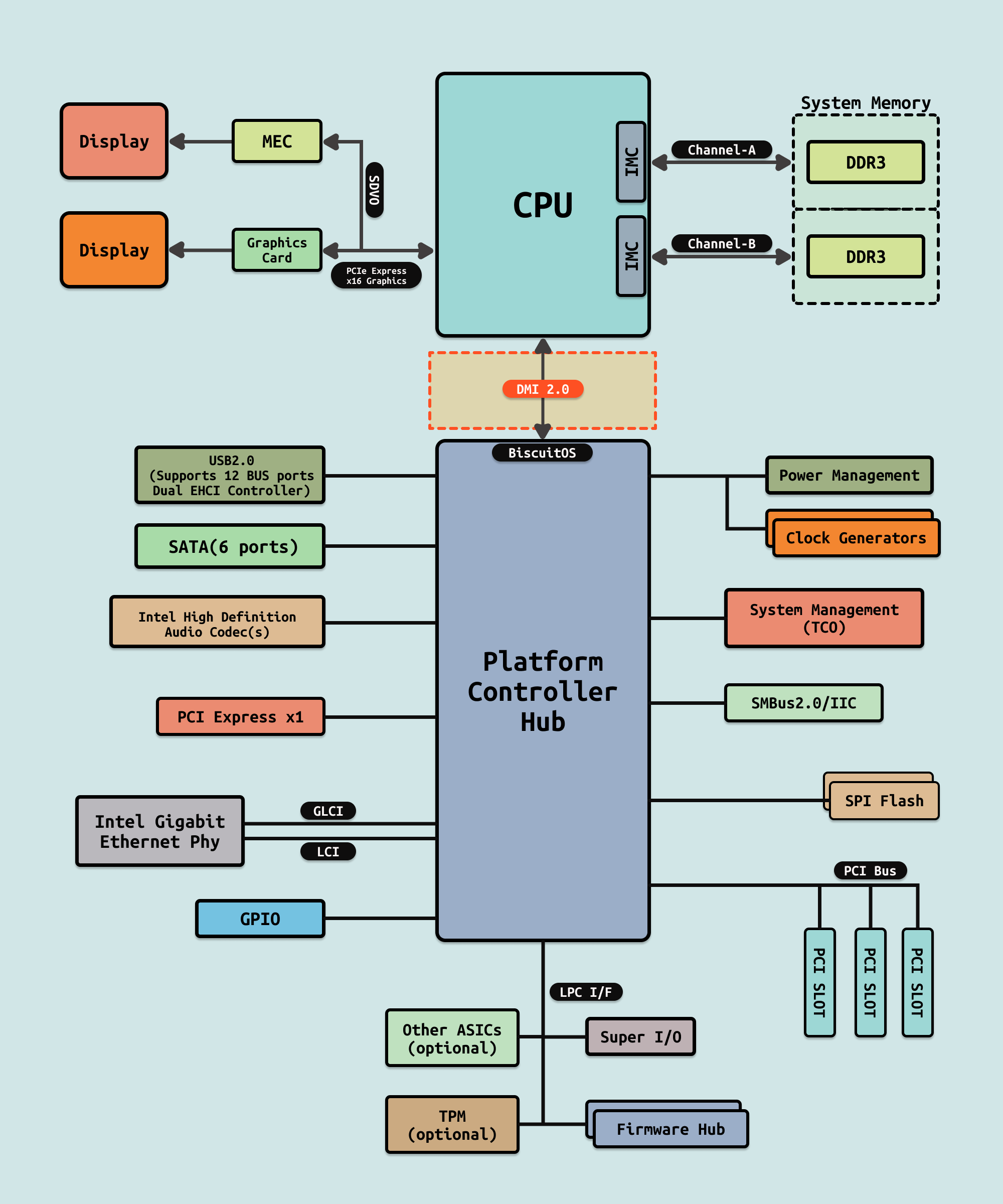

前端总线通常通过一个芯片组连接 CPU 和其他硬件,Intel 实现了一个北桥和南桥。其他总线,如外围组件互连(PCI)、加速图形端口(AGP)和内存总线,都连接到芯片组上,以便数据在连接的设备之间流动。这些次级系统总线通常以从前端总线时钟衍生的速度运行,但不一定与之同步. Intel 在 1990 年代中期推出 Pentium 处理器时开始使用 FSB. 这标志了 CPU 与主内存之间通信方式的一次重大变革,FSB 成为连接 CPU(通过其外部接口)与系统的其余部分(主要是内存控制器,即北桥)的专用通道. Intel 主要采用 FSB 的系列:

- Pentium 系列:

- Pentium: 自 1993 年开始,Pentium 系列的早期版本就使用了FSB

- Pentium Pro: 这是 Intel 首款采用 FSB 的处理器之一,于 1995 年推出

- Pentium II、III 和 IV: 这些后续的 Pentium 系列处理器均使用了 FSB,其中 Pentium IV 特别依赖高速 FSB 以提升性能

- Celeron 系列: 早期的 Celeron 处理器也采用了与同期 Pentium 处理器相同的 FSB 技术,包括基于 Pentium II 和 III 的设计

- Core 系列:

- Core 2 Duo 和 Core 2 Quad: 这些是 Intel Core 系列中广泛采用 FSB 的处理器。Core 2 Duo 在 2006 年推出,提供了较高的 FSB 速率,支持更好的性能表现

- 第一代 Core i3、i5 和 i7(Nehalem 架构之前): 虽然 Nehalem 架构开始引入新的 QPI 和 DMI 总线技术,但在此之前的 Core i 系列的某些型号仍使用FSB

- Xeon 系列: 早期的 Xeon 处理器,尤其是 NetBurst 架构(与Pentium 4 相同)和 Core 架构的处理器,依赖 FSB 进行处理器与内存控制器之间的通信

- Intel Atom: 初代 Intel Atom 处理器在低功耗市场中也采用了 FSB 技术

相关组件速度

处理器(CPU)的运行频率有时是通过将前端总线(FSB)速度乘以一个时钟倍频器来确定的。例如一个运行在 3200 MHz 的处理器可能使用的是 400 MHz 的 FSB. 这意味着有一个内部时钟倍频设置(也称为总线/核心比率)为 8. 即 CPU 设置为以前端总线频率的 8 倍运行: 400 MHz × 8 = 3200 MHz。通过改变 FSB 频率或 CPU 倍频器,可以达到不同的 CPU 速度,这种做法被称为超频(Overclocking)或降频(Underclocking).

内存

设置 FSB 速度直接关系到系统必须使用的内存速度等级. 内存总线连接北桥和 RAM,就像前端总线连接 CPU 和北桥一样。通常这两个总线必须以相同的频率运行. 在大多数情况下,将 FSB 提高到 450 MHz 也意味着让内存以 450 MHz 运行. 在较新的系统中,可以看到 “4:5” 之类的内存比率. 在这种情况下,内存的运行速度将是 FSB 的 5/4 倍,意味着 400 MHz 的总线可以使内存以 500 MHz 运行. 这通常被称为异步系统. 由于 CPU 和系统架构的差异,不同的 FSB 至内存比率可能会以意想不到的方式影响整体系统性能.

在图像、音频、视频、游戏、FPGA 合成和执行少量工作的科学应用中,如果要处理大量数据集的每一个元素,FSB 速度成为一个主要的性能问题. 一个慢的 FSB 将导致 CPU 花费大量时间等待数据从系统内存到达. 然而如果涉及每个元素的计算更复杂,处理器将花费更长时间进行这些计算. 因此,FSB 将能够跟上, 因为访问内存的速率减少了.

外围总线

与内存总线类似, PCI 和 AGP 总线也可以与前端总线异步运行。在旧系统中,这些总线以前端总线频率的一定比例运行, 这个比例由 BIOS 设置. 在较新的系统中,PCI、AGP 和 PCI Express 外围总线通常接收它们自己的时钟信号,这消除了它们对前端总线的时序依赖.

超频

超频是一种通过操纵组件设置运行的频率,并在必要时修改发送到组件的电压以使其能够在这些更高频率下更稳定运行,从而使计算机组件超出其标准性能水平的做法. 许多主板允许用户通过更改跳线或 BIOS 设置来手动设置时钟倍频器和 FSB 设置. 几乎所有 CPU 制造商现在都在芯片中“锁定”了一个预设的倍频器设置。一些被锁定的 CPU 是可以解锁的. 例如一些 AMD Athlon 处理器可以通过在 CPU 表面连接电接点来解锁。AMD 和 Intel 的一些其他处理器出厂时未锁定,并被终端用户和零售商标记为发烧友级处理器,因为具备这一特性。对于所有处理器,提高 FSB 速度可以通过减少 CPU 与北桥之间的延迟来提升处理速度.

这种做法将组件推向超出其规格的极限,可能导致行为异常、过热或提前失效。即使计算机看起来正常运行,在重负载下也可能出现问题。从零售商或制造商(如惠普或戴尔)购买的大多数 PC 不允许用户更改倍频器或 FSB 设置,因为可能会导致行为异常或失败。单独购买用于构建自定义机器的主板更有可能允许用户在 PC 的 BIOS 中编辑倍频器和 FSB 设置.

FSB 演变路线

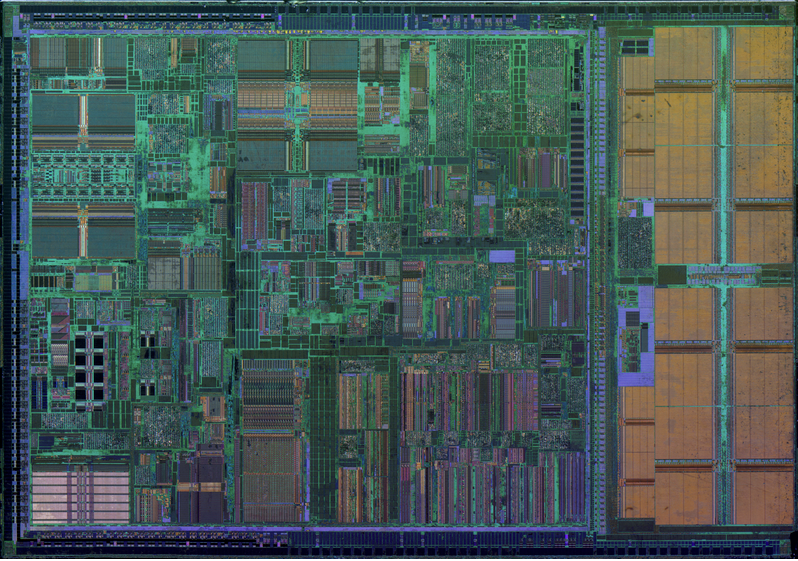

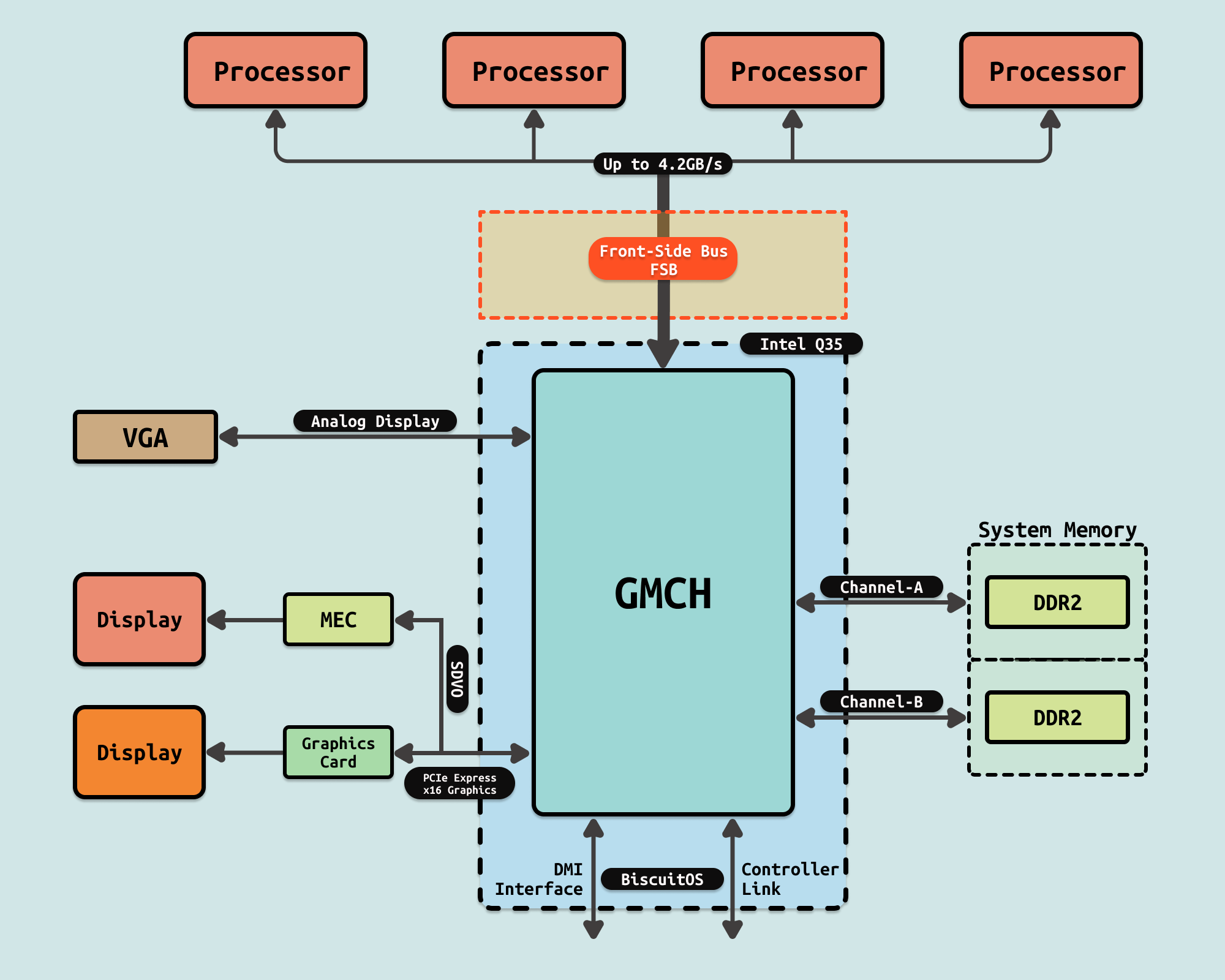

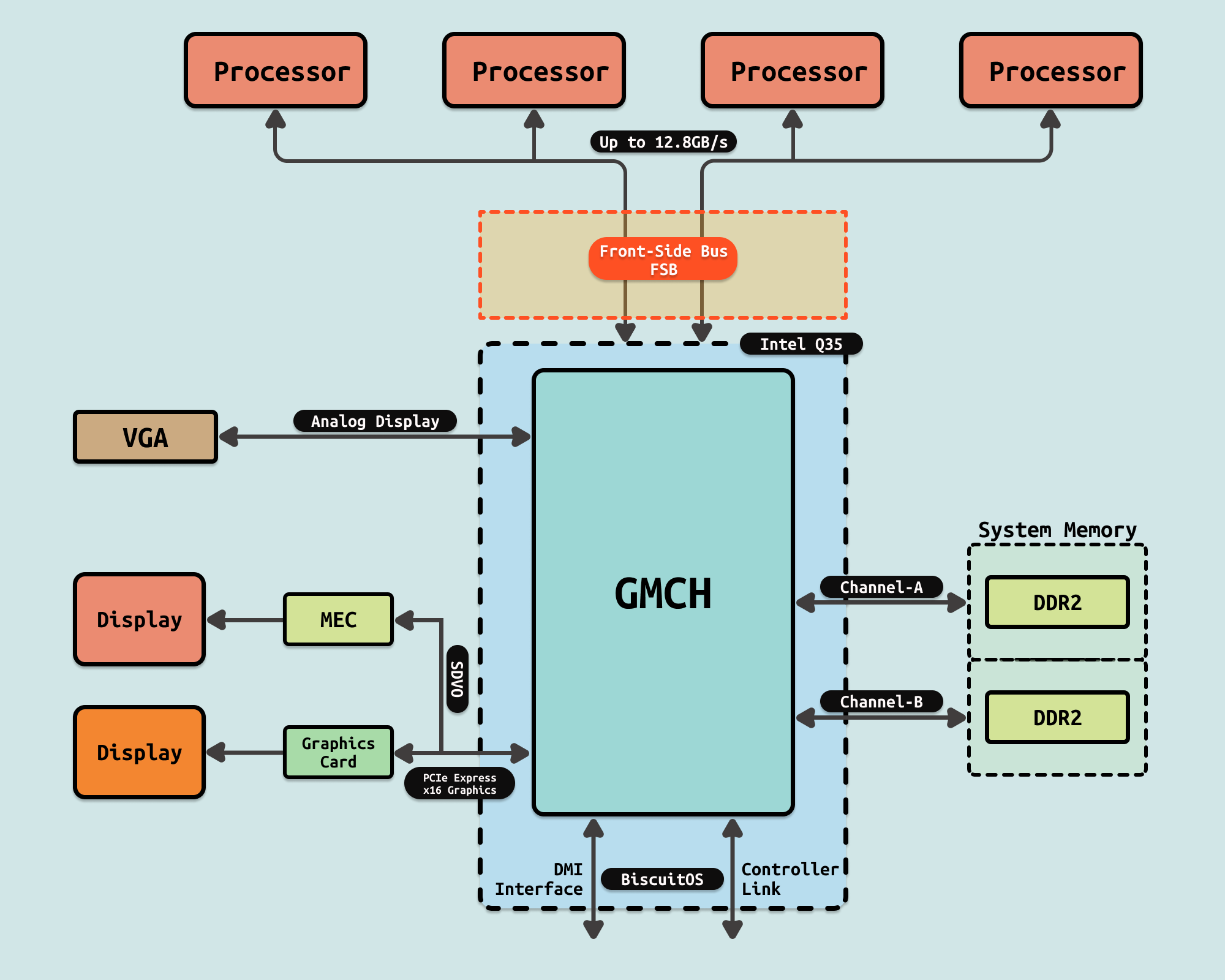

前端总线在最初设计时具有高灵活性和低成本的优势. 简单的对称多处理器将多个 CPU 放置在共享的 FSB 上,尽管由于带宽瓶颈,性能无法线性扩展. 前端总线一直被所有 Intel Atom、Celeron、Pentium、Core 2 和 Xeon 处理器型号使用,直到大约 2008 年. 最初这个总线是 CPU 和所有系统设备的中心连接点. 如果 CPU 不能像执行它们那样快速地获取指令和数据,那么更快的 CPU 潜力就被浪费了。CPU 在等待在主内存中读取或写入数据时可能会花费大量空闲时间,因此高性能处理器需要高带宽和低延迟访问内存。AMD 批评前端总线是一种旧的且缓慢的技术,限制了系统性能.

在较旧的共享 FSB 总线(Shared Front-Side Bus)系统中,所有流量都通过单个共享双向 FSB 总线发送. FSB 宽总线(Intel® Xeon® 处理器为 64 位, Intel® Itanium® 处理器为 128 位) 一次可接收多个数据字节. 这种方法的挑战是随着宽源同步总线频率的增加而遇到的电气限制.为了解决这个问题,英特尔通过一系列技术改进改进了总线. 最初在 20 世纪 90 年代末,数据以 2 倍总线时钟输入,也称为 double-pumped. 如今的 Intel® Xeon® 处理器 FSB 是 quad-pumped,以 4 倍总线时钟输入数据。如今 FSB 上的最高理论数据速率为 1.6 GT/s.

为了进一步增加基于 FSB 总线的平台的带宽,单共享总线方法演变为双独立总线(Dual Independent Buses: DIB). DIB 设计实质上使可用带宽翻倍。但是,所有监听流量都必须在两条总线上广播,如果不加以控制,将减少有效带宽。为了最大限度地减少此问题,在芯片组中采用了监听过滤器来缓存监听信息,从而大大减少了带宽负载.

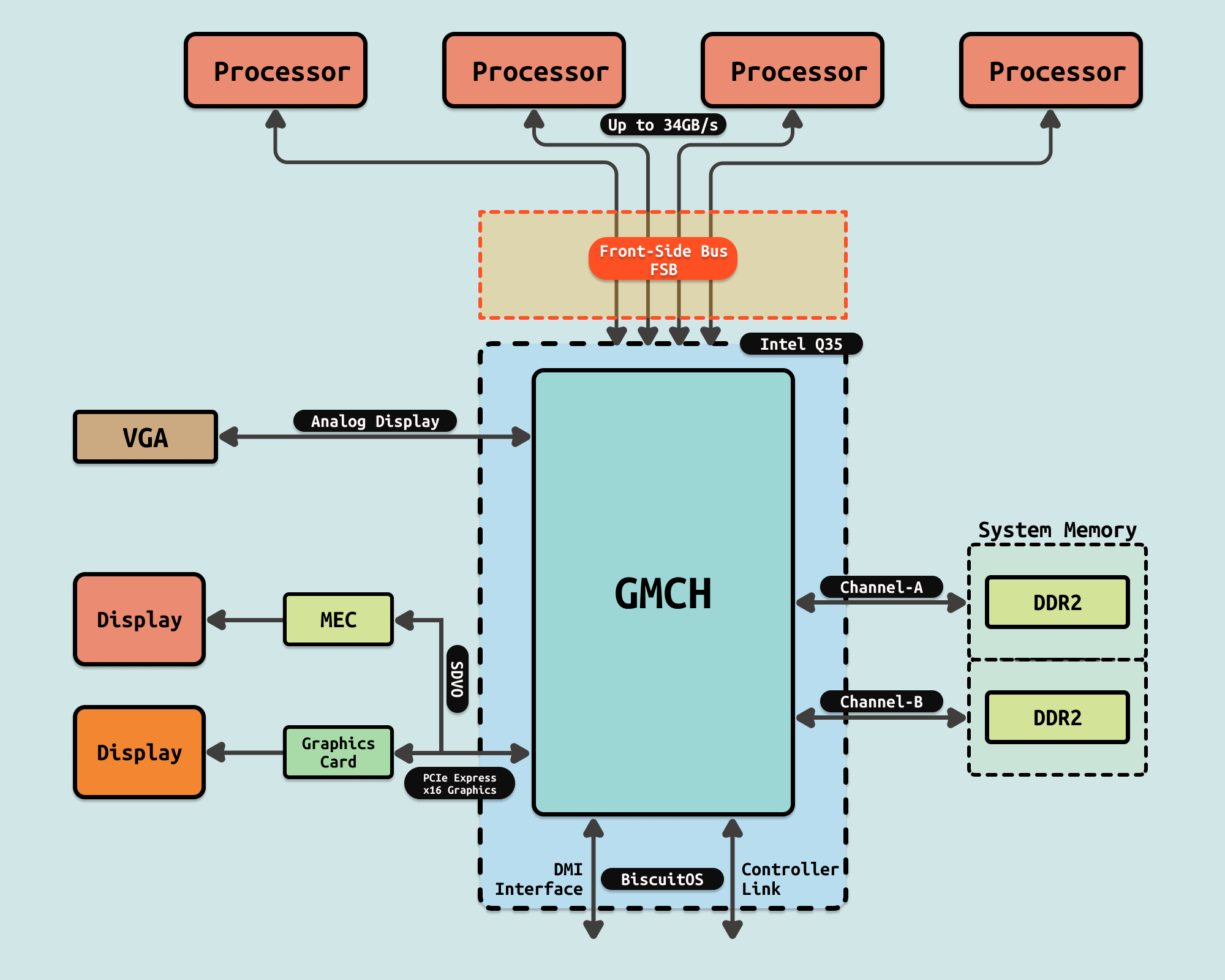

随着专用高速互连(Dedicated High-Speed Interconnects:DHSI) 的引入,DIB 方法得到了进一步的扩展. 基于 DHSI 的平台使用四个 FSB,平台中的每个处理器各一个. 同样还采用了监听过滤器来实现带宽扩展

更现代的设计使用点对点和串行连接,如 AMD 的 HyperTransport 和 Intel 的 DMI 2.0 或 QuickPath Interconnect(QPI). 这些实现取消了传统的北桥,支持 CPU 直接链接到平台控制中心、南桥或 I/O 控制器. 在传统架构中,前端总线作为 CPU 与系统中所有其他设备(包括主内存)之间的直接数据链接. 在基于 HyperTransport 和 QPI 的系统中,系统内存通过集成在 CPU 中的内存控制器独立访问,HyperTransport 或 QPI 链路的带宽用于其他用途. 这增加了 CPU 设计的复杂性,但提供了更大的吞吐量以及在多处理器系统中更好的扩展性.

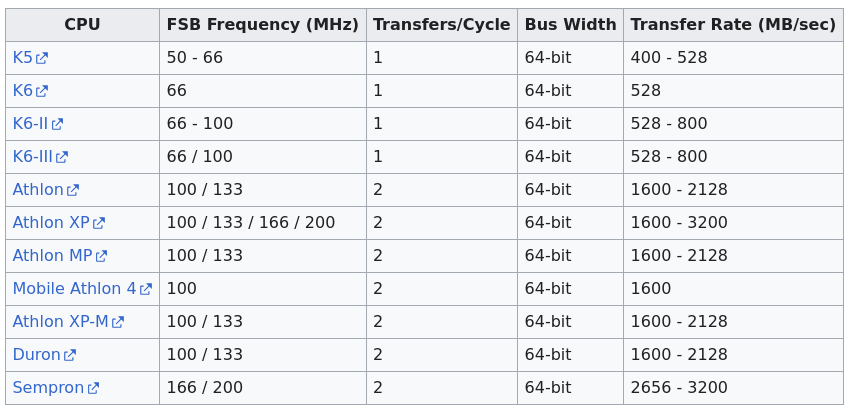

FSB 传输率

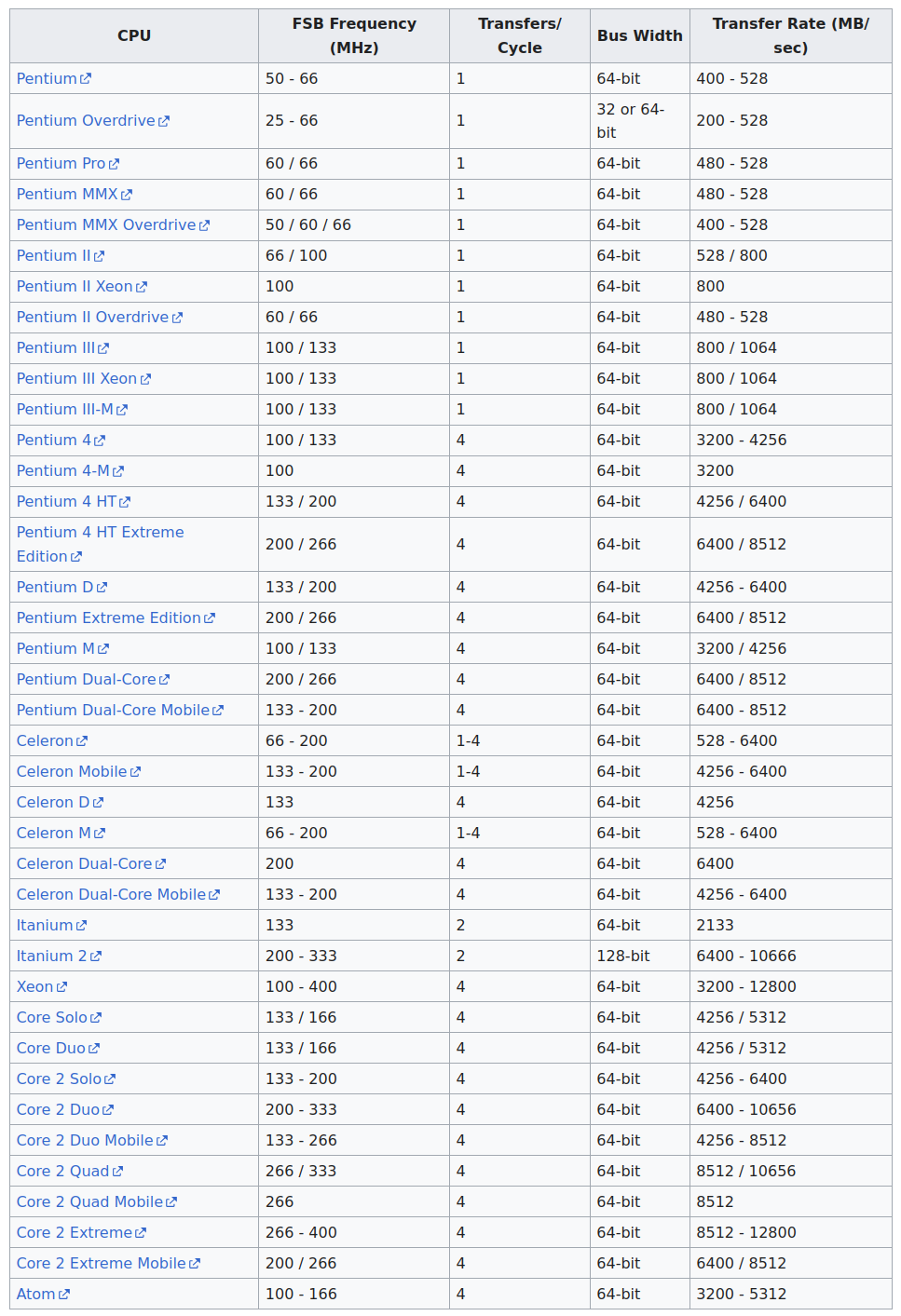

前端总线的带宽或最大理论吞吐量由其数据路径的宽度、时钟频率(每秒周期数)以及每个时钟周期执行的数据传输次数的乘积决定. 例如一个 64 位(8 字节)宽的 FSB,以 100 MHz 的频率运行,每周期执行 4 次传输,其带宽为 3200 兆字节每秒(MB/s):

8 字节/传输 × 100 MHz × 4 传输/周期 = 3200 MB/s每个时钟周期的传输次数取决于使用的技术。例如,GTL+ 每周期执行 1 次传输,EV6 2 次传输/周期,AGTL+ 4 次传输/周期。Intel 将每周期四次传输的技术称为四倍泵送. 许多制造商发布前端总线的频率为 MHz,但经销商经常列出理论有效信号速率(通常称为每秒兆次传输或 MT/s). 例如如果主板(或处理器)的总线设置为 200 MHz 并且每个时钟周期执行 4 次传输,则 FSB 被评定为 800 MT/s. 下面列出了几代流行处理器的规格:

Intel

AMD