Intel 的 Mesh 总线是一种高级的处理器互联技术,用于改善多核心处理器内部的数据传输效率. 这种技术首次出现在 Intel 的 Xeon Scalable 处理器(代号为 Skylake-SP)上,并继续用于后续的一些处理器系列. Mesh 总线替代了之前的环形总线(Ring Bus)架构,旨在提供更高的可扩展性和更低的延迟,特别是在拥有大量核心的处理器上. Mesh 总线的特点和工作原理:

- 结构: Mesh 总线将处理器的核心、缓存、内存控制器等组件通过一个二维网状结构相连. 这种网状布局允许多个数据路径同时激活,从而增加带宽和减少瓶颈.

- 数据传输: 在 Mesh 结构中,数据可以直接从一个组件传输到相邻的组件,或者通过多个跳点(hop)跨越更远的距离. 这种布局优化了数据流,减少了跨大距离传输时的延迟.

- 可扩展性: 与环形总线相比,Mesh 架构更容易扩展到更多的核心和组件,因为它不依赖于单一的数据通道. 这使得它特别适用于服务器和高性能计算环境,这些环境通常需要大量的处理核心和快速的数据处理能力.

- 功效管理: Mesh 架构允许更细粒度的功效控制. 例如不活跃的部分网格可以降低频率或电压,以节省能源,而不影响整体性能.

- 故障容忍: 网状布局的一个优势是,即使某一部分发生故障,数据通常也可以通过其他路径重新路由,从而增强了系统的整体可靠性和故障容忍性.

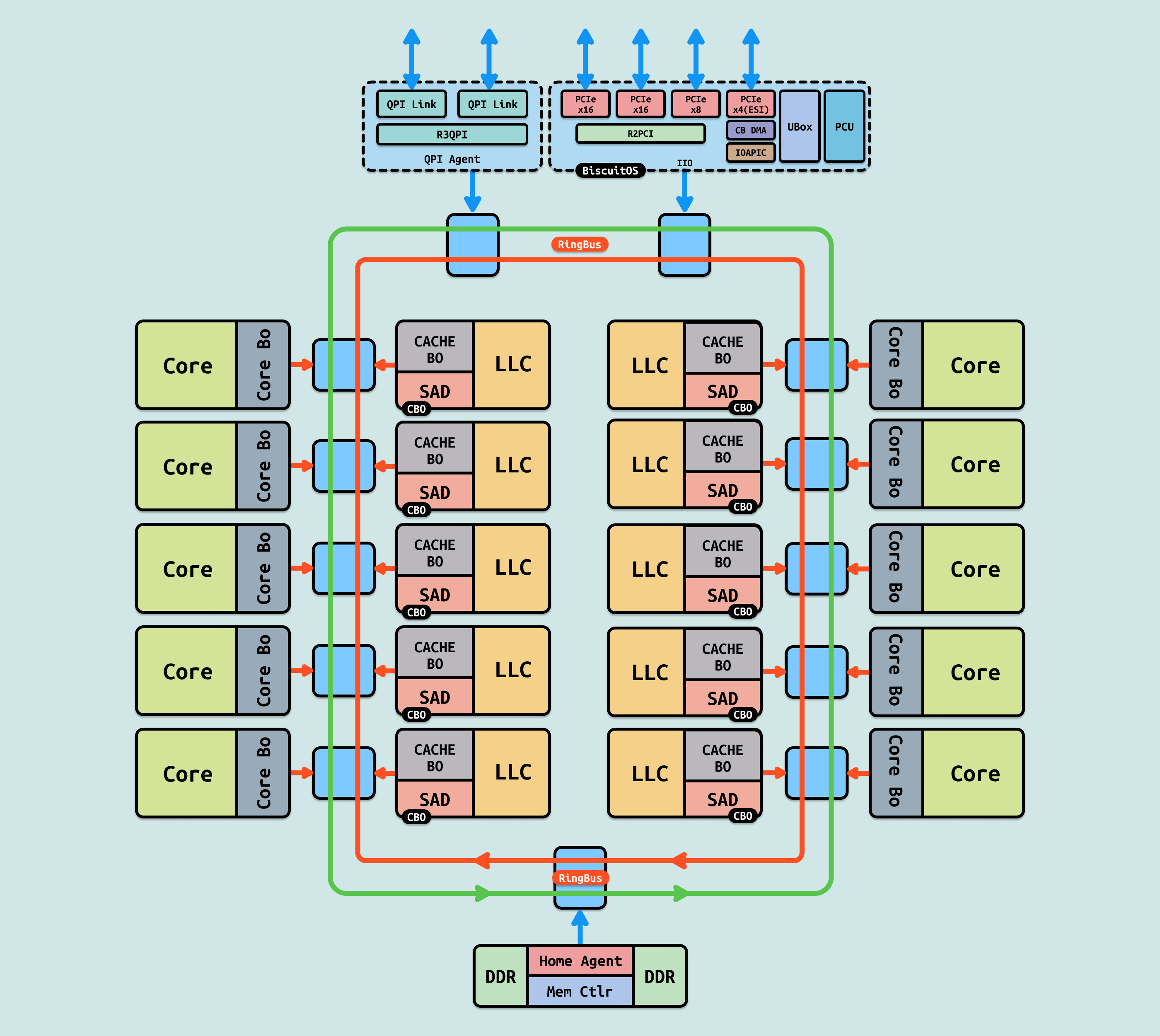

自 2000 年代末期以来,Intel 为了高效地连接多个物理核心,采用了环形互连架构. 随着 2010 年代 Intel 高端模型上核心数量的持续增加,环形架构在带宽和延迟方面遇到了相当严重的扩展问题. 为了显著缓解这些瓶颈,Intel 引入了新的网格互连架构,该架构采用了网状网络拓扑结构,以减少节点之间的延迟并增加带宽.

Intel 长期以来一直在其研究项目中试验网格拓扑. 例如 2007 年的 80 核多核心 Polaris 处理器采用了网格互连架构,每个 Tile 上都有一个 5 口路由器. Polaris 是 teraFLOP 计算领域的第一个研究芯片,最终导致了商用处理器 Xeon Phi 系列的诞生. 2016 年 6 月,Intel 发布了基于 Knights Landing 的新 Xeon Phi MIC 微处理器,这是 Intel 首个商用化实施新互连架构的微架构. 2017 年中,Intel 推出了采用网格互连的 Skylake 服务器微架构. 这种微架构用于他们的服务器(Xeon Scalable)微处理器以及 Core i7 和 Core i9 的高端桌面平台部件.

Intel 的网格互连架构包含了许多相关的概念:

- Mesh: 这种结构是一个由半环形成的二维数组,形成了一个系统级的互连网格(Grid).

- Tile: 一种可以在大型网格上多次复制的模块化 IP 块

- Core Tile: 一种特定类型的 Tile,内含一个 Intel 的 x86 核心

- IMC Tile: 一种特定类型的 Tile,内含一个集成内存控制器

- Caching/Home Agent(CHA): 位于 Core Tile 内部的单元,负责维持 Tile 之间的缓存一致性. CHA 还与 CMS 界面相连

- Coverged/Common(CMS): 一个网格站点,便于 Tile 与结构之间的接口

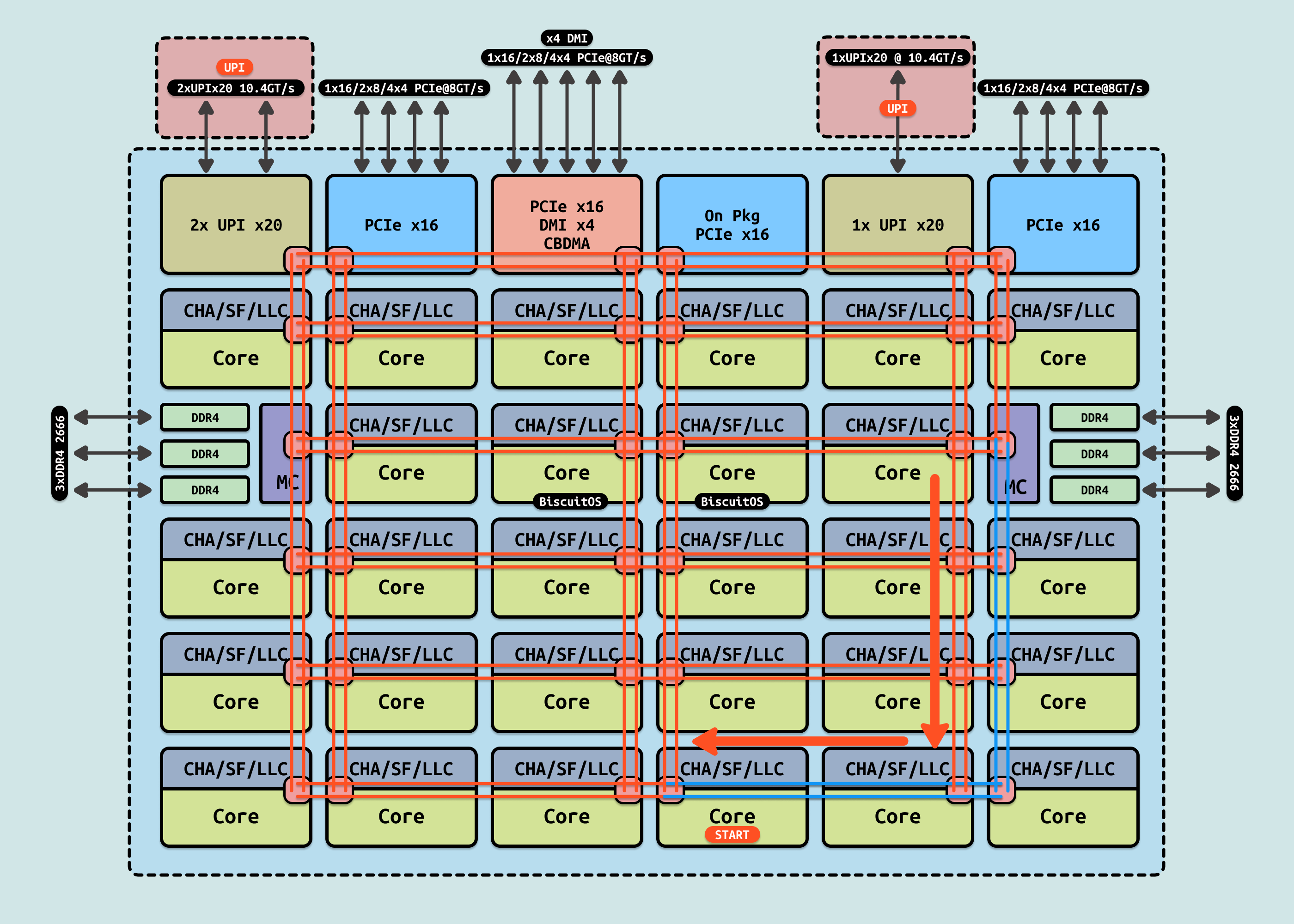

Tile 可以在 X 轴和 Y 轴上根据需要重复多次. Tile 的类型取决于设计目标和目标市场. 理论上任何类型的 IP 块都可以作为 Tile,只要它被修改以与 CMS 接口相连. 每个瓦片都有自己的 CMS,这使得瓦片可以与网格接口相连. 每个瓦片上的每个网格停靠点都直接连接到它的四个直接邻居: North、South、East、West. Mesh 本身由一个二维数组的半环组成. 每个垂直列的 CMS 形成一个双向半环. 同样,每个水平行也形成一个双向半环。数据包遵循一个简单的路由算法:

- 数据包首先在垂直方向上路由

- 然后在水平方向上路由

数据包起始于一个 Tile (例如来自 CHA)或某个 I/O 外设. 它在本地网格停靠点(CMS)进入结构. 然后数据包沿着垂直半环路由,向北或向南,始终选择最短的路径. 一旦数据包到达其目的行,它将被从垂直半环取下并放置在水平半环上,继续前往目的地瓦片. 一旦数据包到达目的地 Tile,它将通过网格停靠点与 Tile 重新连接.

考虑上面的 5X6 示例网格,为了让数据包从标记为 ‘start’ 的 Tile 传输到 IMC,数据包将通过 CHA 离开核心并通过 CMS 进入网格。然后数据包将向北路由经过三个停靠点. 然后数据包将被从垂直半环取下并放置在水平半环上,在那里它将继续向东移动两个额外的停靠点到达 IMC.

需要注意的是,返回路径可能与之前的路线不同. 例如在这种情况下,来自 IMC 的响应将首先通过垂直半环路由到最东南角的 Tile. 然后数据包将被从垂直半环取下并放置在水平半环上,在那里它将向西移动直到到达目的地 Tile。在英特尔产品系列中,采用 Mesh 网格互连架构的主要是以下几个系列:

- Xeon Phi 处理器(基于 Knights Landing 微架构): 这是第一个采用 Mesh 网格互联架构的产品,专为高性能计算和密集计算任务设计

- Skylake-SP Xeon 处理器: Skylake 服务器版本引入了 Mesh 架构,以替代之前的 Ring Bus 架构,提高了多核处理器之间的数据传输效率和扩展性

- Cannon Lake 及之后的处理器: 继续使用和优化 Mesh 架构,用于服务器和高端桌面平台(High-End Desktop,HEDT),如 Xeon Scalable 和部分 Core i9 系列

- Ice Lake-SP Xeon 处理器: 这一代 Xeon 服务器处理器也使用了 Mesh 架构,提供了更高的性能和更好的能效