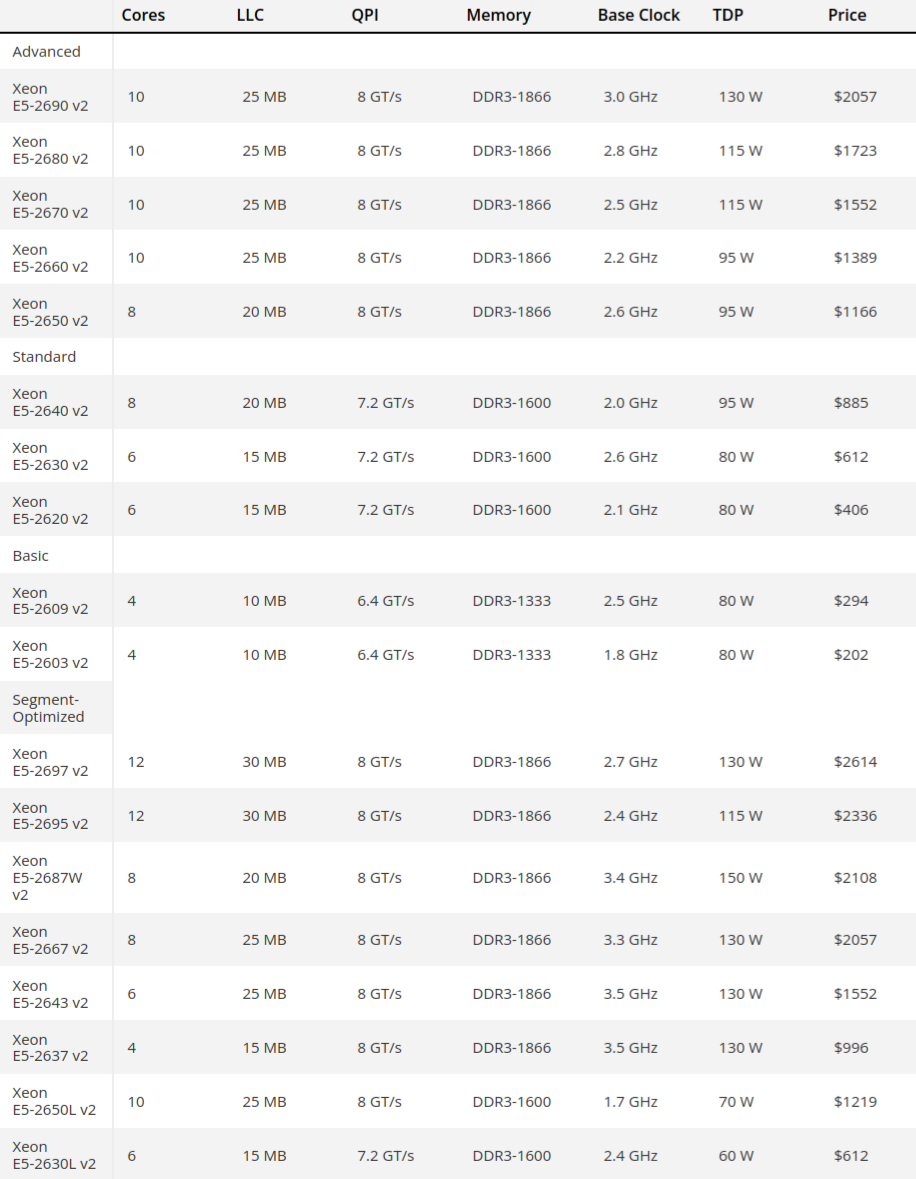

Intel 的 RingBus 架构是一种先进的处理器内部通信技术,用于在处理器的核心、缓存、输入/输出控制器等组件之间传输数据. 这种架构采用环形的数据路径,能够高效地管理多核处理器内部的数据流动. 从上图可以看到,Ring Bus 实际上是两个环,一个顺时针环和一个逆时针环. 各个模块一视同仁的通过 Ring Stop 挂接在 Ring Bus 上. RingBus 架构的主要特点包括:

- 环形连接: RingBus 通过一个环形的总线连接处理器内的多个核心和缓存,允许数据在核心之间迅速流通,从而提高处理效率.

- 多通道传输: 环形总线支持多通道数据同时传输,这样不同的数据包可以在同一时间内在总线上独立传输,减少了等待时间和冲突. 各个模块之间交互方便,不需要 Core 中转, 孕育出一些高级加速技术,如 DCA(Direct Cache Access), Crystal Beach 等

- 缩短延时: 由于数据不需要通过中心控制器即可直接在核心之间传递,这降低了通信延时,提高了响应速度, 双环设计可以保证任何两个 Ring stop 之间距离不超过 Ring Stop 总数的一半,延迟较低. 高速的 Ring bus 保证了性能的极大提高. Core to Core latency 只有 60ns 左右,而带宽则高达数百G(Nehalem 192GB/s)

- 可扩展性: 尽管 RingBus 本身在扩展到非常高的核心数时会遇到挑战,但它比传统的总线架构(如前端总线 FSB) 提供了更好的扩展性. 增加一个 Core,只要在 Ring 上面加个新的 Ring stop 就好,不用像以前一样考虑复杂的互联问题

- 负载平衡: RingBus 允许数据根据需求动态地在环形路径上流动,从而更有效地分配处理器资源,提高整体系统性能

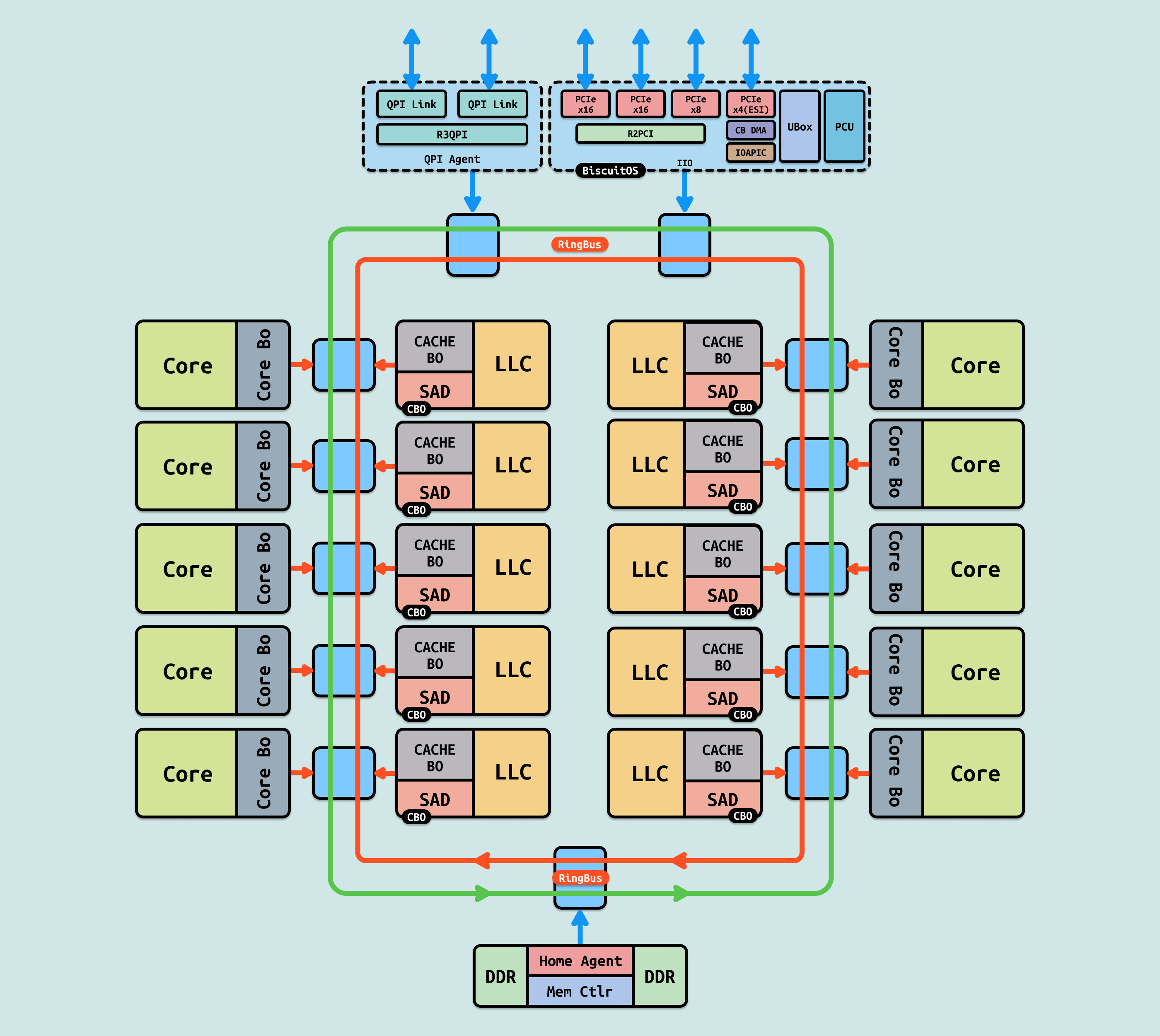

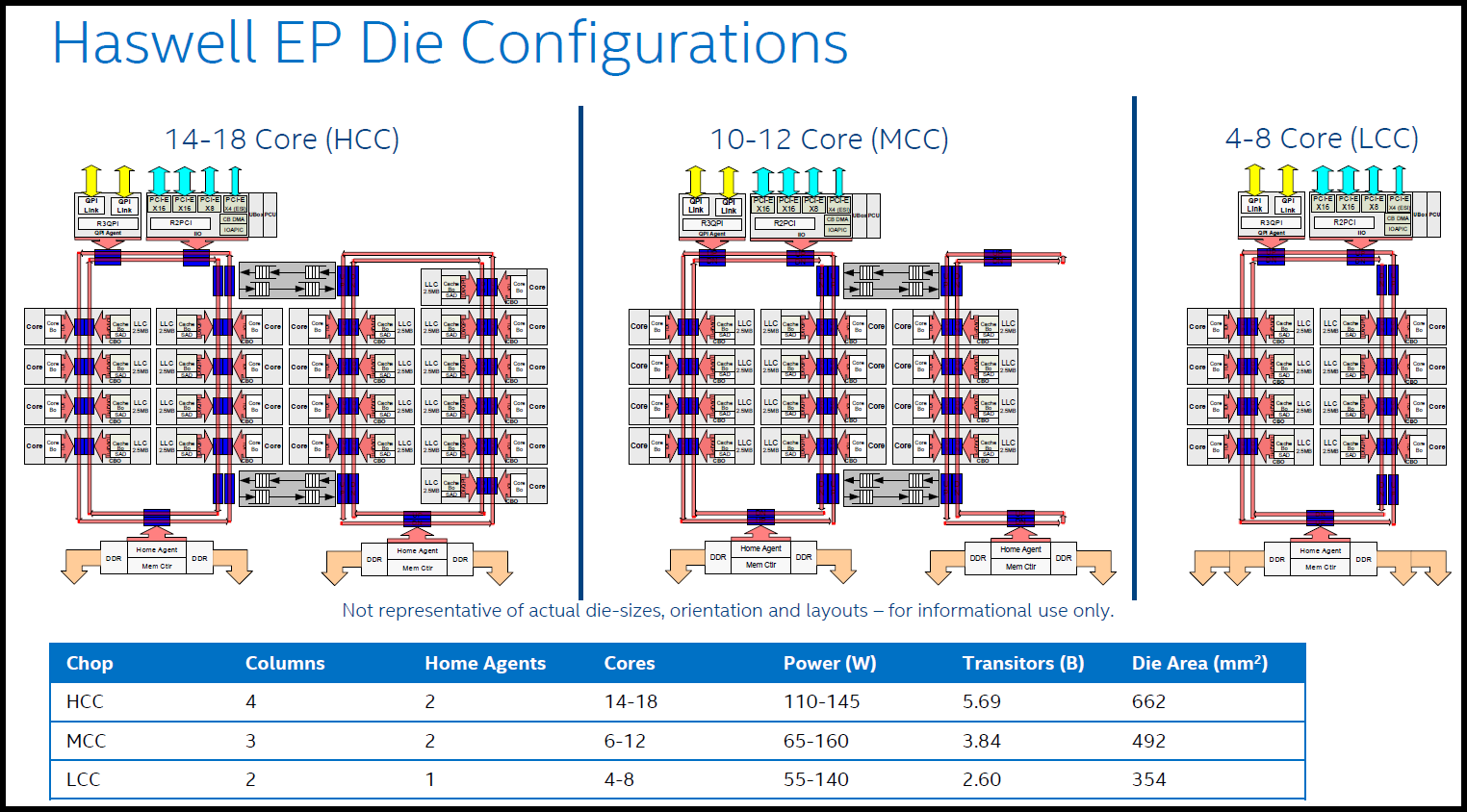

Xeon E5-2600 是采用 RingBus 最典型的 CPU. 由于 RingBus 可以方便增加 Core,但其也不能无限的增加 Core,当 Core 添加到一定数量之后,RingBus 的缺点页很快暴露出来,随着 Core 的增加,RingBus 的性能严重下降,多余 12 个 Core 之后会严重拖累系统的整体延迟,因此 RingBus 产生了很多变种,其总共有三种不同的芯片布局:

- LCC(Low Core Count): 该配置配置从四核到八核,与较低核心数的 Ivy Bridge EP 非常相似. 它有一个双环,两列核心,只有一个内存控制器. 这种芯片的最后一级缓存(LLC)较小,延迟也较低

- MCC(Middle Core Count): 该配置支持 10 到 12 核心,该芯片有两个内存控制器. 蓝点表示数据可以跳上环形总线的位置。需要注意的是,其左边一个单 RingBus,而右边则是半个 RingBus, 也就是 1.5 RingBus.

- HCC(High Core Count): 该配置支持 14 到 18 核心,该芯片有两个内存控制器. 蓝点表示数据可以跳上环形总线的位置。需要注意的是,芯片的布局也是不对称的. 例如一个 18 核的 CPU 在一侧有 8 核(4-4)和 20MB 的 LLC,另一侧则有 25MB 的 LLC 和 10 个核心. 该配置在右侧的环上减少了六到八个核心,同时也减少了相应数量的 LLC. 两个 RingBus 直接用两个双向 Pipe Line 连接,保证通讯顺畅. 由于此时 Ring0(左边的 RingBus) 访问 Ring1(右边的 RingBus) 模块的延迟明显高于本 Ring,亲和度不同,所以两个 Ring 分属于不同的 NUMA.

RingBus 是独立于核心的实体之一,它们有独立的电压和频率。因此如果进行的输入/输出或一致性消息传递比处理更多,可以动态分配功率以加速环形总线的速度. 随着摩尔定律带来的多个的晶体管,Core 数量不断的增加,单 Ring、1.5 Ring 和双 Ring 让 Core 的数量有所增加,但不能简单的通过增加 Ring 的数量来解决问题,跨 Ring 的访问会带来很大的延时. Intel 为此推出了 Mesh 内部总线.